#### TESE DE DOUTORADO

Inversores Multiníveis obtidos a partir do Empilhamento de Células de Dois Níveis

JOÃO HELDER GONZAGA MUNIZ DA SILVA

SUPRA OMNES LUX LUCE

CAMPINA GRANDE - PARAÍBA NOVEMBRO - 2016

# Inversores Multiníveis obtidos a partir do Empilhamento de Células de Dois Níveis

João Helder Gonzaga Muniz da Silva

Tese de Doutorado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Campina Grande como parte dos requisitos necessários para obtenção do grau de Doutor em Ciências, no domínio da Engenharia Elétrica.

Área de Concentração: Processamento da Energia

Prof. Edison Roberto Cabral da Silva Orientador

> Campina Grande - PB Novembro - 2016

S586i

2016 Silva, João Helder Gonzaga Muniz da,

Inversores Multiníveis obtidos a partir do Empilhamento de Células de Dois Níveis / João Helder Gonzaga Muniz da Silva. — Campina Grande, 2016.

162 f.: il. color.

Tese (Doutorado) – Universidade Federal de Campina Grande, Centro de Engenharia Elétrica e Informática.

Orientação: Prof. Dr. Edison Roberto Cabral da Silva, Prof. Dr. Euzeli Cipriano dos Santos Júnior

1. Inversores. 2. Célula de Dois Níveis. 3. Modulação de Inversores. I. Silva, Edison Roberto Cabral da. II. Santos Júnior, Euzeli Cipriano dos.

CDU - 621.314.572(043)

# "INVERSORES MULTINÍVEIS OBTIDOS A PARTIR DO EMPILHAMENTO DE CÉLULAS DE DOIS NÍVEIS"

#### JOÃO HELDER GONZAGA MUNIZ DA SILVA

TESE APROVADA EM 14/11/2016

EDISON ROBERTO CABRAL DA SILVA, Dr.Ing., UFCG Orientador(a)

EUZELI CIPRIANO DOS SANTOS JÚNIOR, D.Sc., IUPUI - USA Orientador(a)

DEMERCIL DE SOUZA OLIVEIRA JÚNIOR, Dr., UFC Examinador(a)

CASSIANO RECH, Dr., UFSM

Examinador(a)

TALVANES MENESES OLIVEIRA, D.Sc., UFCG

Examinador(a)

CURSINO BRANDÃO JACOBINA, Dr.Ing., UFCG

acoli

Examinador(a)

**CAMPINA GRANDE - PB**

Dedico este trabalho à minha esposa Renata Arnaud, aos meus filhos Tarsila e Bernardo. Ao meu Pai João Muniz, à minha mãe Auristela Muniz, às minhas irmãs Fabiana Muniz e Fernanda Muniz, aos meus avós Antonio Gonzaga, Maria Albuquerque (in memorian), Silvino Muniz (in memorian) e Severina Muniz(in memorian), a todos os meus tios, primos e demais parentes e amigos.

# Agradecimentos

Agradeço a Deus pela minha existência, por ter me proporcionado várias oportunidades e por estar sempre presente em minha vida.

Agradeço a minha querida esposa Renata Arnaud por todo carinho, dedicação e suporte. Aos meus pais João Muniz e Auristela pelo suporte e ensinamentos ao longo da vida. Aos meus sogros Francisco Arnaud e Elza Arnaud pelas valorosas ajudas. A Maria Letícia e Isabel Muniz que tiveram valiosa participação na minha formação.

A Euzeli Cipriano dos Santos Júnior pelas enormes contribuições e por ser um exemplo de dedicação naquilo que faz.

Um agradecimento especial ao professor Edison Roberto Cabral, cuja orientação foi muito além do escopo desse trabalho.

Aos professores Cursino Brandão, Talvanes Meneses Oliveira, Cassiano Rech e Demercil de Souza Oliveira pelas colaborações que engrandeceram este trabalho.

Aos amigos que tenho muita estima: Luciano Barros, Wellington de Sousa Lima, Alvaro de Medeiros Maciel, Abinadabe Silva Andrade, Antônio Isaac, Luis Gustavo Guedes Pereira Castro, Antonio de Paula Dias Queiroz, Edgar Luiz, Bruno Emanuel, Ítalo Roger e demais amigos de LEIAM.

Ao CNPQ pelo suporte financeiro que permitiu a realização deste trabalho.

## Resumo

Os inversores multiníveis foram introduzidos como uma alternativa para o aumento da qualidade e da eficiência dos sistemas alimentados por inversores. Dependendo do nível de tensão c.c. do barramento aplicado ao inversor, pode ser inevitável a utilização de topologias multi-níveis. Estas topologias possibilitam a redução da tensão sobre cada um destes dispositivos. Contudo, uma quantidade maior de interruptores não só aumenta o custo final do inversor, como também requer o uso de estratégias mais complexas de modulação e controle. Ainda, alguns pontos inerentes aos inversores multiníveis como: redução da tensão de modo-comum, tolerância à faltas e desbalanceamento das tensões dos capacitores, entre outros, precisam ser investigados. Neste cenário, são de muito interesse os estudos de novas topologias multiníveis, além de novas técnicas de modulação simplificadas.

Neste trabalho serão estudados inversores multiníveis com diferentes princípios de operação, abordando topologias híbridas formadas pelo empilhamento de células dois níveis. A primeira delas, consiste de um inversor monofásico de quatro níveis em ponte. Este inversor é composto de um braço de dois níveis e um braço de três níveis apresentando mesma tensão de bloqueio para todas as chaves. Na segunda topologia, os pontos centrais de cada um dos braços são conectados ao mesmo ponto, com o braço externo envolvendo o interno, representando uma estrutura pouco investigada. Esta topologia necessita de chaves bidirecionais para tornar possível seu correto funcionamento. É feito ainda um estudo de um inversor de 2/3 níveis, onde é proposto um algoritmo de modulação simplificado, onde consegue-se uma significativa redução no número de operações realizados. Por fim, é estudado um inversor multinível simétrico híbrido baseado nas topologias meia-ponte e ANPC, onde são propostas duas alterações na topologia que juntamente com a modificação do padrão de chaveamento, fornece um melhor controle no balanceamento das tensões dos capacitores, além de reduzir a quantidade de fontes c.c. utilizadas pelo mesmo.

<u>Resumo</u> vii

Palavras-chave: inversores, células de dois níveis, modulação de inversores.

## Abstract

Multilevel inverters are an alternative for both quality and efficiency increase of inverter fed systems. Depending on the voltage level c.c. of the bus applied to the inverter, the usage of multilevel topologies is inevitable. Those topologies reduce the voltage over each of those devices. However, a higher quantity of switches increases the inverters final cost, and requires more complex approaches for control and modulation. Also, few inherent aspects of the multilevel inverters including: reduction of the common-mode voltage, fault tolerance and unbalance capacitors voltages, among other, need to be investigated. In this scenario, new multilevel topologies have great interest, also with new and simplified modulation techniques.

In this work we study multilevel inverter with different operational principles, formed by formed by stacking two levels cells. The first one, consist of a single-phase inverter with a four level bridge. This inverter is composed of a two level leg and a three level leg, presenting the same blocking voltage for all the switches. In the second topology, every central point of each of the leg is connected into a common single point, with the extern leg over the intern one, a structure poorly studied. This topology needs bidirectional switches for a correct well function. A study of the 2/3 level inverter is done, in which a significant reduction of the operation numbers is achieved. Finally, a hybrid symmetric multilevel inverter is studied based on both half-bridge and ANPC topologies, in which two changes in the topology are proposed alongside with some changes in the switching standard. This provides a better control in the capacitors voltage balance, and reduces the amount of sources c.c. used by them.

**Keywords:** inverters, two-level cells, modulation inverters.

# Índice

| A                         | grade                 | ecimentos                                               |

|---------------------------|-----------------------|---------------------------------------------------------|

| $\mathbf{R}_{\mathbf{c}}$ | esum                  | o                                                       |

| A۱                        | ostra                 | <b>ct</b>                                               |

| Ín                        | $\operatorname{dice}$ |                                                         |

| Ín                        | ${f dice}$            | de Tabelas                                              |

| Ín                        | $\operatorname{dice}$ | de Figuras                                              |

| Li                        | sta d                 | e Símbolos                                              |

| 1                         | Inti                  | rodução Geral                                           |

|                           | 1.1                   | Localização do Tema                                     |

|                           | 1.2                   | Revisão Bibliográfica                                   |

|                           |                       | 1.2.1 Inversores Multiníveis                            |

|                           |                       | 1.2.2 Técnicas de Modulação para Inversores Multiníveis |

|                           | 1.3                   | Empilhamento de Células Dois Níveis                     |

|                           | 1.4                   | Justificativa e Contribuições do Trabalho               |

|                           | 1.5                   | Organização do Trabalho                                 |

|                           | 1.6                   | Produção Gerada                                         |

| <b>2</b>                  | Inv                   | ersor <b>2L3L</b>                                       |

|                           | 2.1                   | Introdução                                              |

|                           | 2.2                   | Operação do Inversor 2L3L                               |

|                           | 2.3                   | Estratégia de Modulação                                 |

<u>Índice</u> x

|   | 2.4               | Balanceamento das Tensões dos Capacitores                        | 42                              |

|---|-------------------|------------------------------------------------------------------|---------------------------------|

|   | 2.5               | Comparação Geral                                                 | 44                              |

|   |                   | 2.5.1 Número de Dispositivos                                     | 45                              |

|   |                   | 2.5.2 Distorção Harmônica da Tensão de Carga                     | 45                              |

|   |                   | 2.5.3 Correntes nos Capacitores do Barramento                    | 46                              |

|   |                   | 2.5.4 Perdas                                                     | 46                              |

|   | 2.6               | Inversor 2L3L com Número de Fontes Reduzido                      | 48                              |

|   | 2.7               | Resultados de Simulação                                          | 49                              |

|   | 2.8               | Resultados Experimentais                                         | 51                              |

|   | 2.9               | Conclusões                                                       | 52                              |

| 3 | Cor               | Sannaçãos Multinánia Nostad                                      | E 4                             |

| 3 |                   | 9                                                                | 54                              |

|   | 3.1               |                                                                  | 54                              |

|   | 3.3               |                                                                  | <ul><li>55</li><li>58</li></ul> |

|   | ა.ა               |                                                                  |                                 |

|   |                   |                                                                  | 58                              |

|   | 3.4               | 9                                                                | <ul><li>62</li><li>63</li></ul> |

|   | $\frac{3.4}{3.5}$ |                                                                  | 64                              |

|   |                   |                                                                  |                                 |

|   | 3.6<br>3.7        |                                                                  | 69                              |

|   |                   |                                                                  | <ul><li>72</li><li>73</li></ul> |

|   |                   | -                                                                |                                 |

|   | 3.9               | 1                                                                | 74                              |

|   | 3.10              | Conclusões                                                       | 74                              |

| 4 | Est               | ratégia de Modulação Simplificada para o Conversor Híbrido $2/3$ |                                 |

|   | Nív               | eis                                                              | 82                              |

|   | 4.1               | Introdução                                                       | 82                              |

|   | 4.2               | Operação do inversor 2/3 Níveis                                  | 83                              |

|   | 4.3               | Estratégia de modulação                                          | 86                              |

|   | 4.4               | Estratégia de modulação Proposta                                 | 93                              |

|   | 4.5               | Conversor híbrido $2/3$ níveis utilizando célula NPC             | 98                              |

|   | 4.6               | Estudo de perdas nos semicondutores                              | 99                              |

|   |                   |                                                                  |                                 |

<u>Índice</u> xi

|    | 4.7   | THD e WTHD                                                                    | 101     |

|----|-------|-------------------------------------------------------------------------------|---------|

|    | 4.8   | Resultados de Simulações                                                      | 103     |

|    | 4.9   | Resultados Experimentais                                                      | 103     |

|    | 4.10  | Conclusões                                                                    | 106     |

| 5  | Inv   | ersores Híbridos de Cinco Níveis baseados nas Topologias Meia-                |         |

|    | Por   | nte e ANPC                                                                    | 108     |

|    | 5.1   | Introdução                                                                    | 108     |

|    | 5.2   | Inversor Híbrido Simétrico de Cinco Níveis baseado nas Topologias Meia-       |         |

|    |       | ponte e ANPC                                                                  | 109     |

|    |       | 5.2.1 Modos de operação                                                       | 110     |

|    |       | 5.2.2 Análise Quantitativa                                                    | 115     |

|    | 5.3   | Inversor Híbrido de Cinco Níveis baseado nas Topologias Meia-Ponte e ANPC/Ca  | pacitor |

|    |       | Flutuante                                                                     | 117     |

|    |       | 5.3.1 Modos de operação                                                       | 117     |

|    |       | 5.3.2 Análise Quantitativa                                                    | 121     |

|    | 5.4   | Inversor Híbrido de Cinco Níveis baseado nas Topologias Meia-Ponte e ANPC/For | nte     |

|    |       | Flutuante                                                                     | 127     |

|    |       | 5.4.1 Modos de Operação                                                       | 128     |

|    |       | 5.4.2 Análise Quantitativa                                                    | 129     |

|    | 5.5   | Estratégia PWM                                                                | 131     |

|    | 5.6   | Características Gerais                                                        | 133     |

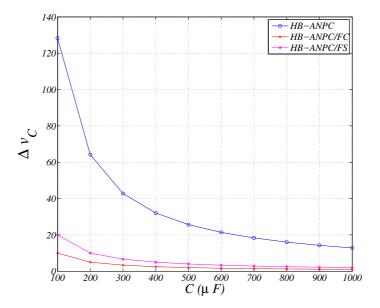

|    |       | 5.6.1 Oscilação das tensões dos capacitores                                   | 133     |

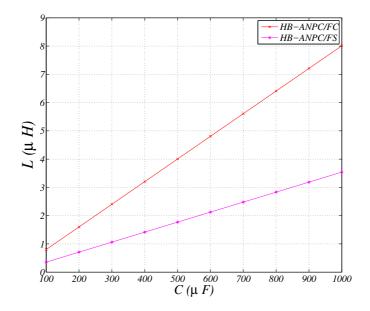

|    |       | 5.6.2 Seleção da indutância auxiliar                                          | 134     |

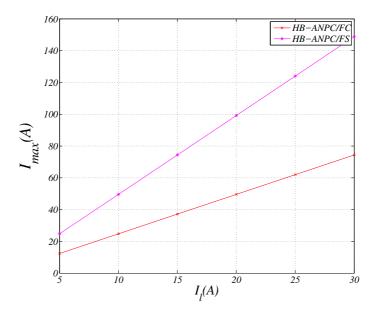

|    |       | 5.6.3 Corrente máxima nas chaves                                              | 135     |

|    |       | 5.6.4 Perdas                                                                  | 137     |

|    | 5.7   | Resultados de simulações                                                      | 140     |

|    | 5.8   | Resultados Experimentais                                                      | 140     |

|    | 5.9   | Conclusões                                                                    | 142     |

| 6  | Cor   | nclusões e Trabalhos Futuros                                                  | 147     |

| Re | eferê | ncias Bibliográficas                                                          | 151     |

# Índice de Tabelas

| 2.1 | Tensão de saída considerando todos os estados de chaveamento possíveis    .  . | 42  |

|-----|--------------------------------------------------------------------------------|-----|

| 2.2 | Perdas do inversor NPC de quatro níveis                                        | 47  |

| 2.3 | Perdas do inversor 2L3L                                                        | 47  |

| 2.4 | Comparação entre o inversor NPC 4N e o inversor 2L3L                           | 48  |

| 2.5 | Parâmetros utilizados na simulação do inversor 2L3L                            | 49  |

| 3.1 | Tensão de pólo considerando todos os estados de chaveamento                    | 57  |

| 3.2 | Tensão de bloqueio e corrente nas chaves da topologia Nested de quatro níveis. | 66  |

| 3.3 | Tensão de bloqueio e corrente nas chaves da topologia Nested de cinco níveis.  | 66  |

| 3.4 | Perdas do inversor NPC de quatro níveis                                        | 70  |

| 3.5 | Perdas do inversor Nested de quatro níveis                                     | 70  |

| 3.6 | Perdas do inversor NPC de quatro níveis operando sob condição nominal          |     |

|     | 1200V/50A                                                                      | 71  |

| 3.7 | Perdas do inversor Nested de quatro níveis operando sob condição nominal       |     |

|     | 1200V/50A                                                                      | 71  |

| 3.8 | Comparação entre conversores de quatro níveis                                  | 73  |

| 3.9 | Parâmetros utilizados na simulação do inversor Nested                          | 74  |

| 4.1 | Parâmetros utilizados na simulação do inversor 2/3 níveis                      | 103 |

| 5.1 | Possíveis estados de comutação                                                 | 113 |

| 5.2 | Estados de comutação utilizados na lógica de acionamento                       | 114 |

| 5.3 | Estados de comutação utilizados na lógica de acionamento do inversor HB-       |     |

|     | ANPC/FC                                                                        | 119 |

| 5.4 | Comparação entre os conversores de cinco níveis                                | 139 |

| 5.5 | Parâmetros utilizados na simulação dos conversores de cinco níveis             | 140 |

# Índice de Figuras

| 1.1  | Processador de Potência (Conversor Estático)                                | 2  |

|------|-----------------------------------------------------------------------------|----|

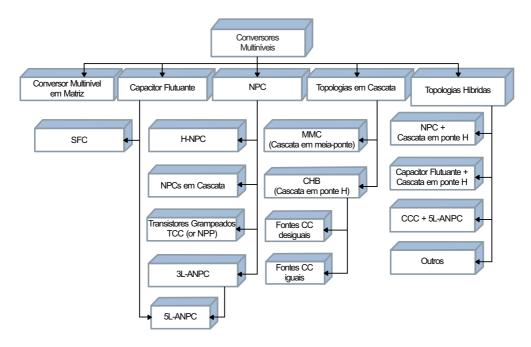

| 1.2  | Classificação de Kouro et al. (2010) modificada                             | 4  |

| 1.3  | Topologia de cinco níveis em Cascata                                        | 7  |

| 1.4  | Inversores NPC tipo I e II (ou T): (a) braço de inversor NPC de três níveis |    |

|      | tipo I; (b) braço de inversor NPC de três níveis tipo II                    | 8  |

| 1.5  | Inversores multiníveis Bhagwat e NPC: (a) Braço de inversor de Bhagwat de   |    |

|      | sete níveis; (b) Braço de inversor NPC de cinco níveis.                     | 8  |

| 1.6  | Braço de um inversor FC de três níveis                                      | 9  |

| 1.7  | Braço de um inversor com grampeamento por diodos                            | 10 |

| 1.8  | Braço de um inversor ANPC: (a) ANPC de três níveis; (b) ANPC de cinco       |    |

|      | níveis                                                                      | 10 |

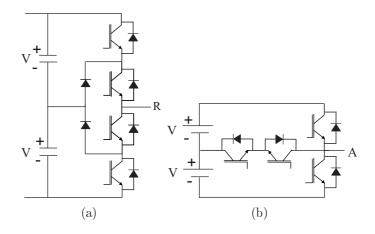

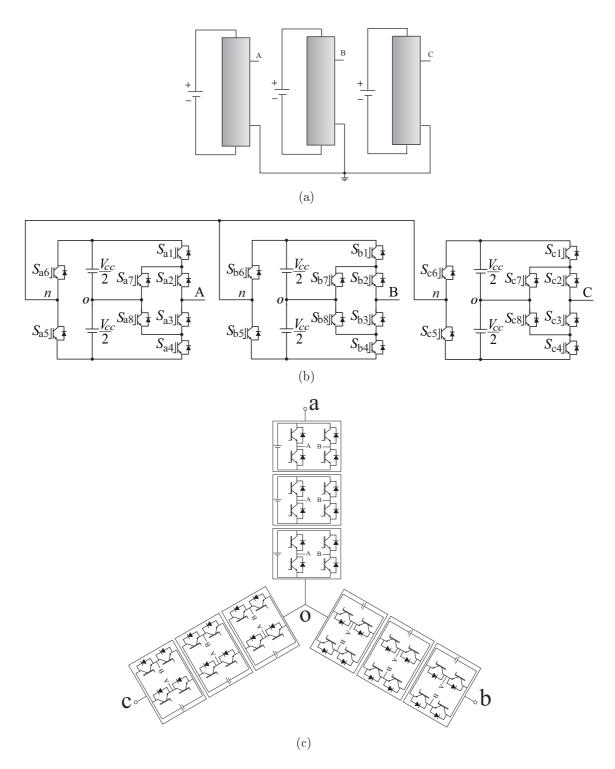

| 1.9  | Inversores em cascata: (a) utilizando meia-ponte; (b) utilizando meia-ponte |    |

|      | mista; (c) formando um braço de inversor; (d) simetricamente conectados em  |    |

|      | relação a um ponto central                                                  | 11 |

| 1.10 | Braço de um inversor híbrido NPC/FC de três níveis                          | 12 |

| 1.11 | Generalização do braço de um inversor ANPC/FC                               | 12 |

| 1.12 | Braço de um inversor ANPC/FC de cinco níveis com redução de componentes.    | 13 |

| 1.13 | Ponte inversora NPC                                                         | 14 |

| 1.14 | Ponte inversora FC                                                          | 14 |

| 1.15 | Ponte inversora NPC/FC                                                      | 14 |

| 1.16 | Ponte inversora ANPC/FC                                                     | 15 |

| 1.17 | Ponte inversora NPC/meia-ponte                                              | 15 |

| 1.18 | Ponte inversora ANPC/meia-ponte                                             | 15 |

| 1.19 | Inversor multinível de cinco níveis                                         | 16 |

| 1.20 | Inversor híbrido com número reduzido de componentes                         | 16 |

Índice de Figuras xiv

| 1.21 | Inversor multinível híbrido simétrico                                              | 16 |

|------|------------------------------------------------------------------------------------|----|

| 1.22 | Ponte inversora com uma fonte $c.c.$ comum: (a) Diagrama de blocos; (b)            |    |

|      | Topologia de três níveis para conversores de potência de baixa tensão              | 17 |

| 1.23 | Inversores formado por braços conectados em estrela: (a) Diagrama de blocos;       |    |

|      | (b) Inversor trifásico meia-ponte/ANPC; (c) braço formado por pontes em            |    |

|      | cascata.                                                                           | 18 |

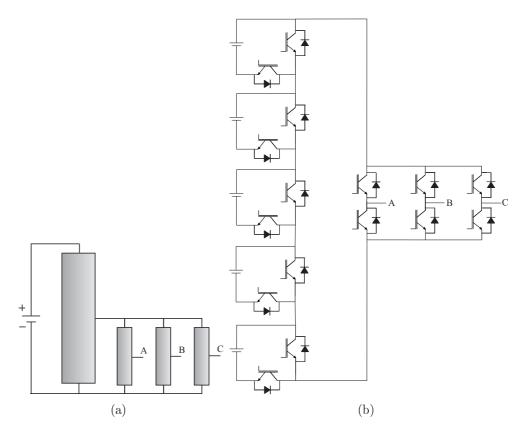

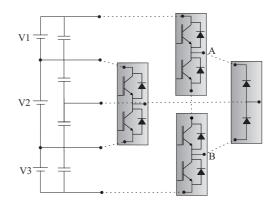

| 1.24 | Fonte multinível alimentando um inversor convencional: (a) Diagrama de blo-        |    |

|      | cos; (b) Inversor com fonte Multinível                                             | 19 |

| 1.25 | Inversores trifásicos com um dos braços de nível maior: (a) Diagrama de            |    |

|      | blocos; (b) Inversor Híbrido de 2/3 níveis.                                        | 20 |

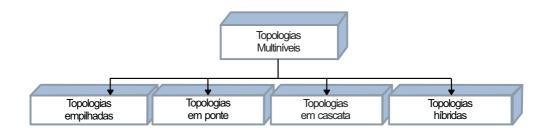

| 1.26 | Classificação de Kouro et al. (2010)                                               | 25 |

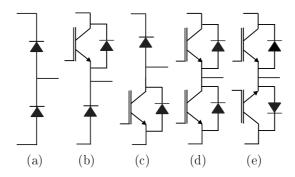

| 1.27 | Células de dois níveis: (a) célula c.c.; (b) célula c.c. positiva; (c) célula c.c. |    |

|      | negativa; (d) célula c.a.; (e) célula bidirecional                                 | 26 |

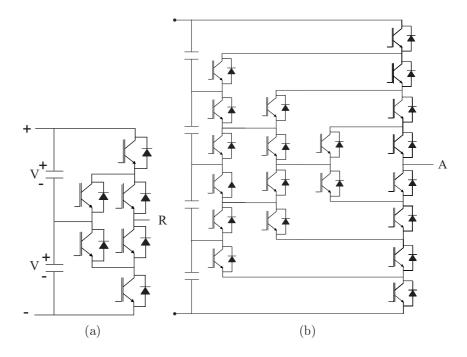

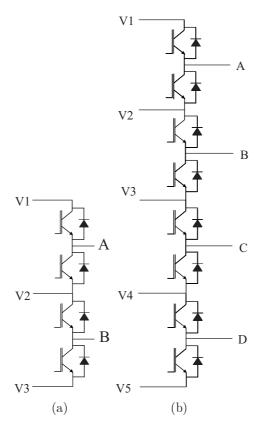

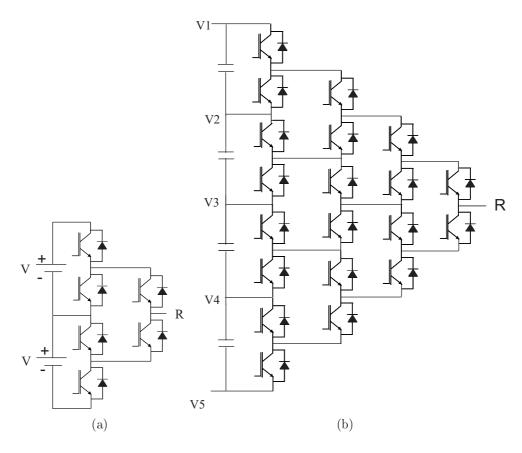

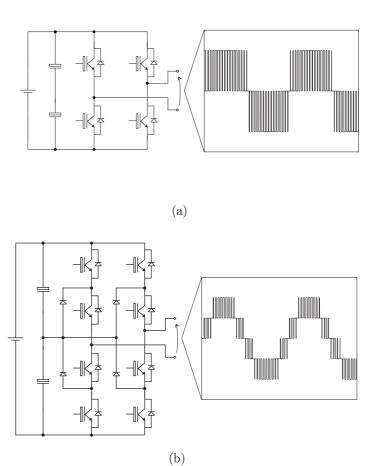

| 1.28 | Empilhamento de células $c.a.$ : (a) empilhamento de duas células; (b) empi-       |    |

|      | lhamento de quatro células para geração de mais níveis                             | 28 |

| 1.29 | Empilhamento de duas células c.c. do tipo positivo e negativo                      | 28 |

| 1.30 | Topologia FC obtidas pelo empilhamento de células $c.a.$ : (a) braço FC; (b)       |    |

|      | generalização do FC                                                                | 29 |

| 1.31 | Topologia ANPC obtidas pelo empilhamento de células $c.a.$ : (a) braço ANPC;       |    |

|      | (b) generalização do ANPC                                                          | 30 |

| 1.32 | Braço de inversor ANPC/FC                                                          | 30 |

| 1.33 | Inversor NPC/FC de cinco níveis                                                    | 31 |

| 1.34 | Topologia Nested: (a) Inversor NPC tipo II; (b) Nested de cinco níveis             | 31 |

| 1.35 | Pontes híbridas: (a) simétrica; (b) assimétrica                                    | 32 |

| 1.36 | Classificação de topologias multiníveis fonte de tensão                            | 32 |

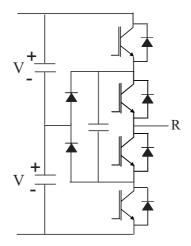

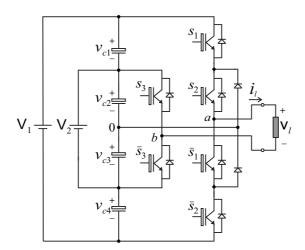

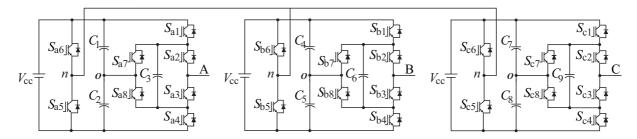

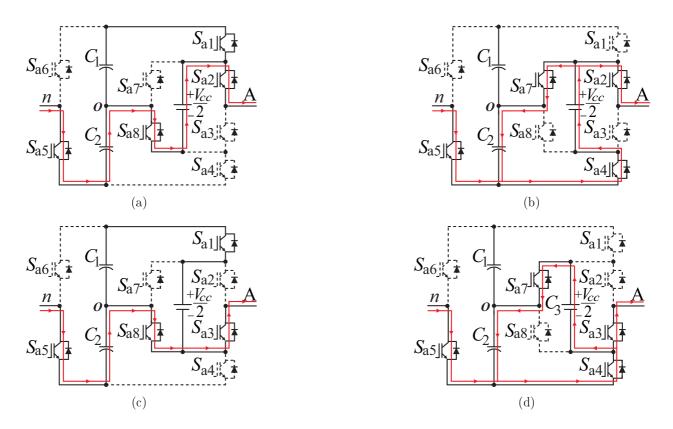

| 2.1  | Formação do inversor 2L3L                                                          | 39 |

| 2.2  | Topologia em ponte H 2L3L                                                          | 39 |

| 2.3  | Configuração convencional e forma de onda da tensão de saída (a) topologia         |    |

|      | em ponte H com quatro chaves de três níveis (b) topologia em ponte H com           |    |

|      | oito chaves de cinco níveis                                                        | 40 |

Índice de Figuras xv

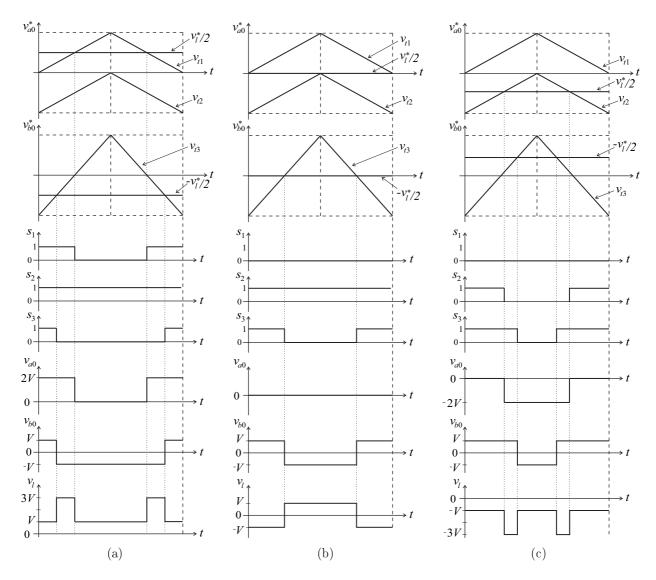

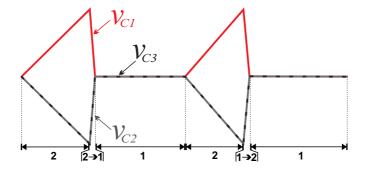

| 2.4  | Formas de ondas da modulação seno-triângulo para (a) $v_l^*/2 > 0$ (b) $v_l^*/2 = 0$ |    |

|------|--------------------------------------------------------------------------------------|----|

|      | (c) $v_l^*/2 < 0$                                                                    | 43 |

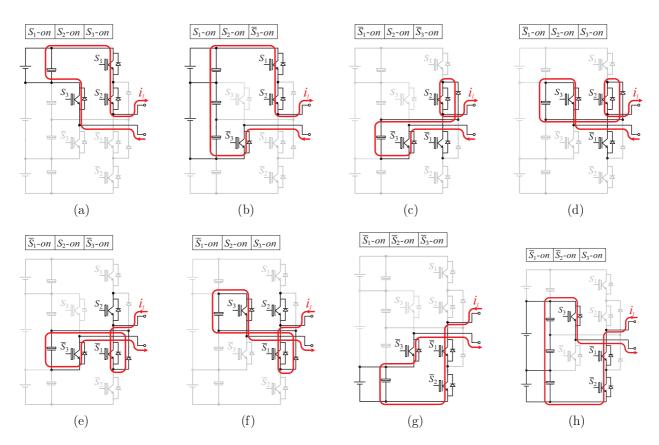

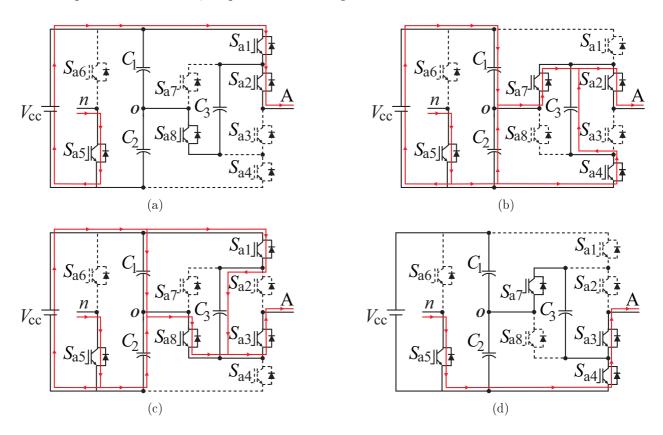

| 2.5  | Caminho da corrente nos capacitores considerando todos os estados de cha-            |    |

|      | veamento: (a)-(d) para $i_l > 0$ e (e)-(h) para $i_l < 0$                            | 44 |

| 2.6  | Configuração NPC de quatro níveis convencional                                       | 45 |

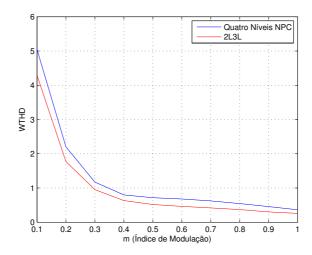

| 2.7  | WTHD da tensão de carga em função do índice de modulação obtida por                  |    |

|      | simulação                                                                            | 46 |

| 2.8  | Inversor 2L3L com duas fontes de alimentação                                         | 48 |

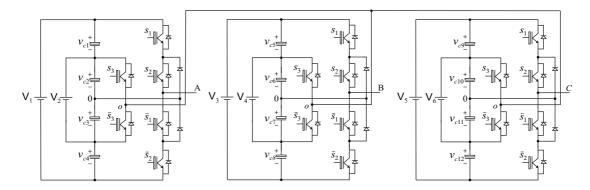

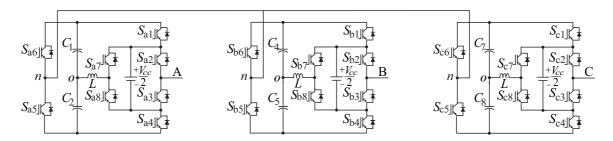

| 2.9  | Inversor 2L3L trifásico                                                              | 49 |

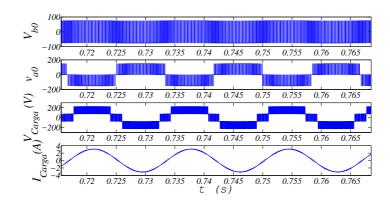

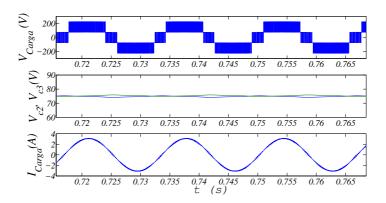

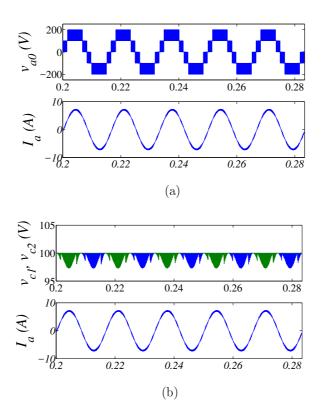

| 2.10 | Resultados de simulação (de cima para baixo) tensão de polo no braço dois            |    |

|      | níveis, tensão de polo no braço três níveis, tensão de carga e corrente de carga     | 50 |

| 2.11 | Resultados de simulação (de cima para baixo) tensão de carga, tensões nos            |    |

|      | capacitores $v_{c2}$ e $v_{c3}$ e corrente de carga                                  | 50 |

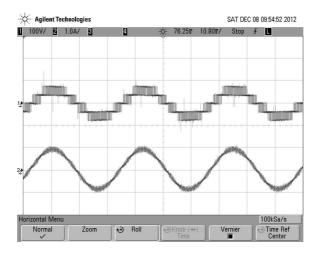

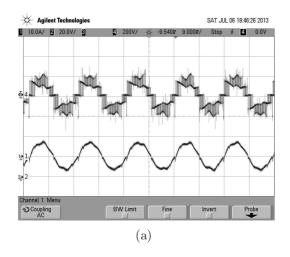

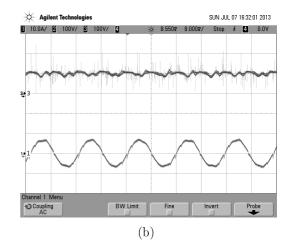

| 2.12 | Resultados Experimentais (de cima para baixo) tensão de polo no braço dois           |    |

|      | níveis, tensão de pólo no braço três níveis, tensão de carga e corrente de carga     | 51 |

| 2.13 | Resultados Experimentais (de cima para baixo) tensão de carga, tensões nos           |    |

|      | capacitores $v_{c2}$ e $v_{c3}$ e corrente de carga                                  | 51 |

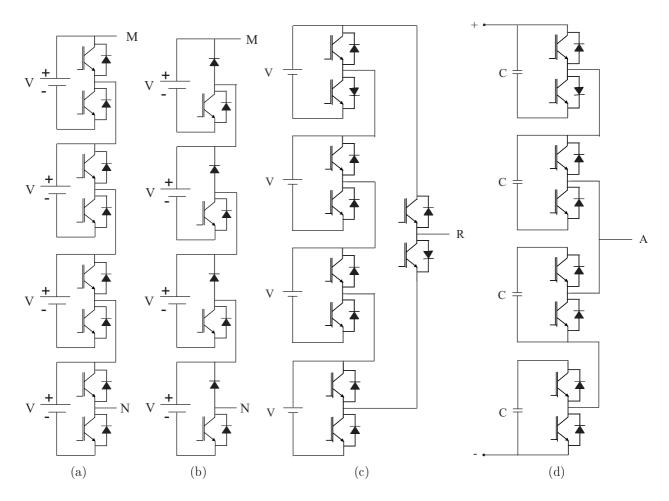

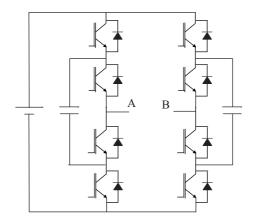

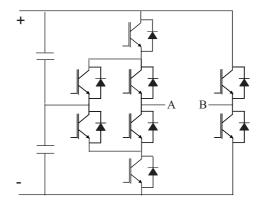

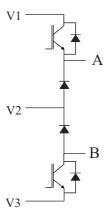

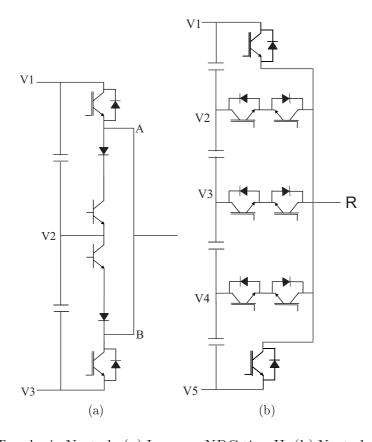

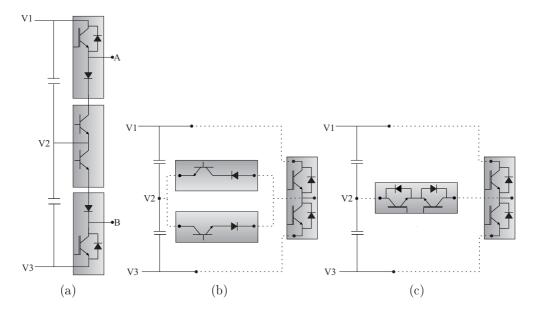

| 3.1  | Formação do Nested: (a) Empilhamento de células com diferentes dispositivos          |    |

|      | (b) formação da chave bidirecional e (c) Nested de três níveis ou NPC de três        |    |

|      | níveis do tipo II                                                                    | 55 |

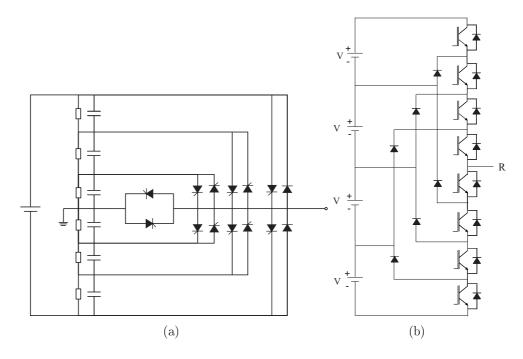

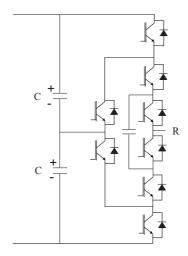

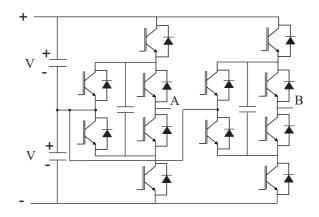

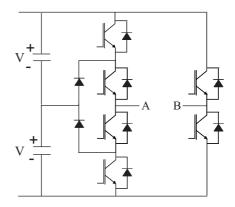

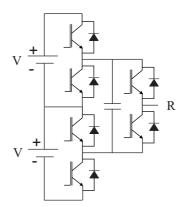

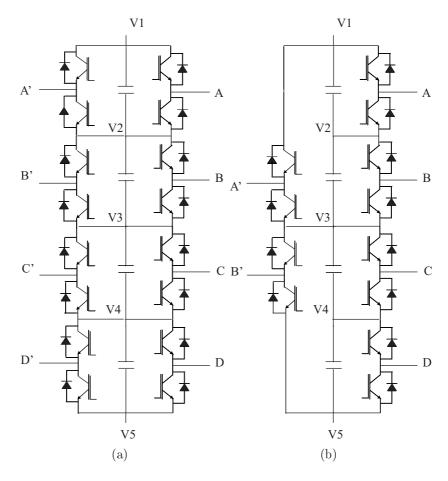

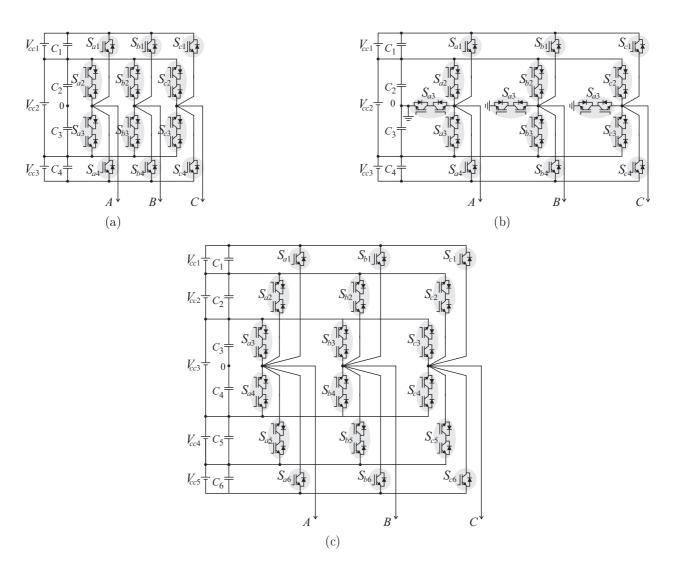

| 3.2  | Configurações Multiníveis Nested: (a) Quatro níveis (b) Cinco níveis e (c)           |    |

|      | Seis níveis                                                                          | 56 |

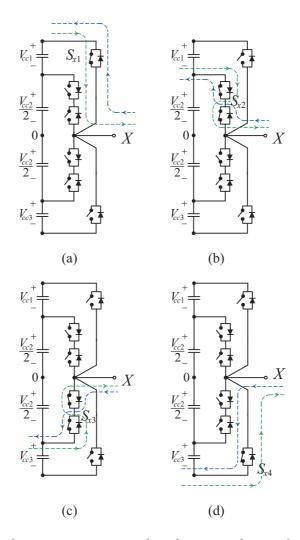

| 3.3  | Fluxo de corrente através das chaves no braço da topologia Nested                    | 58 |

| 3.4  | Fluxo de corrente através das chaves no braço da topologia NPC de quatro             |    |

|      | níveis.                                                                              | 59 |

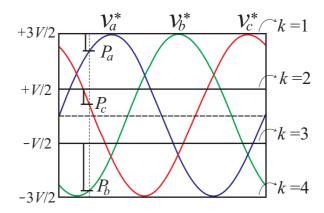

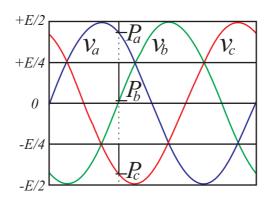

| 3.5  | Definição de $P_a, P_b$ e $P_c$ em um inversor de 4-níveis                           | 60 |

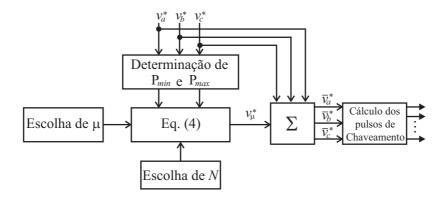

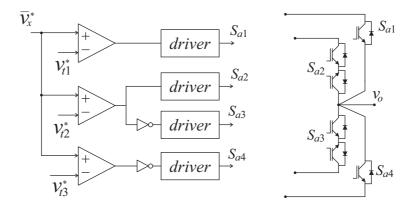

| 3.6  | Diagrama de blocos da PWM híbrida                                                    | 61 |

| 3.7  | Implementação analógica da PWM                                                       | 61 |

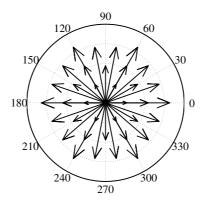

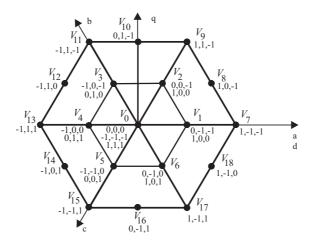

| 3.8  | Diagrama Vetorial                                                                    | 63 |

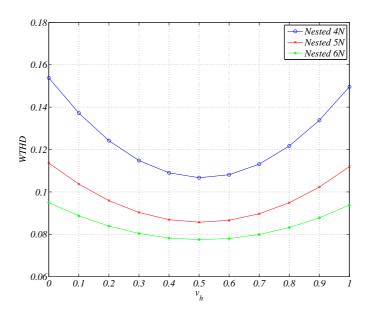

| 3.9  | WTHD da tensão de carga em função de $v_{\mu}$                                       | 64 |

Índice de Figuras xvi

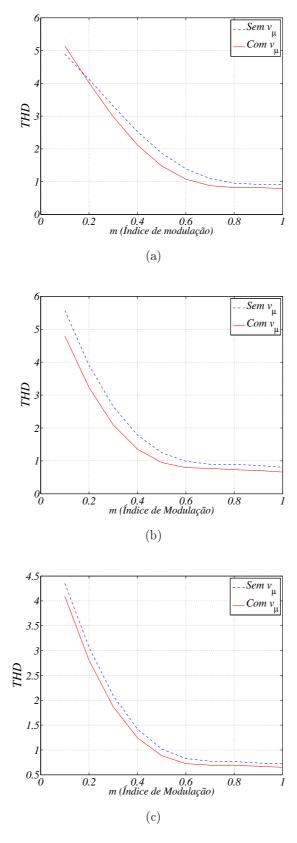

| 3.10 | THD da corrente de carga em função do índice de modulação para as confi-      |    |

|------|-------------------------------------------------------------------------------|----|

|      | gurações com (a) quatro níveis (b) cinco níveis e (c) seis níveis             | 65 |

| 3.11 | Tensões nas chaves do braço $a.$                                              | 67 |

| 3.12 | Corrente nas chaves do braço $a.$                                             | 68 |

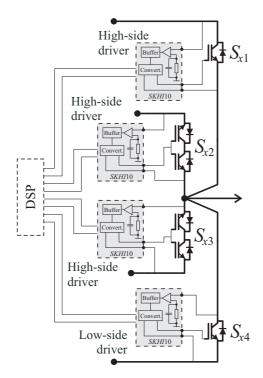

| 3.13 | Circuito de acionamento de um braço do Nested com três drivers high-side e    |    |

|      | um low-side                                                                   | 69 |

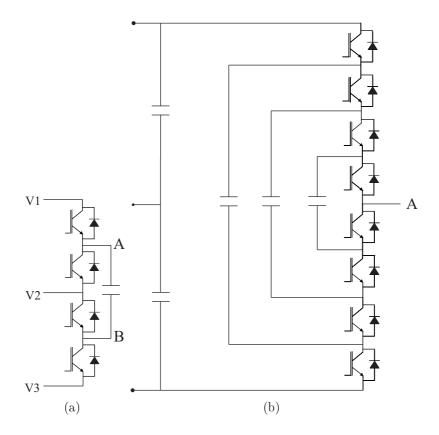

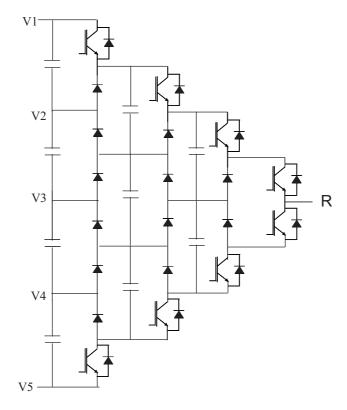

| 3.14 | Generalização da configuração Nested com número de níveis: (a) par e (b)      |    |

|      | ímpar                                                                         | 72 |

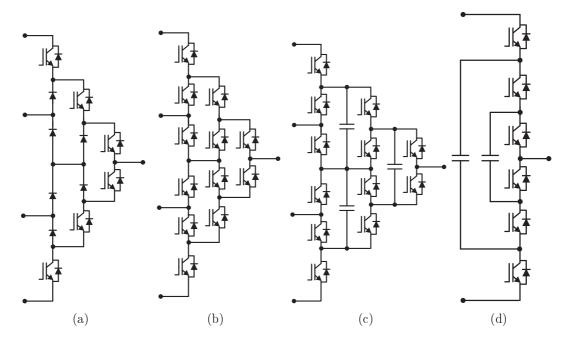

| 3.15 | Topologias propostas na literatura técnica: (a) inversor multinível com dio-  |    |

|      | dos grampeados (b) conversor NPC ativo (c) inversor de quatro níveis e (d)    |    |

|      | inversor a capacitores flutuantes                                             | 73 |

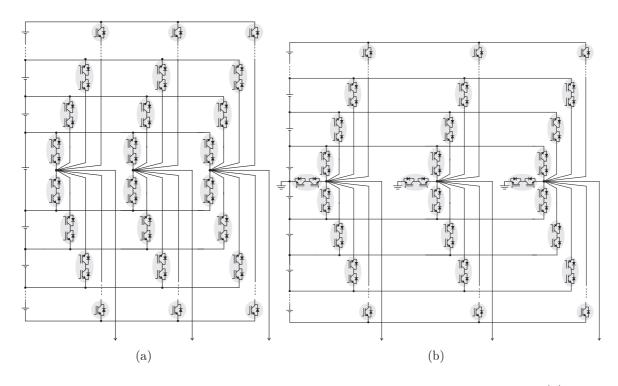

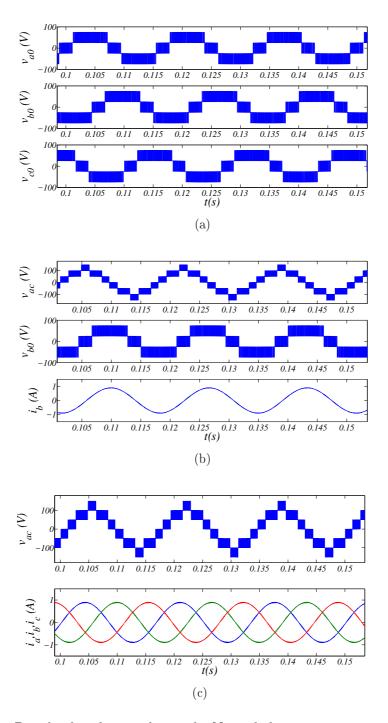

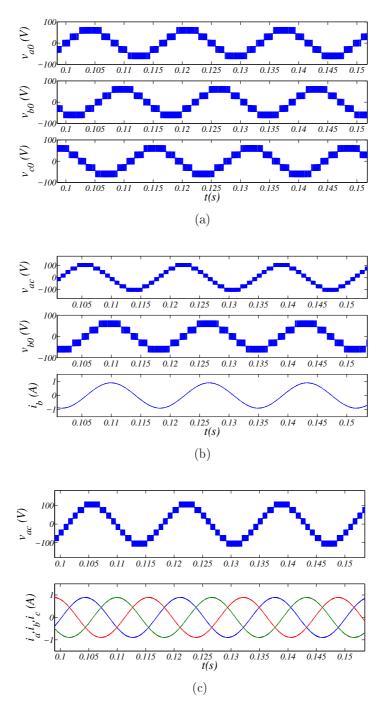

| 3.16 | Resultados de simulação do Nested de quatro níveis. (a) Tensão de polo; (b)   |    |

|      | De cima para baixo: tensão de linha, tensão de polo e corrente de fase; e (c) |    |

|      | De cima para baixo: Tensão de linha e correntes trifásicas na carga           | 75 |

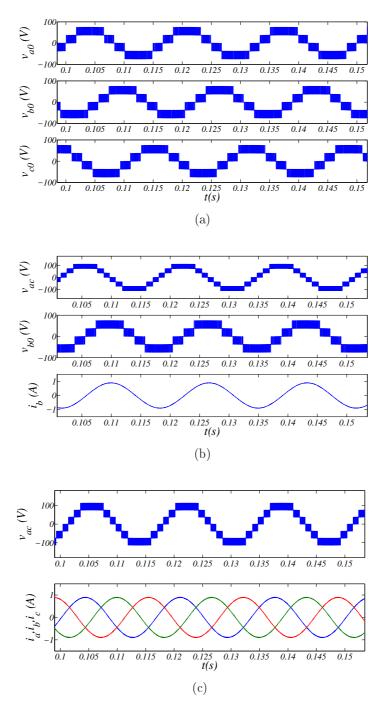

| 3.17 | Resultados de simulação do Nested de cinco níveis. (a) Tensão de polo; (b)    |    |

|      | De cima para baixo: tensão de linha, tensão de polo e corrente de fase; e (c) |    |

|      | De cima para baixo: Tensão de linha e correntes trifásicas na carga           | 76 |

| 3.18 | Resultados de simulação do Nested de seis níveis. (a) Tensão de polo; (b) De  |    |

|      | cima para baixo: tensão de linha, tensão de polo e corrente de fase; e (c) De |    |

|      | cima para baixo: Tensão de linha e correntes trifásicas na carga              | 77 |

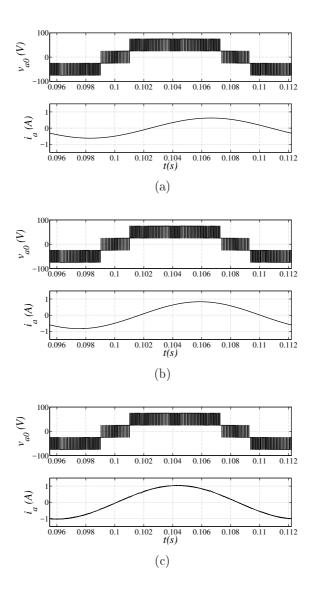

| 3.19 | Resultados de simulação do Nested de quatro níveis com fatores de potência    |    |

|      | igual a: (a) 0,6, (a) 0,8, e (a) 1,0                                          | 78 |

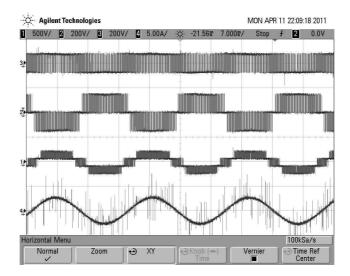

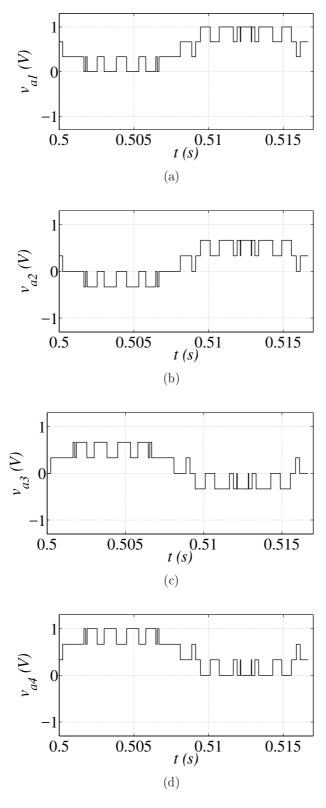

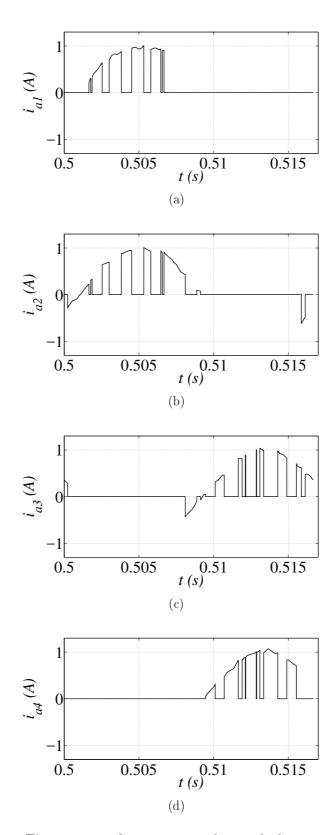

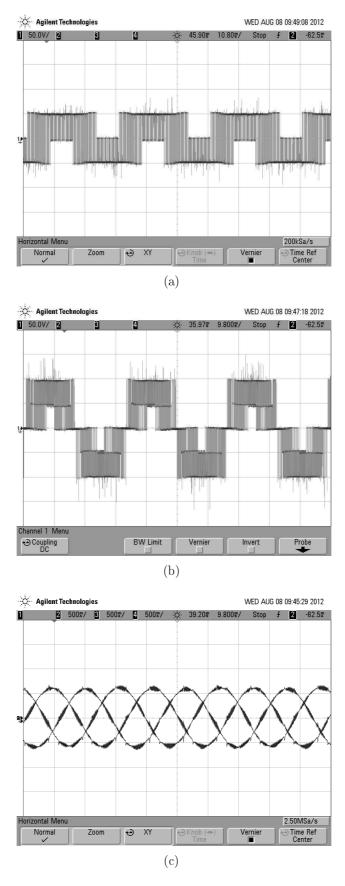

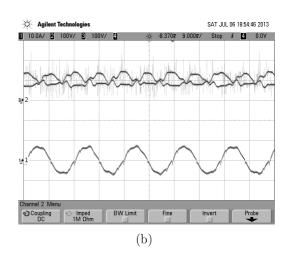

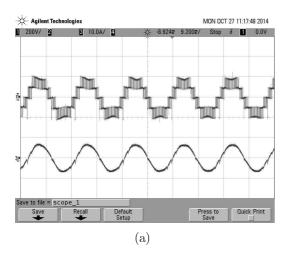

| 3.20 | Resultados experimentais do Nested de quatro níveis. (a) Tensão de polo; (b)  |    |

|      | De cima para baixo: tensão de linha, tensão de polo e corrente de fase; e (c) |    |

|      | De cima para baixo: Tensão de linha e correntes trifásicas na carga           | 79 |

| 3.21 | Resultados experimentais do Nested de cinco níveis monofásico: Tensão de      |    |

|      | polo e corrente na carga monofásica.                                          | 80 |

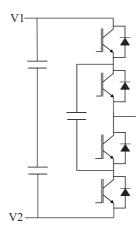

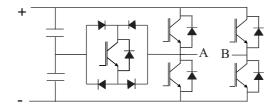

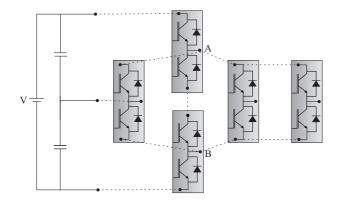

| 4.1  | Formação do inversor de $2/3$ níveis                                          | 83 |

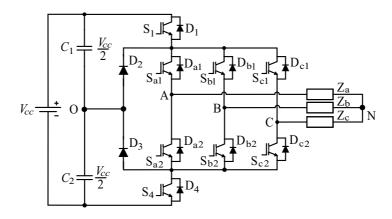

| 4.2  | Inversor Híbrido de $2/3$ níveis                                              | 83 |

| 4.3  | Aplicação do vetor 0,-1,-1                                                    | 84 |

| 4.4  | Aplicação do vetor 1,-1,-1                                                    | 85 |

Índice de Figuras xvii

| 4.5  | Aplicação do vetor 1,1,-1                                                        | 85  |

|------|----------------------------------------------------------------------------------|-----|

| 4.6  | Aplicação do vetor 1,1,0                                                         | 85  |

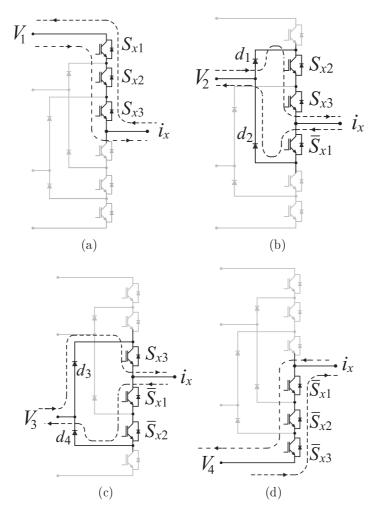

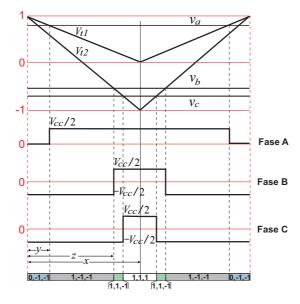

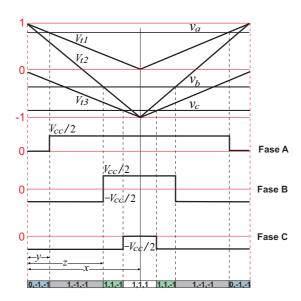

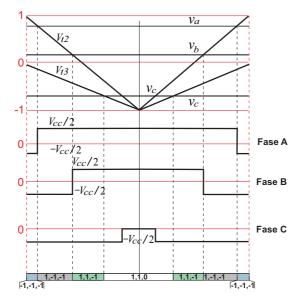

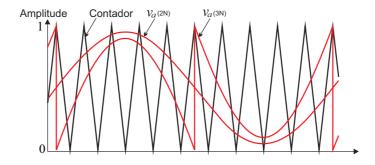

| 4.7  | Princípio da modulação por portadora do inversor 2/3 N $$                        | 86  |

| 4.8  | Pulsos da modulação proposta por (Mihalache, 2006) no intervalo $1$ do setor $1$ | 87  |

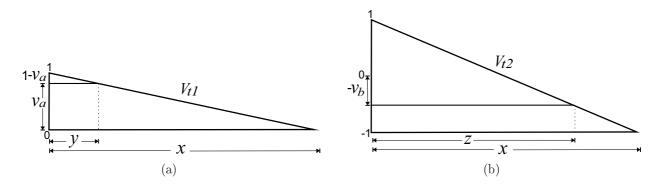

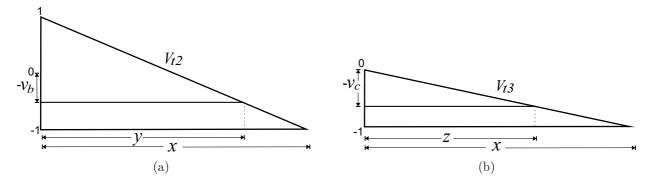

| 4.9  | Triângulos formados pelas tensões $v_a$ e $v_b$ com as portadoras                | 87  |

| 4.10 | Pulsos da modulação proposta por (Mihalache, 2006) no intervalo $2$ do setor $1$ | 88  |

| 4.11 | Triângulos formados pelas tensões $v_b$ e $v_c$ com as portadoras                | 89  |

| 4.12 | Pulsos da modulação proposta por (Mihalache, 2006) no intervalo 3 do setor $1$   | 90  |

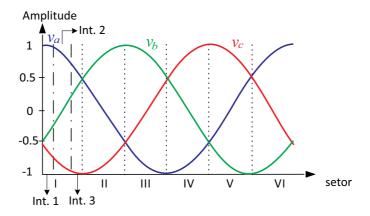

| 4.13 | Intervalos do setor 1                                                            | 91  |

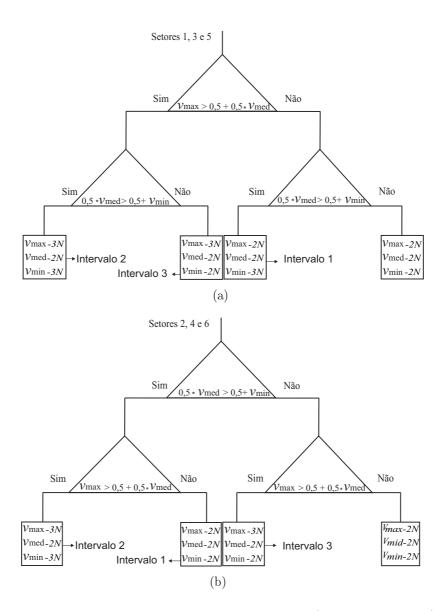

| 4.14 | Fluxograma da modulação proposta por (Mihalache, 2006): (a) para os setores      |     |

|      | 1, 3 e 5; (b) para os setores 2, 4 e 6                                           | 92  |

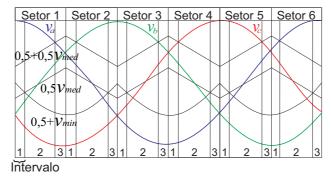

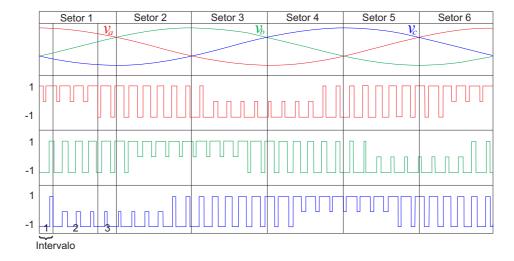

| 4.15 | Método introduzido por Mihalache, mostrando os seis setores e os dezoitos        |     |

|      | intervalos a serem determinados                                                  | 94  |

| 4.16 | Método proposto: utilizando as equações $(4.17)$ e $(4.18)$                      | 95  |

| 4.17 | Fluxograma da modulação proposta                                                 | 95  |

| 4.18 | Diagrama vetorial 2N                                                             | 96  |

| 4.19 | Diagrama vetorial 2/3N $\dots \dots \dots \dots \dots \dots \dots \dots \dots$   | 97  |

| 4.20 | Diagrama vetorial 3N                                                             | 97  |

| 4.21 | Inversor Híbrido de $2/3$ níveis                                                 | 99  |

| 4.22 | Sequências de configurações para para o intervalo 1 do Setor 1                   | 100 |

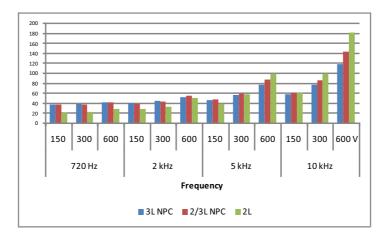

| 4.23 | Comparação de perdas totais versus frequência de chaveamento e tensão do         |     |

|      | barramento                                                                       | 101 |

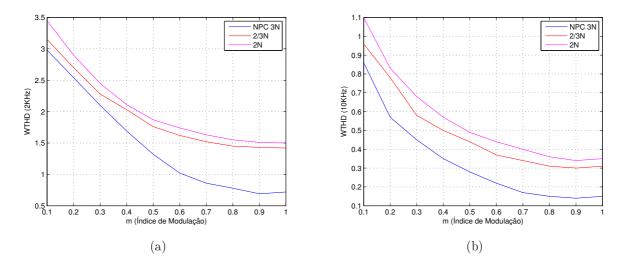

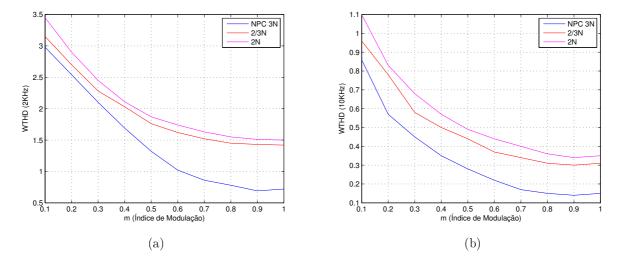

| 4.24 | WTHD: (a) $2kHz$ ; (b) $10kHz$                                                   | 102 |

| 4.25 | THD: (a) $2kHz$ ; (b) $10kHz$                                                    | 102 |

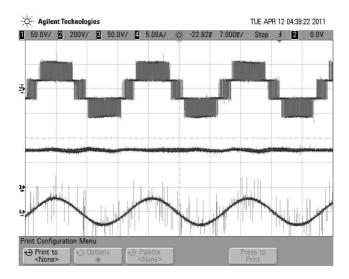

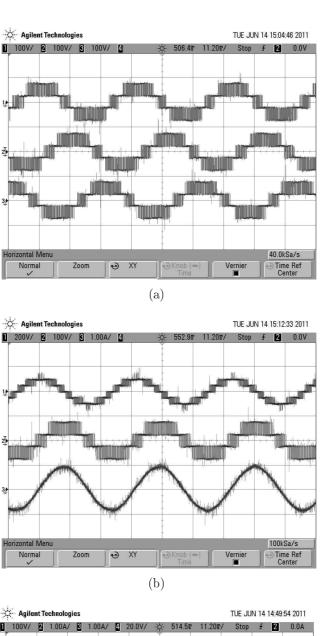

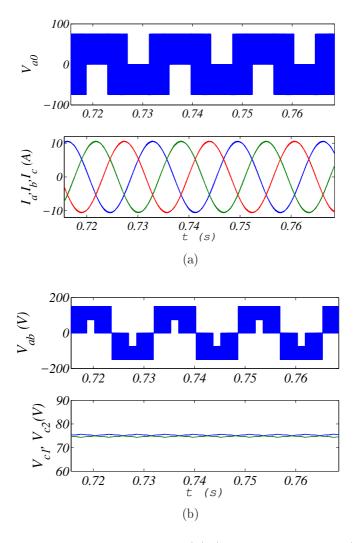

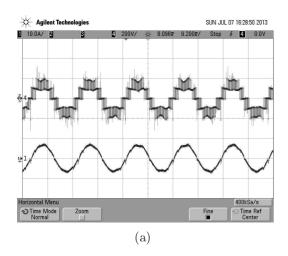

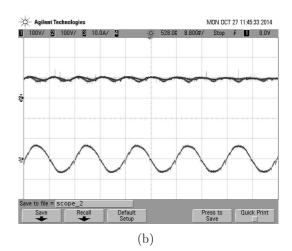

| 4.26 | Resultados de simulações. (a) (de cima para baixo) tensão de polo e correntes    |     |

|      | na carga trifásica; (b) (de cima para baixo) tensão de linha e tensões nos       |     |

|      | capacitores do barramento                                                        | 104 |

| 4.27 | Detalhes da tensão de polo                                                       | 104 |

| 4.28 | Resultados experimentais. (a) tensão de polo; (b) tensão de linha e (c) cor-     |     |

|      | rentes trifásicas                                                                | 105 |

| 4.29 | Implementação no DSP do princípio da modulação do inversor $2/3~\mathrm{N}$      | 106 |

Índice de Figuras xviii

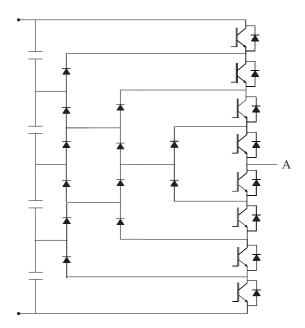

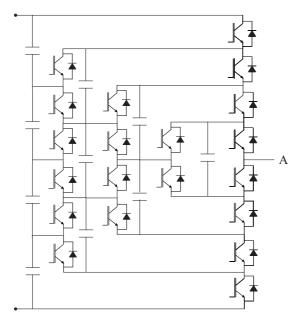

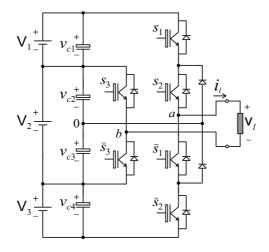

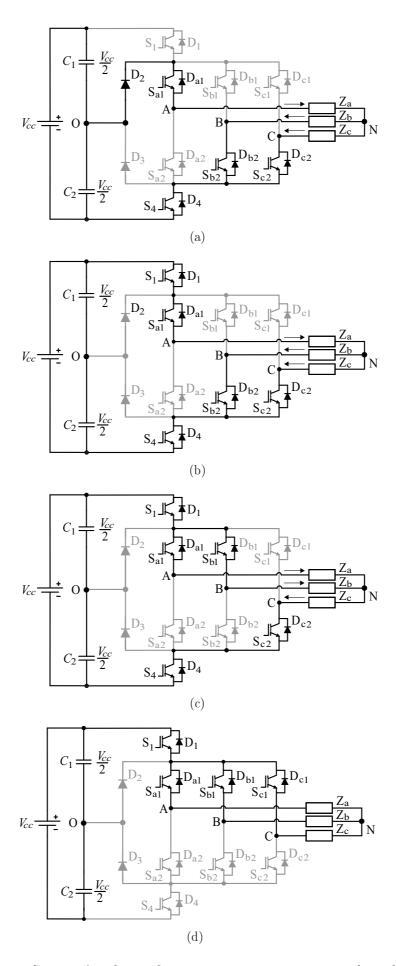

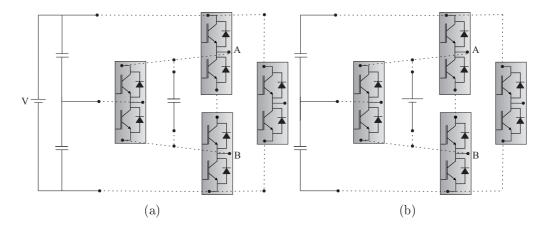

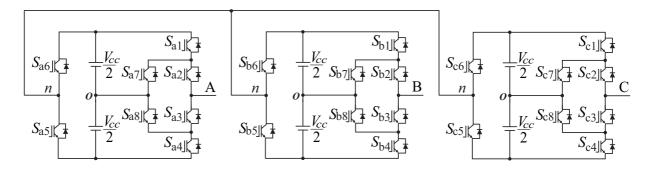

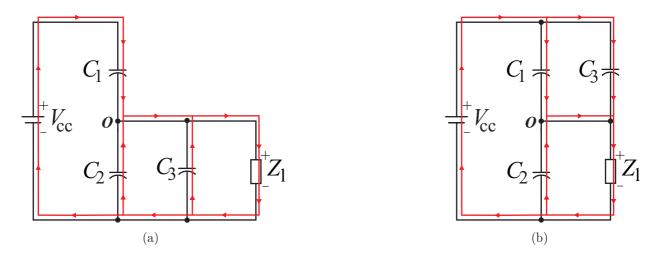

| 5.1  | Formação das topologias propostas: (a) com capacitor no braço ANPC (b)           |     |

|------|----------------------------------------------------------------------------------|-----|

|      | com fonte de tensão no braço ANPC $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 109 |

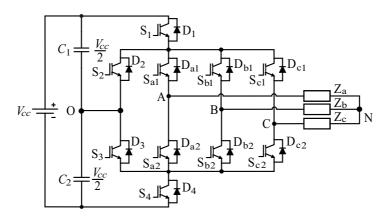

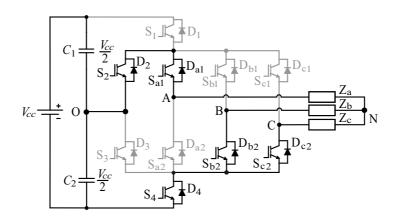

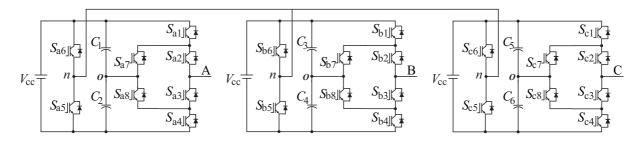

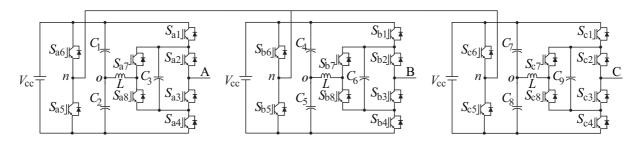

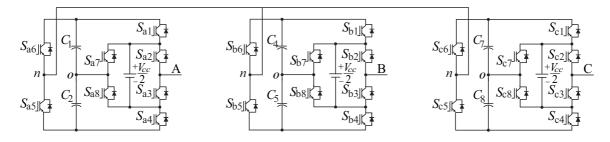

| 5.2  | Inversor trifásico HB-ANPC utilizando seis fontes isoladas                       | 110 |

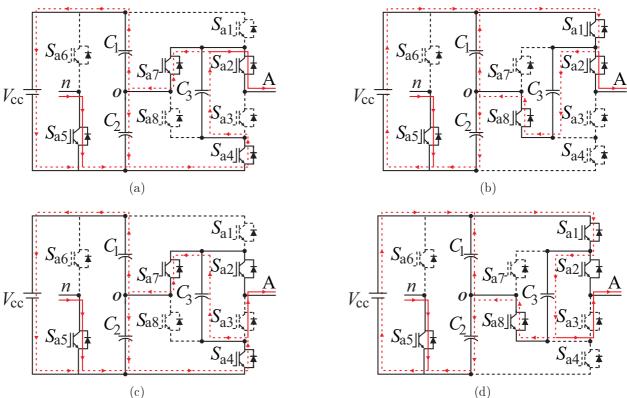

| 5.3  | Modos de operação do inversor HB-ANPC: semi-ciclo positivo                       | 111 |

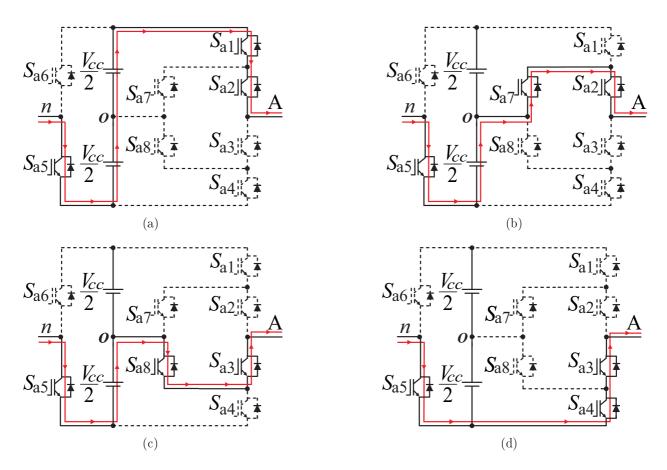

| 5.4  | Modos de operação do inversor HB-ANPC: semi-ciclo negativo                       | 112 |

| 5.5  | Estrutura trifásica HB-ANPC com três fontes de tensão                            | 114 |

| 5.6  | Oscilação das tensões dos capacitores do inversor da Fig 5.5                     | 115 |

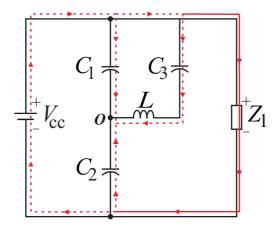

| 5.7  | Conversor proposto com célula ANPC/capacitor flutuante                           | 117 |

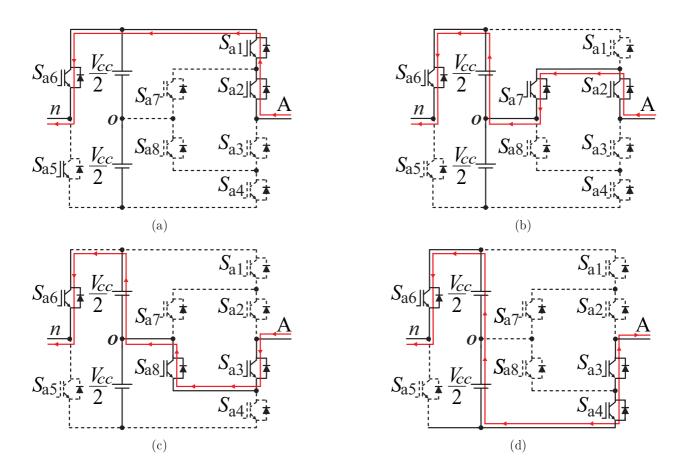

| 5.8  | Modos de operação da estrutura HB-ANPC/FC                                        | 118 |

| 5.9  | Estados transitórios no semi-ciclo positivo                                      | 119 |

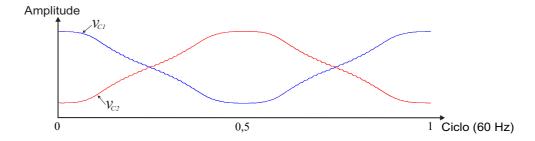

| 5.10 | Variação das tensões: $v_{C1}$ , $v_{C2}$ e $v_{C3}$                             | 120 |

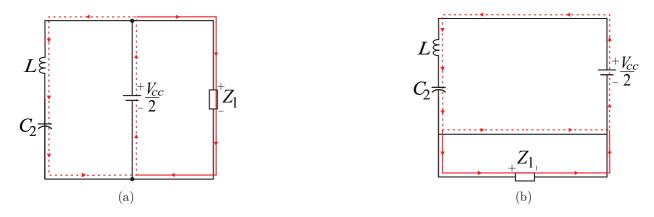

| 5.11 | Conversor HB-ANPC/FC com indutâncias                                             | 120 |

| 5.12 | Variação das tensões: $v_{C1}$ , $v_{C2}$ e $v_{C3}$ com $C_3=2C_1=2C_2$         | 121 |

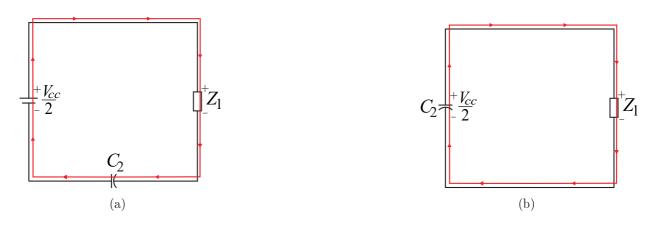

| 5.13 | Circuitos equivalentes dos modos 2 e 3                                           | 121 |

| 5.14 | Circuito equivalente na mudança do modo 2 para o modo 1                          | 123 |

| 5.15 | Conversor com célula ANP C/fonte flutuante                                       | 127 |

| 5.16 | Modos de operação da estrutura HB-ANPC/FS                                        | 129 |

| 5.17 | Conversor HB-ANPC/FS com indutâncias                                             | 129 |

| 5.18 | Circuitos equivalentes dos modos 1 e 3 da estrutura HB-ANPC/FS $$                | 130 |

| 5.19 | Circuitos equivalentes dos modos 2 e 4 da estrutura HB-ANPC/FS $$                | 131 |

| 5.20 | Definição de $P_a, P_b$ e $P_c$ em um inversor de 5-níveis                       | 132 |

| 5.21 | Oscilação da tensão dos capaciotres das três topologias estudadas                | 134 |

| 5.22 | Valores de indutâncias permitidos em função dos capacitores utilizados           | 136 |

| 5.23 | Corrente máxima nas chaves dos inversores propostos                              | 136 |

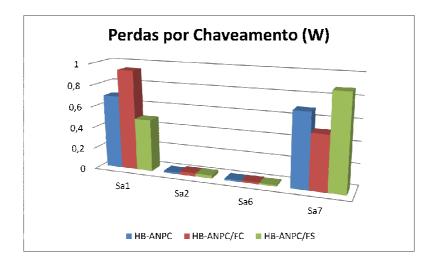

| 5.24 | Distribuição da perdas por chaveamento                                           | 138 |

| 5.25 | Distribuição das perdas por condução                                             | 138 |

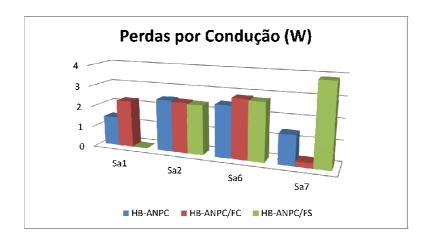

| 5.26 | Perdas totais dos conversores                                                    | 139 |

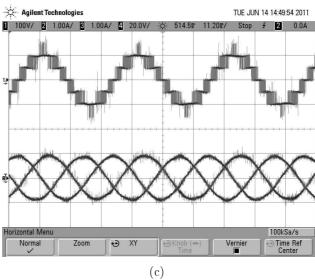

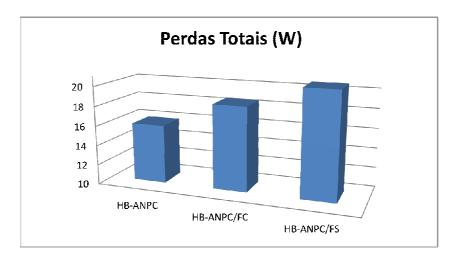

| 5.27 | Configuração HB-ANPC com capacitâncias de $2200 \mu F$ . (a) De cima para        |     |

|      | baixo: Tensão de polo; corrente de carga (b) De cima para baixo: tensão nos      |     |

|      | capacitores; corrente de carga                                                   | 141 |

Índice de Figuras xix

| 5.28 | Configuração HB-ANPC com capacitâncias de $200 \mu F$ . (a) De cima para    |     |

|------|-----------------------------------------------------------------------------|-----|

|      | baixo: Tensão de polo; corrente de carga (b) De cima para baixo: tensão     |     |

|      | nos capacitores; corrente de carga                                          | 141 |

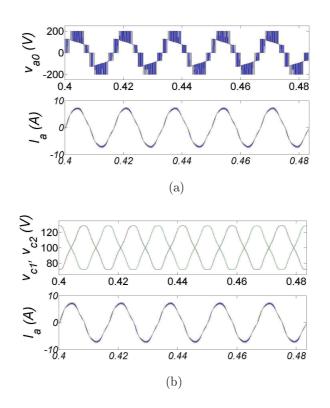

| 5.29 | Configuração HB-ANPC/FC com capacitâncias de $200\mu F.$ (a) De cima para   |     |

|      | baixo: Tensão de polo; corrente de carga (b) De cima para baixo: tensão nos |     |

|      | capacitores; corrente de carga                                              | 142 |

| 5.30 | Configuração HB-ANPC/FS com capacitâncias de $200\mu F.$ (a) De cima para   |     |

|      | baixo: Tensão de polo; corrente de carga (b) De cima para baixo: tensão nos |     |

|      | capacitores; corrente de carga                                              | 143 |

| 5.31 | Configuração HB-ANPC com capacitâncias de $200 \mu F$ . (a) De cima para    |     |

|      | baixo: Tensão de polo; corrente de carga (b) De cima para baixo: tensão     |     |

|      | nos capacitores; corrente na carga                                          | 143 |

| 5.32 | Configuração HB-ANPC/FC com capacitâncias de $200\mu F.$ (a) De cima para   |     |

|      | baixo: Tensão de polo; corrente de carga (b) De cima para baixo: tensão nos |     |

|      | capacitores; corrente na carga                                              | 144 |

| 5.33 | Configuração HB-ANPC/FS com capacitâncias de $200\mu F.$ (a) De cima para   |     |

|      | baixo: Tensão de polo; corrente de carga (b) De cima para baixo: tensão nos |     |

|      | capacitores; corrente na carga                                              | 144 |

## Lista de Símbolos

$f_s$  — Frequência chaveamento

$S_1, S_2, S_3, S_4$  – Chaves de inversores

$V_l$  — Tensão de carga

$v_{a0}, v_{b0}, v_{c0}$  – Tensões de polo

$v_{a0}^*, v_{b0}^*, v_{c0}^*$  – Tensões de referencia

$V_{cc}$  – Tensão da fonte

$V_{c1}, V_{c2}, V_{c3}$  – Tensões nos capacitores

$v_{a0}^{*\prime}, v_{b0}^{*\prime}, v_{c0}^{*\prime}$  — Tensões de referências modificada

$v_{\mu}$  – Tensão homopolar

$P_a, P_b, P_c$  — Diferença de entre os níveis e as senoides de referência

Número de níveis

$T_a, T_b, T_c$  – Tempo de acionamento das chaves

$v_{t1}^*, v_{t2}^*, v_{t3}^*$  – Sinais da portadora

$v_d, v_q$  – Tensões em quadratura

THD – Distorção harmônica total

WTHD – Distorção harmônica total ponderada

$i_a, i_b, i_c$  – Corrente de carga

$v_{max}, v_{med}, v_{min}$  – Valores máximo, médio e mínimo de tensão

a<sub>1</sub> – Amplitude da tensão fundamental

Lista de Símbolos xxi

p – Número de harmônicos total

$a_h$  — Amplitude da n-ésima harmônica

m – índice de modulação

$V_f$  – Tensão da fonte

R – Resistência da carga

$w_l$  — Reatância do indutor de carga

$Z_l$  — Reatância da carga

$\Delta v_c$  – Variação de tensão dos capacitores

$i_{c1}, i_{c2}, i_{c3}$  — Corrente nos capacitores

$T_s$  — Período de chaveamento do conversor

$\Delta Q_c$  – Variação de carga do capacitores

$w_o$  – Frequência de ressonância

# 1

# Introdução Geral

#### 1.1 Localização do Tema

O domínio da energia tem sido de extrema importância para o progresso da humanidade e o percentual de consumo é um dos indicadores do estágio de desenvolvimento de uma nação. Como dados demonstrativos, os Estados Unidos (maior economia mundial) e com apenas 4% da população mundial, consome cerca de 28% da energia global gerada. Já a China, que possui cerca de 20% da população mundial, e que consumia menos que 2,5% no início da década passada, experimentou forte crescimento econômico e agora possui a segunda maior economia, consumindo energia quase no mesmo nível que os Estados Unidos (Bose, 2013). Assim, os países buscam cada vez mais o seu fortalecimento econômico e investem no crescimento industrial. Observa-se que o domínio do manuseio da energia elétrica foi um fator determinante nas transformações que ocorreram no mundo nos últimos séculos, sendo esse tipo de energia o mais utilizado no mundo. Sua demanda global tem crescido continuamente e, em 2030, a capacidade de geração elétrica no mundo terá crescido cerca de 100% (Steimer, 2010).

A energia elétrica é obtida a partir de outras formas de energia, tais como a hídrica, a eólica, a solar, a geotérmica, a das ondas, a das marés e as bio-combustíveis, entre outras (Bose, 2013). As estratégias de controle eficaz da produção, transporte e uso final dessa energia têm sido bem sucedidas graças à eletrônica de potência. A eletrônica de potência é a área da engenharia dedicada ao estudo do processamento e controle do fluxo de energia

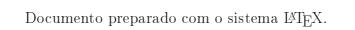

elétrica entre uma fonte (de tensão ou corrente) e uma carga. O processamento da energia é feito por meio de conversores estáticos que são circuitos elétricos compostos de elementos ativos (dispositivos semicondutores). Por meio do controle dos tempos de condução e bloqueio dos elementos ativos, pode-se converter a tensão de entrada com amplitude  $V_e$  e frequência  $f_e$  em uma tensão na saída com amplitude  $V_s$  e frequência  $f_s$ , Fig. 1.1.

Figura 1.1: Processador de Potência (Conversor Estático)

A era da eletrônica de potência moderna começou em 1957 quando o primeiro tiristor, um dispositivo semicondutor de potência que recebeu o nome de Retificador Controlado de Silício (SCR, do inglês Silicon Controlled Rectifier), foi tornado comercial pela General Electric Company. O SCR substituiu o Retificador a Arco de Mercúrio, inventado em 1902, o Tiratron, inventado em 1923, e o Ignitron, inventado em 1931, tornando mais econômico o uso de vários circuitos industriais, concebidos entre os anos 20 e 40, em adição à ponte de Graetz patenteada em 1897. Os SCRs foram utilizados em conversores durante mais de um quarto de século e ainda reinam supremos nas aplicações com potências elevadas. Contudo, os SCRs são considerados lentos e difíceis de comutar em aplicações de corrente contínua e mesmo nas aplicações de corrente alternada já não são considerados a melhor opção. Recentemente, a confluência de dois fatores provocou um crescimento explosivo na Eletrônica de Potência e uma grande revolução na indústria elétrica: 1) novos dispositivos já disponíveis para tensões e correntes elevadas, mais eficientes, de controle mais fácil e de chaveamento mais rápido; 2) o uso de processadores digitais como o DSP (do inglês, Digital Signal Processor) e o FPGA (do inglês, Field Programmable Gate Array). O impacto destes dois fatores foi tão significativo quanto o aparecimento do SCR, permitindo, assim, o uso de novos conceitos de comando e de técnicas de controle moderno dos conversores.

Vários dispositivos são usados hoje em dia: o BJT (*Bipolar Unijunction Transistor*), de 1970, em aplicações de baixa a média potências e frequências, já pouco utilizado; o tiristor GTO (*Gate Turn-off*, GTO), em torno de 1973, em aplicações de baixa a alta potências e

de baixa a média frequências; o MOSFET ( Metal-oxide Semi-conductor Field-effect Transistor), de 1978, em aplicações de baixa potência e frequência elevada; o IGBT (Insulated Bipolar Gate Transistor) de 1983, em aplicações de baixa a média potências e frequências; o IGCT (Integrated Gate Commutated Thyristor), de 1997, e o ETO (Emitter Turn-off), de 1998, em aplicações de média a alta potências e de baixa a média frequências. Assim, os equipamentos podem operar na faixa de alguns poucos watts até os GW, a faixa de frequência indo de algumas centenas de Hz até algumas centenas de kHz, dependendo da potência manuseada (Bat, 2004) e da limitação pela Interferência Eletromagnética.

Com tantos dispositivos, formando um leque composto pelas mais variadas características de tensão, corrente e frequência, e com a facilidade de uso de novas técnicas de controle através de microcomputadores e de outros processadores, a eletrônica de potência passou a ser utilizada em um número cada vez maior e diversificado de aplicações. Elas podem ser do tipo residencial (refrigeração, aquecimento, iluminação, alimentação de computadores, etc.), comercial (aquecimento, ventilação, elevadores, fontes de emergência, etc.), industrial (bombas, compressores, exaustores, moinhos, laminadores, trituradores, ventiladores, robôs, aquecimento indutivo, solda, acionamento de motores, etc.), transporte (veículos elétricos, carregadores de bateria, locomotivas, metrô, eletrônica de automóvel, etc), utility systems (transmissão de alta tensão em corrente contínua, geração de energia, compensação de reativos, FACTS, etc.), aero-espacial (sistemas de alimentação em naves espaciais, satélites e aeronaves), telecomunicações (fontes de alimentação e equipamentos de radio-transmissão) e conversão de energias alternativas (fonte eólica, fonte fotovoltaica, fonte de células combustíveis, propulsores marinhos, etc.) (Kouro et al., 2010).

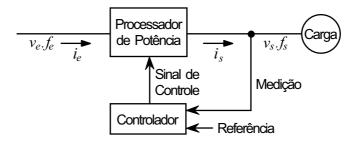

Nessas aplicações, os equipamentos de eletrônica de potência baseiam-se nos chamados conversores estáticos de energia. Esses conversores podem ser classificados de acordo com sua função de conversão da energia elétrica na forma contínua (c.c.) ou alternada (c.a.), em sua entrada, para uma energia elétrica na forma contínua ou alternada, em sua saída, ou seja: conversores c.a./c.a., conversores c.a./c.c., conversores c.c./c.a. e conversores c.c./c.a. Em especial, os conversores c.a./c.c. são referidos como retificadores e conversores c.c./c.a. como inversores. Os conversores c.a./c.a. podem ser diretos ou indiretos, como indicado na classificação apresentada por (Kouro et al., 2010), mostrada na Fig. 1.2. Os conversores diretos são constituídos por cicloconversores e por conversores matriciais. Em particular,

os conversores indiretos realizam, inicialmente, uma conversão c.a./c.c. e, em seguida, uma conversão c.c./c.a.. Ou seja, nesse conversor, um retificador alimenta um inversor. Também, os conversores podem ser do tipo fonte de tensão, do tipo fonte de corrente ou do tipo fonte Z, esta última tendo sido acrescentada à classificação de Kouro.

Figura 1.2: Classificação de Kouro et al. (2010) modificada

Cada aplicação utiliza um tipo adequado de conversor e envolve diferentes aspectos no que tange o uso da eletrônica de potência. Por exemplo, dentre as aplicações industriais, os sistemas de acionamento são, sem dúvida, os mais utilizados. Na tentativa de se melhorar o desempenho dos motores através da melhoria das formas de onda de alimentação, o custo e tamanho de fontes em geral, a existência de dispositivos rápidos e confiáveis permitiu a elevação das frequências de operação dos conversores. Entretanto, isto leva a um aumento das perdas produzidas durante a operação dos conversores, o que piora com o aumento de potência nos grandes motores. Também, a introdução de conversores provocou, em muitos casos, a deterioração da qualidade da energia e a introdução de harmônicos na linha gerando normas que impõem valores mínimos de fator de potência e valores máximos do conteúdo de harmônicos produzidos. Isto acarretou desenvolvimento de novos campos de pesquisa e novos métodos, tais como aqueles que possuem o objetivo de reduzir as perdas. Em particular, a aplicação dos conversores em utility systems e a busca da melhoria da qualidade de energia levou ao conceito de Sistemas Flexíveis de Transmissão CA, FACTS (do inglês Flexible Alternate Current Transmission Systems) e ao desenvolvimento de filtros ativos e compensadores de fator de potência, no nível de sistemas de distribuição. Como aumentar a potência dos conversores mantendo níveis aceitáveis de qualidade de energia e de eficiência energética? Parte dessa exigência do mercado foi satisfeita com o desenvolvimento de dispositivos como o IGBT e, posteriormente, o IGCT e o ETO, e de estruturas de converso-

res, como os chamados multiníveis, capazes de operar nos níveis de média a alta potência, área antes restrita ao uso do SCR utilizados em conversores de dois níveis em conjunto com transformadores de potência elevada. Dentro da classificação de Kouro, conforme a Fig. 1.2, os conversores tipo fonte de tensão são os mais utilizados. Dentro deste contexto, serão investigados, especificamente, os inversores multiníveis.

### 1.2 Revisão Bibliográfica

Foi realizada uma pesquisa bibliográfica para verificar o estado da arte com respeito às topologias de inversores multiníveis e estratégias de modulação para inversores fonte de tensão. Alguns dos trabalhos analisados são apresentados nesta seção.

#### 1.2.1 Inversores Multiníveis

Como mencionado, os inversores multiníveis foram introduzidos como uma alternativa para o aumento da qualidade e dos níveis de tensão dos sistemas alimentados por inversores. A redução do conteúdo harmônico possibilitada por estes inversores, além de melhorar a qualidade dos sinais na saída do inversor, contribui diretamente para redução das perdas nos motores causadas pelas componentes harmônicas das correntes e pela componente pulsante do torque (Corrêa, 2002).

As estruturas de inversores multiníveis possibilitam o controle de níveis maiores de tensão e potência máxima suportáveis pelos interruptores. Com uma quantidade maior de níveis para compor o sinal modulado, estes inversores possibilitam sinais de saída com um conteúdo harmônico bem menor, ou possibilitam a operação em freqüência de comutação mais baixa, porém com a mesma qualidade de um inversor de dois níveis operando em freqüência elevada. Com isso, é possível diminuir as perdas por comutação e a interferência eletromagnética (dos Santos, 2005).

Os conversores multiníveis têm sido fonte de pesquisa e desenvolvimento por mais de três décadas e têm sido aplicados com sucesso em aplicações industriais. Muitas contribuições e topologias comerciais têm sido reportadas nos últimos anos. Atualmente, os conversores têm sido comercializados de forma padronizada ou de forma personalizada de acordo com

cada aplicação específica. Embora seja uma tecnologia já consolidada, o conversor multinível apresenta um horizonte desafiador, com pesquisadores de todo mundo contribuindo para o melhoramento da eficiência, confiabilidade, densidade de potência, simplificação e custo. A ampliação cada vez maior de seu campo de aplicação tem tornado os conversores multiníveis mais atrativos e competitivos do que as topologias clássicas, dependendo dos níveis de tensão, corrente e potência utilizada.

As primeiras estruturas utilizadas para obtenção de formas de onda de tensão multiníveis eram compostas por vários conversores convencionais de dois níveis cujas saídas alimentavam transformadores cujos enrolamentos secundário eram conectados em série (Flairty, 1962; Morgan e Hoft, 1964). As saídas dos conversores eram defasadas e somadas vetorialmente de modo a produzir, no secundário, uma forma de onda quase-senoidal, formada por diferentes degraus de tensão. Essas estruturas foram propostas inicialmente como solução para acionamentos elétricos de alta potência e alto desempenho (Nabae, Takahashi e Akagi, 1981). Entretanto, elas requerem transformadores especiais com doze ou mais secundários, sendo de projeto complicado, caros e, normalmente, sem atenderem aos ensaios de descargas parciais exigidos em cubículos de média tensão.

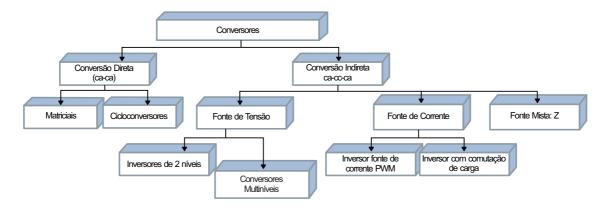

A primeira estrutura de inversor multinível, sem a necessidade de uso de transformadores, registrada foi do tipo em cascata com inversores monofásicos em ponte completa alimentados por fontes c.c. separadas e conectados em série para sintetizar as tensões c.a. de saída na forma de degraus (Baker e H., 1975). Sua estrutura, amplamente utilizada para se conseguir múltiplos níveis de tensão pode ser vista na Fig. 1.3, para um inversor em cascata de cinco níveis. A tensão de saída é obtida somando-se a tensão de saída de cada módulo. Embora a estrutura tenha surgido em 1975, seu uso só se deu a partir do final dos anos 80 (Marchesoni et al., 1988; Marchesoni, 1989). Posteriormente, essa mesma topologia foi investigada para aplicação em compensadores estáticos de reativos (Lai e Peng, 1996; Peng et al., 1996). Note-se que o componente básico desta estrutura, o módulo, é o inversor monofásico em ponte completa, capaz de operar em três níveis desde que os disparos dos interruptores de cada braço sejam defasados um em relação ao outro.

A topologia de inversor de três níveis com diodos de grampeamento NPC (do inglês, Neutral Point Clamped), Fig. 1.4(a), uma alternativa para o inversor de três níveis em cascata, foi introduzida em (Baker, 1980), tendo despertado interesse após o trabalho apresentado

Figura 1.3: Topologia de cinco níveis em Cascata

em (Nabae, Takahashi e Akagi, 1981). Como o próprio nome diz, possui diodos de grampeamento que são conectados ao barramento c.c. do inversor. Observa-se na Fig. 1.4(a) que cada braço do inversor de três níveis NPC é formado por quatro dispositivos semicondutores com seus respectivos diodos em anti-paralelo e dois diodos ligados ao ponto central do barramento. A tensão sobre os interruptores é mantida igual à tensão dos capacitores  $C_1$  ou  $C_2$  através dos dois diodos de grampeamento em cada braço. A tensão em cada capacitor deve ser mantida o mais próximo possível do valor ideal  $V_{cc}/2$  para garantir que as tensões de polo assumam os valores  $-V_{cc}/2$ , 0 ou  $V_{cc}/2$ . Um segundo tipo do inversor NPC, indicado Fig. 1.4(b), foi também investigado em (Nabae, Takahashi e Akagi, 1981). Nesse caso, o acesso ao ponto central é obtido através de um interruptor bidirecional e, embora o número de interruptores seja reduzido, os do braço, conectados ao barramento c.c. têm que suportar, toda sua tensão.

Só posteriormente, o conceito de inversor multinível foi aplicado em uma estrutura generalizada para N níveis (Bhagwat e Stefanovic, 1983; Choi et al., 1991), a partir da introdução de interruptores adicionais (tiristores, no caso de Bhagwat e GTOs no caso de Choi) conectando a fase aos pontos intermediários entre vários capacitores colocados no barramento c.c.. Esses circuitos são indicados nas Figs. 1.5(a) e 1.5(b). Embora, sem ter o mesmo impacto de outras topologias, o inversor generalizado de Bhagwat mostrou as vantagens da redução de harmônicas através da utilização das estruturas multiníveis. Em particular, a versão para três níveis do inversor de Bhagwat corresponde à segunda versão do NPC apresentada em

(Nabae, Takahashi e Akagi, 1981), Fig. 1.4(b). Já o inversor proposto por Choi é uma generalização direta do NPC de três níveis da Fig. 1.4(a).

Figura 1.4: Inversores NPC tipo I e II (ou T): (a) braço de inversor NPC de três níveis tipo I; (b) braço de inversor NPC de três níveis tipo II.

Figura 1.5: Inversores multiníveis Bhagwat e NPC: (a) Braço de inversor de Bhagwat de sete níveis; (b) Braço de inversor NPC de cinco níveis.

No início da década de 90, surgiu mais uma alternativa para inversores multiníveis: o princípio do inversor multinível com capacitores flutuantes, indicado na Fig. 1.6 e proposto por (Meynard e Foch, 1992). Nela, a tensão sobre os interruptores é limitada utilizando-se capacitores em lugar dos diodos, o que diminui as perdas em condução. No entanto, o uso deste princípio aumenta a complexidade das técnicas utilizadas para equalizar as tensões, não só no barramento c.c., mas também nos capacitores flutuantes.

Na época, os inversores NPC, os inversores a capacitor flutuante e os inversores em cascata foram considerados os mais importantes, tendo sido, por esta razão, realizados diversos estudos comparativos entre os mesmos (Lai e Peng, 1996; Peng et al., 1996). Daí em diante, muitas configurações, capazes de gerar três ou mais níveis de tensão em sua saída, foram propostas (Suh et al., 1998), (Rodriguez et al., 2002), com o intuito de reduzir o conteúdo harmônico da tensão de saída (Mariethoz e Rufer, 2004; Weng et al., 2007), de diminuir a quantidade de componentes ativos e passivos, de melhorar a eficiência e diminuir os esforços de tensão sobre os semicondutores (Kouro et al., 2010; Chan et al., 2009; Boora et al., 2010), especialmente em aplicações de média e de alta potência, como compensadores de potência reativa e acionamento de motores c.a.. Por exemplo, os diodos do inversor multinível indicado na Fig. 1.5(b) suportam tensões desiguais, conforme sua localização. Uma modificação efetuada para minorar este problema foi a de distribuir estas tensões elevadas em diodos adequadamente conectados em série (Lai e Peng, 1996). Um grampeamento adequado para equalizar as tensões sobre os diodos foi obtida em (Xiaoming Yuan, 2000), mostrado na Fig. 1.7. Uma outra concepção, que tinha como proposta melhorar a distribuição das perdas nos interruptores, em relação ao NPC, foi tornada conhecida na sua versão de três níveis em (Bruckner e Bemet, 2001; Bruckner et al., 2005) e apresentada em sua forma generalizada em (Peng, 2001): o inversor multinível com grampeamento ativo do neutro (ANPC - Active Neutral Point Clamped), apresentado na Fig. 1.8.

Figura 1.6: Braço de um inversor FC de três níveis.

Uma busca na redução de componentes, levou à conexão de meia pontes, também alimentadas por fontes isoladas, resultando numa fonte multinível c.c. (Su e Adams, 2001; Su, 2005), cujo número de componentes foi ainda mais reduzido, posteriormente, com a utiliza-

Figura 1.7: Braço de um inversor com grampeamento por diodos

Figura 1.8: Braço de um inversor ANPC: (a) ANPC de três níveis; (b) ANPC de cinco níveis

ção de meia-ponte mistas (Chen et al., 2008). Estas duas topologias são indicadas nas Figs. 1.9(a) e 1.9(b). Essas fontes de tensão c.c. variável são utilizadas para alimentar um braço de inversor, como indica a Fig. 1.9(c).

Um outro princípio inventado a partir da conexão série de estruturas em meia-ponte, de dois níveis, foi a de inversor modular (Lesnicar e Marquardt, 2003). Como se observa, a conexão cascata utiliza fontes individuais, sem tensão de barramento c.c. O conceito de inversor modular implica em substituir a fonte isolada por um capacitor de armazenamento, cada meia ponte e seu capacitor constituindo um módulo. Dois conjuntos compostos, cada um, de vários módulos em cascata, simetricamente conectados em relação a um ponto central são alimentados por um barramento c.c, como ilustra a Fig. 1.9(d).

Figura 1.9: Inversores em cascata: (a) utilizando meia-ponte; (b) utilizando meia-ponte mista; (c) formando um braço de inversor; (d) simetricamente conectados em relação a um ponto central.

Outras configurações resultaram de diferentes tipos de combinações, dando origem aos conversores híbridos, havendo um grande número de possibilidades para sua geração. Por

exemplo, pode ser feita uma associação de diferentes princípios, ou de partes de diferentes estruturas, na formação de um braço. É o caso do inversor no qual um capacitor flutuante é adicionado à topologia NPC (Suh e Hyun, 1997). Tal estrutura, apresentada na Fig. 1.10, tem como vantagem a redução da flutuação de tensão no ponto neutro e do balanceamento das tensões de bloqueio nos interruptores e como desvantagem o acréscimo de componentes. Este tipo de combinação foi, posteriormente, estendido para o caso do inversor ANPC, de modo generalizado, em (Peng, 2001), Fig. 1.11, e para cinco níveis, com redução do número de componentes em (Barbosa et al., 2005), Fig. 1.12.

Figura 1.10: Braço de um inversor híbrido NPC/FC de três níveis.

Figura 1.11: Generalização do braço de um inversor ANPC/FC.

Outra possibilidade de estrutura híbrida é obtida quando se utiliza diferentes valores nas fontes de alimentação ou das tensões nos capacitores de armazenamento. Por exemplo,

Figura 1.12: Braço de um inversor ANPC/FC de cinco níveis com redução de componentes.

quando o capacitor flutuante do inversor da Fig. 1.6 é substituído por uma fonte fixa, de valor diferente da metade da tensão do barramento c.c., o número de níveis de tensão aumenta, para um mesmo número de dispositivos semicondutores (Kou, Corzine e Familiant, 2002). O mesmo ocorre quando as tensões das fontes isoladas da estrutura em cascata da Fig. 1.3 têm valores diferentes (Manjrekar e Lipo, 1998). Também, topologias híbridas foram concebidas a partir da associação de diferentes tipos de dispositivos semicondutores (Manjrekar e Lipo, 1998).

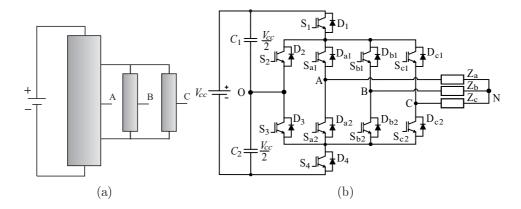

Outra possibilidade, ainda, é a de gerar pontes inversoras híbridas para aplicações de alta tensão e alta potência utilizando braços de inversores multiníveis, tipo NPC (Ding et al., 2003), (Sneineh et al., 2006), FC/NPC (Zhang e Ruan, 2005) ou FC/ANPC (Li et al., 2009) para substituir os braços de uma ponte inversora de dois níveis, constantes da Fig. 1.3. As Figs. 1.13 a 1.16 ilustram essas pontes inversoras. Quando esses módulos são conectados em cascata, consegue-se um aumento do número de níveis com um número menor de fontes isoladas.

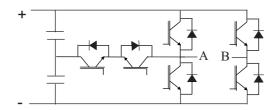

O número de componentes das pontes multiníveis acima pode ser reduzido quando um dos braços é substituído por uma estrutura de dois níveis, dando origem a uma hibridez quanto ao número de níveis em cada braço da ponte. A topologia meia ponte e NPC, indicada na Fig. 1.17, foi proposta em (Kai et al., 2004) e (Almeida et al., 2006). Uma variação, apresentada na Fig. 1.18 permite que dispositivos mais rápidos e de alta tensão operem em sinergismo. Essa topologia também permite a comutação de metade dos interruptores em baixa frequência (a da modulante), contribuindo, assim, com a redução das perdas (Silva

Figura 1.13: Ponte inversora NPC  $\,$

Figura 1.14: Ponte inversora FC

Figura 1.15: Ponte inversora  $\mathrm{NPC}/\mathrm{FC}$

Figura 1.16: Ponte inversora ANPC/FC

et al., 2011).

Figura 1.17: Ponte inversora NPC/meia-ponte

Figura 1.18: Ponte inversora ANPC/meia-ponte

Como se observa das Figs. 1.17 e 1.18, os dispositivos que compõem o braço de dois níveis suportam toda a tensão do barramento, o que limita sua potência de aplicação. Outras soluções que utilizam o mesmo princípio são ilustradas nas Figs. 1.19 (Ceglia et al., 2004), 1.20 (Oliveira Jr, Silva e Jacobina, 2006). Algumas soluções procuraram minorar este problema, como o inversor da Fig. 1.21 (Astudillo et al., 2008). As três topologias operam com

cinco níveis de tensão na saída. Entretanto, a topologia da Fig. 1.21 é capaz de manusear potências mais elevadas.

Figura 1.19: Inversor multinível de cinco níveis

Figura 1.20: Inversor híbrido com número reduzido de componentes

Figura 1.21: Inversor multinível híbrido simétrico

Ainda, o conceito de fonte multinível c.c. deu origem a inúmeras topologias híbridas e pode ser aplicado a muitas das topologias já mencionadas acima (Baek et al., 2005), (Lezana e Rodriguez, 2007), (Rosas-Caro et al., 2008), (Ruiz-Caballero et al., 2010), (Banaei e Salary, 2010), (Rodríguez-Rodríguez et al., 2011), (Najafi e Yatim, 2012), (Basha e Nayeemuddin, 2013), (K. Rachel, 2013).

Também, é possível obter topologias híbridas através da associação de conversores em ponte com componentes magnéticos como indutores e transformadores. É o caso de braços de pontes conectados através de reatores acoplados (Ueda et al., 1995; Matsui et al., 1996; Hausmann e Barbi, 2009; Vafakhah et al., 2010; Floricau et al., 2011; Ewanchuk et al., 2012)

Além disso o conceito de inversores modulares tem sido amplamente aplicado a inúmeras topologias, como pontes completas, resultando em inúmeros inversores híbridos (Hiller et al., 2009; Marquardt, 2010; Solas et al., 2013; Ilves et al., 2015; Nami et al., 2015).

Existem diferentes possibilidades de formação de inversores multiníveis trifásicos, cujos princípios serão discutidos a seguir. Uma primeira possibilidade é o de uma ponte inversora com uma fonte c.c. comum, ilustrado no esquema da Fig. 1.22(a). Um exemplo é a conexão de três braços de inversores NPC, formando a ponte com fonte comum de alimentação, como mostra a Fig. 1.22(b) (Teichmann e Bernet, 2003). Diferentes braços podem ser utilizados nesse arranjo, como é o caso da utilização de inversores ANPC, a capacitor flutuante, inversores modulares formados por meia-ponte (Lesnicar e Marquardt, 2003), por ponte completa, por uma combinação de ponte completa e meia-ponte (Feldman et al., 2012) e outros tipos (Nami et al., 2015).

Figura 1.22: Ponte inversora com uma fonte c.c. comum: (a) Diagrama de blocos; (b) Topologia de três níveis para conversores de potência de baixa tensão.

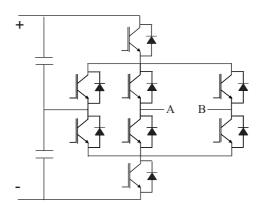

Uma segunda possibilidade é o de um inversor formado por braços conectados em estrela, cujo esquema é indicado na Fig. 1.23(a). Um exemplo é o inversor ilustrado na Fig. 1.23(b) em que a ponte mostrada na Fig. 1.18 forma um dos braços da conexão em estrela (E Silva, 2012). Outros exemplos são o caso do uso dos inversores constantes das Figs. 1.17 (Ding et al., 2003), 1.20 (Tang et al., 2009) e 1.21 (Carmona et al., 2008). Também, é o caso de pontes em cascata formando o braço, como ilustrado na Fig. 1.23(c) (Lai e Shyu, 2002).

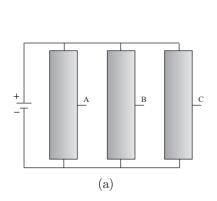

O princípio ilustrado na Fig. 1.24(a) é o de uma fonte multinível alimentando um inversor convencional de dois níveis. Uma realização deste princípio é mostrada na Fig. 1.24(b) (Su

Figura 1.23: Inversores formado por braços conectados em estrela: (a) Diagrama de blocos; (b) Inversor trifásico meia-ponte/ANPC; (c) braço formado por pontes em cascata.

e Adams, 2001).

Figura 1.24: Fonte multinível alimentando um inversor convencional: (a) Diagrama de blocos; (b) Inversor com fonte Multinível.

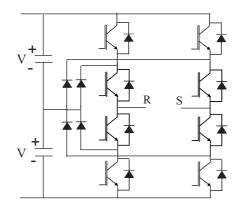

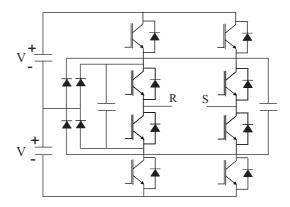

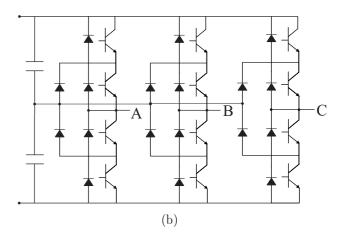

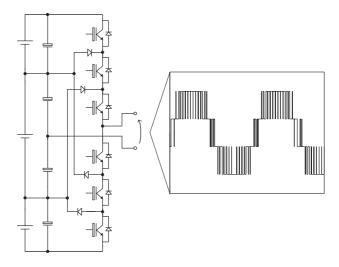

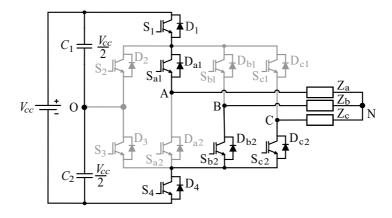

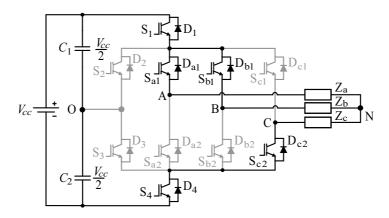

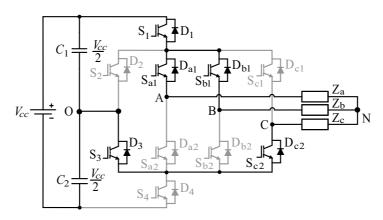

No esquema da Fig. 1.25(a), um dos braços é de nível maior do que os outros dois. No exemplo da Fig. 1.25(b), o inversor, nomeado como 2/3 níveis (Mihalache, 2006), é formado por um braço ANPC de três níveis e dois braços de dois níveis. Este caso, também pode ser considerado como originário da adição de mais uma fase da ponte monofásica ilustrada na Fig. 1.21 (Astudillo et al., 2008).

Outras possibilidades resultam da combinação de pontes trifásicas, associação de pontes monofásicas H e transformadores. Exemplos são dados em (Veenstra e Rufer, 2003).

#### 1.2.2 Técnicas de Modulação para Inversores Multiníveis

Com o aumento do número de semicondutores nas estruturas de inversores objetivando melhorar a qualidade da tensão de saída; reduzir as perdas do inversor; e realizar o balanceamento de tensão entre os capacitores do barramento c.c.; Diversas técnicas de modulação e estratégias de controle têm se desenvolvido. Várias são as estratégias discutidas e utilizadas

Figura 1.25: Inversores trifásicos com um dos braços de nível maior: (a) Diagrama de blocos; (b) Inversor Híbrido de 2/3 níveis.

na literatura técnica para o comando dos inversores de tensão multiníveis. Embora, cada uma delas tenha suas características e vantagens próprias, a seleção da melhor estratégia baseia-se na satisfação de vários fatores (dos Santos, 2005):

- Menor conteúdo harmônico nas tensões e nas correntes de saída

- Menor ruído acústico e interferência eletromagnética provocados pelo inversor no sistema.

- Menores perdas por comutação e em condução.

- Operação na região de sobremodulação.

Nos anos 60, as tensões de saída dos inversores multiníveis tinham a forma de degraus de diferentes níveis, obtidos pela soma das saídas de vários inversores operando em paralelo através do defasamento das mesmas entre si (Flairty, 1962). Em 1977 foi desenvolvida uma técnica de modulação em degrau, aplicada a um inversor de três níveis a transistores (Baker, 1977a; Baker, 1977b). Em 1983, com o objetivo de controlar a tensão de saída foi concebido o primeiro controle de um inversor em três níveis usando uma forma de onda triangular, a técnica PWM uniforme, em que a modulante é um sinal constante (ou uma onda quadrada na frequência de saída) e os pulsos gerados são equidistantes e de largura constante. Sabe-se que com um número suficiente de pulsos por ciclo o conteúdo harmônico de uma forma de onda modulada se aproxima da envoltória (Patel e Hoft, 1974). Entretanto, para harmônicos de ordem mais elevada, é necessário um grande número de pulsos, para obter uma redução apreciável de harmônicos (Maz, 1997).

Em 1988, duas estratégias PWM para inversores de três níveis foram desenvolvidos a partir de dois métodos clássicos para inversores de dois níveis. O primeiro método, o PWM otimizado ou pré-calculado, utiliza cálculos fora de operação, de acordo com os conteúdos harmônicos ou outros critérios como otimização, eliminação de harmônicos e outros, que são armazenados para serem reproduzidos em operação (Patel e Hoft, 1974; Bowes e Bird, 1975; Buja e Indri, 1977). O segundo método, o método PWM sub-harmônico, desenvolvido em 1964 para inversores de dois níveis e hoje também conhecido com PWM por portadora, é uma estratégia baseada na intersecção em tempo real de uma modulante senoidal com uma portadora triangular (Schönung e Stemmler, 1964). Em 1981 foi feita uma generalização do método sub-harmônico para operações com o índice de modulação maior que um (m > 1), tanto para modulações de dois níveis como modulações de três níveis (Mazzucchelli et al., 1981). Em 1988, na versão de três níveis, foram utilizadas duas modulantes senoidais e uma portadora triangular, a técnica sendo nominada pelos autores como dipolar (Velaerts et al., 1988).

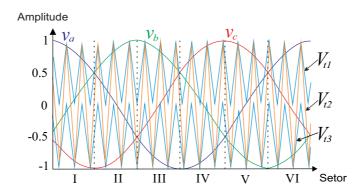

Uma outra abordagem da técnica PWM por portadora foi concebida em 1992, de forma generalizada, para controle de inversores de três níveis ou mais níveis, monofásicos, ou trifásicos. Essa técnica consiste no uso de uma modulante senoidal e de N-1 portadoras triangulares(Carrara et al., 1992). Os dois tipos mais interessantes de disposição das portadoras são discutidos: a) aquela com deslocamento de fase (Phase-Shifted Pulse Width Modulation - PSPWM) e (b) aquela com deslocamento de nível (Level-Shifted Pulse Width Modulation - LSPWM).

A Modulação por Largura de Pulso com Deslocamento de Fase, utiliza duas portadoras triangulares defasadas em cento e oitenta graus, para aplicações em inversores de três níveis (Carrara et al., 1992). A vantagem dessa técnica de modulação é a simplicidade de sua implementação, além de ela permitir o balanceamento natural das tensões nos capacitores flutuantes. Como desvantagem pode-se citar a Distorção harmônica Total (DHT) da tensão de saída apresentada em inversores que utilizam esta modulação, principalmente para aplicações que utilizam baixos índices de modulação (Floricau et al., 2009). Outra limitação desta técnica é que ela não pode ser aplicada ao inversor NPC. Para superar esta desvantagem é que foram desenvolvidas outras técnicas utilizando duas portadoras defasadas em níveis de tensão, as de Modulação por Largura de Pulso com Deslocamento de Nível. Depen-

dendo da disposição das triangulares e seu defasamento no tempo, esta modulação pode ser dividida em três tipos distintos: PD (*Phase Disposition*, do inglês, em fase), POD (*Phase-Opposition Disposition*, do inglês, disposição em oposição de fase) (Carrara e Marchesoni, 1992), e APOD (*Alternate Phase-Opposition Disposition*, do inglês, disposição em oposição com alternância de fase) (E Silva, 2012).

Ainda em 1988 surgiu a aplicação da modulação vetorial (VSM) aos conversores multiníveis (Steinke, 1988). Depois ela foi estendida e generalizada para N níveis (Kouro et al., 2010). Uma característica comum a todas às técnicas de modulação vetorial é que este algoritmo é dividido em três estágios: no primeiro, é definido o estado das chaves ou vetor a ser utilizado para a modulação, o qual usualmente é um dos três vetores mais próximos da referência; no segundo estágio são definidos os tempos de condução e bloqueio das chaves; e no terceiro estágio é definida a sequência na qual os vetores são gerados (McGrath e Holmes, 2002). Diferentes contribuições têm sido reportadas no sentido de tornar mais eficiente alguns desses três estágios (Gopinath et al., 2009). Entretanto, algumas técnicas foram introduzidas para empregar a modulação vetorial de modo algébrico (Seixas et al., 2000).

As modulações por portadora e vetorial têm sido as mais empregadas e estudadas. O estabelecimento das primeiras relações entre as duas técnicas ocorreram no início do século XXI (Wu e He, 2001). Para inversores de dois níveis, obteve-se o mesmo desempenho conseguido com a modulação vetorial, empregando uma modulação híbrida, divulgada em (Blasko, 1996). Essa técnica híbrida usa um sinal de sequência zero com o triplo da frequência das tensões de referência como o termo de tensão comum. A modulação por portadora (CB-PWM) pode produzir os mesmos resultados da modulação vetorial (SV-PWM) quando um sinal adequado de sequência zero é injetado nas tensões de referência (Wu e He, 2001). Também, pode diminuir as oscilações nas correntes, estender a região de linearidade (sobremodulação), reduzir a frequência de comutação média, assim como, diminuir os harmônicos de corrente (Lee et al., 1999). A técnica permite efetuar algebricamente os cálculos para determinação dos vetores de tensão e seus tempos de aplicação a partir da estratégia de comando vetorial, diminuindo a complexidade e o tempo das operações. Essa técnica híbrida é interessante para o comando de inversores multiníveis devido ao fato de estes terem um número elevado de vetores de tensão, o que aumenta a dificuldade de implementação da estratégia

SV-PWM convencional. Uma generalização dessa técnica foi introduzida posteriormente em (de Oliveira et al., 2004) e pode ser facilmente adaptada a diferentes topologias.

Como visto, existem diferentes tipos de inversores híbridos. Uma visão geral dos métodos de modulação aplicados a inversores híbridos multiníveis é apresentada em (Chandwani e Matnani, 2012). É visto que para alguns inversores híbridos as técnicas clássicas PWM podem ser aplicadas de forma direta, enquanto para outras topologias são necessárias algumas modificações e adaptações (Radan et al., 2007; Aghdam et al., 2008; Rech e Pinheiro, 2007).

Além do desenvolvimento dos métodos de modulação, alguns pontos específicos como redução da tensão de modo-comum, detecção de faltas e balanceamento das tensões dos capacitores do barramento c.c. são igualmente importantes. Destes tópicos, o problema mais conhecido é o de desbalanceamento das tensões dos capacitores de inversores multiníveis como o NPC (Kouro et al., 2010). Particularmente, o desbalanceamento em inversores de três níveis NPC, foi extensivamente estudado e inúmeras soluções foram reportadas (Rodriguez et al., 2009).

Geralmente, o controle da tensão do barramento capacitivo dos inversores multiníveis é feito utilizando técnicas em malha fechada. No entanto, existem alguns métodos que empregam circuitos auxiliares. Uma dessas técnicas, apresentada por (Von Jouanne et al., 2002), é a conexão ao ponto central do barramento de um indutor L que transfere a carga excedente de um capacitor para outro, mantendo as tensões equilibradas. Esta solução é muito utilizada em fontes UPS para manter balanceadas as tensões nas baterias. Outra maneira de manter os valores das tensões nos capacitores c.c. iguais é utilizando, na entrada do retificador, um transformador com dois enrolamentos no secundário, ligados cada um a uma ponte retificadora e a um capacitor do barramento. Os dois enrolamentos devem garantir a mesma tensão em cada um dos capacitores caso não sejam utilizados interruptores controlados nas pontes retificadoras. Para inversores NPC de quatro ou mais níveis e em diversas outras topologias, o controle da tensão do barramento não pode ser conseguido com técnicas convencionais, sendo um dos pontos que vem exigindo bastante atenção por parte de pesquisadores (Kouro et al., 2010).

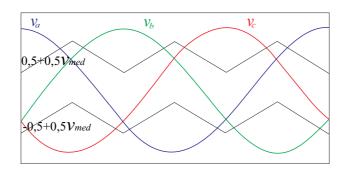

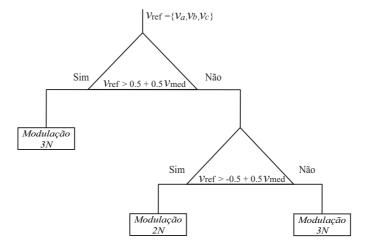

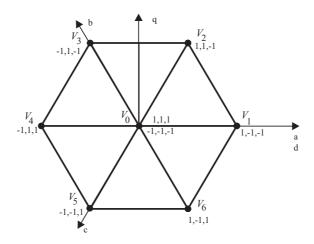

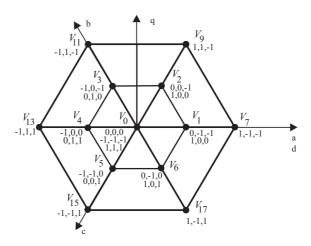

# 1.3 Empilhamento de Células Dois Níveis