### Universidade Federal de Campina Grande

## Centro de Engenharia Elétrica e Informática

Curso de Graduação em Engenharia Elétrica

CARLOS ANTONIO ALVES DE ARAÚJO JÚNIOR

# ESTUDO, VIA SIMULAÇÃO, DE INVERSORES DE TRÊS NÍVEIS TIPO CAPACITOR FLUTUANTE

Campina Grande, Paraíba Novembro de 2012

#### CARLOS ANTONIO ALVES DE ARAÚJO JÚNIOR

# ESTUDO, VIA SIMULAÇÃO, DE INVERSORES DE TRÊS NÍVEIS TIPO CAPACITOR FLUTUANTE

Trabalho de Conclusão de Curso submetido à Unidade Acadêmica de Engenharia Elétrica da Universidade Federal de Campina Grande como parte dos requisitos necessários para a obtenção do grau de Bacharel em Ciências no Domínio da Engenharia Elétrica.

Área de Concentração: Processamento de Energia

Orientador:

Professor D. Sc. Maurício Beltrão de Rossiter Corrêa.

Campina Grande, Paraíba Novembro de 2012

#### CARLOS ANTONIO ALVES DE ARAÚJO JÚNIOR

# ESTUDO, VIA SIMULAÇÃO, DE INVERSORES DE TRÊS NÍVEIS TIPO CAPACITOR FLUTUANTE

Trabalho de Conclusão de Curso submetido à Unidade Acadêmica de Engenharia Elétrica da Universidade Federal de Campina Grande como parte dos requisitos necessários para a obtenção do grau de Bacharel em Ciências no Domínio da Engenharia Elétrica.

Área de Concentração: Processamento de Energia

Aprovado em / /

**Professor Avaliador**Universidade Federal de Campina Grande

Avaliador

Professor D. Sc. Maurício Beltrão de Rossiter Côrrea. Universidade Federal de Campina Grande Orientador, UFCG

#### **AGRADECIMENTOS**

Agradeço a Deus, em primeiro lugar, pela minha vida e por sempre me abençoar com força e persistência para nunca desistir e por sempre iluminar meu caminho nos momentos difíceis durante todo o curso.

Agradeço ao meu professor-orientador Euzeli Cipriano dos Santos Jr., Prof. Edison Roberto Cabral da Silva e ao Prof. Maurício Beltrão por toda atenção e tempo gasto em mim para a conclusão desse trabalho.

Agradeço também à meu pai Carlos Antonio Alves de Araújo, minha mão Ana Maria Cavalcanti de Almeida e meu irmão Aristóteles Terceiro Neto, por sempre estarem ao meu lado me apoiando e dando muito amor e conselhos que me ajudaram a crescer cada vez mais na minha vida.

Agradeço também a minha namorada Lígia Rabay por todo amor e companheirismo que ela devotou a mim durante todo esse tempo juntos e que me ajudou a sempre persistir.

Agradeço também a toda minha família, que com todo carinho e apoio.

Enfim, agradeço a todos os meus amigos que sempre estiveram ao meu lado, nas horas de estudo e de brincadeira, com certeza, sem esse apoio eu não conseguiria atingir todos os meus objetivos.

"Não tentes ser bem sucedido, tenta ser um homem de valor."

#### **RESUMO**

Os inversores são dispositivos usados para conversão de uma forma de tensão de entrada CC para uma outra forma de tensão de saída CA. Essa conversão é feita através do chaveamento de chaves, com disparo ou bloqueios controlados, em uma determinada frequência, fixa ou variável. Os inversores mais utilizados são os inversores monofásicos e trifásicos. Atualmente há um grande interesse nos inversores-multiníveis, pois é possível manusear uma maior potência e gerar menos harmônicos do que o inversor convencional para uma mesma frequência de operação. Há três arquiteturas básicas de inversores de multi-níveis: o inversor com grampeamento por diodos (*Diode Clamped inverter*, em inglês), o inversor com capacitor flutuante (*Flying Capacitor inverter*, em inglês) e o inversor ponte H em cascata (em inglês *cascade H-bridge*). Nesse trabalho será focada a arquitetura com capacitor flutuante e será feito um estudo usando o método baseado na portadora para PWM para controle de chaves. Será simulado, utilizando o software *PSIM*, um inversor trifásico usando esse controle para verificar seu uso e mostrar a sua eficácia através da análise de distorção harmônica na saída do inversor.

Palavras-chave: inversores, controle, harmônicos, capacitor flutuante, PWM.

# Sumário

| Agradecimentos                                                     | iv   |

|--------------------------------------------------------------------|------|

| Resumo                                                             | vi   |

| Sumário                                                            | vii  |

| Lista de Ilustrações                                               | viii |

| Lista de Tabelas                                                   | X    |

| Lista de Abreviaturas e Siglas                                     | xi   |

| 1 Introdução                                                       | 1    |

| 1.1 Topologia com grampeamento por diodos                          | 2    |

| 1.2 Topologia com ponte h em Cascata                               | 3    |

| 1.3 Topologia com capacitor flutuante                              | 4    |

| 2 Inversor com capacitor Flutuante                                 | 6    |

| 2.1 Modo de operação do conversor                                  | 6    |

| 2.2 Técnica de controle PWM utilizada                              | 8    |

| 2.3 Carregamento e descarregamento do capacitor                    | 10   |

| 2.3.1 Etapa 1: quando S1 = 1 e S2 = 1:                             | 11   |

| 2.3.2 Etapa 2: quando $S1 = 0$ e $S2 = 1$ ou $S1 = 1$ e $S2 = 0$ ; | 11   |

| 2.3.3 Etapa 3: quando S1 = 0 e S2 = 0;                             | 12   |

| 2.4 Limitação da Técnica PWM e Faixa de operação do Inversor       | 14   |

| 3 Estudo de Caso Através de Simulação                              | 18   |

| 4 Conclusão                                                        | 25   |

| Bibliografia                                                       | 26   |

# LISTA DE ILUSTRAÇÕES

| Figura 1 - Configuração basica de um inversor com diodo grampeado de 3 niveis                             | 3         |

|-----------------------------------------------------------------------------------------------------------|-----------|

| Figura 2 - Célula de um inversor ponte H monofásico.                                                      | 4         |

| Figura 3 - Topologia do Capacitor Flutuante                                                               | 6         |

| Figura 4 - Conversor utilizando Capacitor Flutuante                                                       | 7         |

| Figura 5 - Forma de onda da portadora 1 e 2, respectivamente, no ciclo positivo da referência             | 8         |

| Figura 6 - Forma de onda da portadora 1 e 2, respectivamente, no ciclo negativo da referência             | 8         |

| Figura 7 - Sinais das portadoras em comparação com a referência, sinais de comando enviados pa            | ıra chave |

| S1 e S2, respectivamente, para o ciclo positivo da referência.                                            | 9         |

| Figura 8 - Sinais das portadoras em comparação com a referência [1], sinais de comando enviado            | s para    |

| chave S1 [2] e S2 [3] para o ciclo negativo da referencia.                                                | 9         |

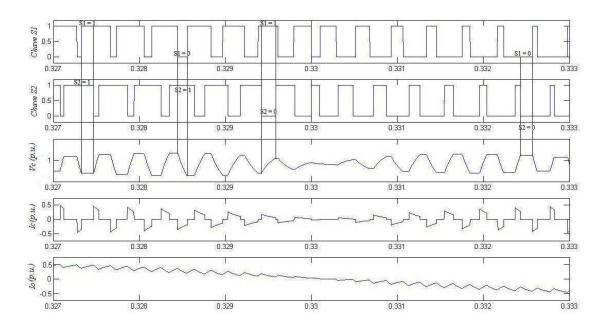

| Figura 9 - Gráfico do sinal de comando da chave S1 e S2, tensão no capacitor, corrente no capaci          | tor e na  |

| carga, respectivamente, para carga predominantemente resistiva.                                           | 10        |

| Figura 10 - Gráfico do sinal de comando da chave S1 e S2, tensão no capacitor, corrente no capac          | itor e na |

| carga, respectivamente, para carga predominantemente indutiva.                                            | 11        |

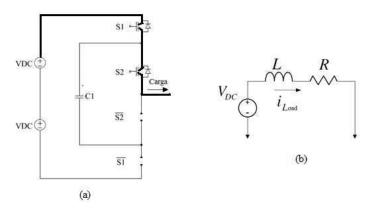

| Figura 11 - Circuito equivalente $S1 = 1$ e $S2 = 0$ , (a) fluxo de corrente positiva e (b) circuito simp | lificado  |

|                                                                                                           | 11        |

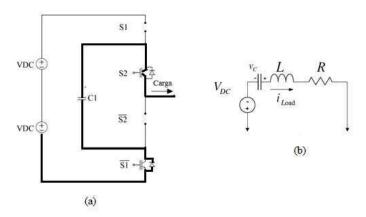

| Figura 12 - Circuito Equivalente S1=0 e S2=1, (a) fluxo de corrente positiva e (b) circuito simplif       | ricado 12 |

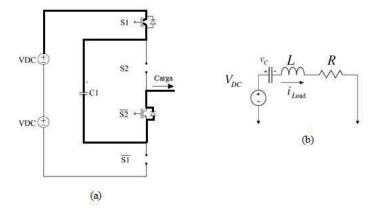

| Figura 13 - Circuito equivalente $S1 = 1$ e $S2 = 0$ , (a) fluxo da corrente positiva e (b) circuito simp | lificado  |

|                                                                                                           | 12        |

| Figura 14 - Circuito equivalente $S1 = 0$ e $S2 = 0$ , (a) fluxo da corrente positiva e (b) circuito simp | lificado  |

|                                                                                                           | 13        |

| Figura 15 - Tensão no capacitor, Comparação da Chave S1 e S2, respectivamente                             | 14        |

| Figura 16 - Método da simetria das portadoras (Kang, 2005)                                                | 15        |

| Figura 17 - Gráfico da ondulação no capacitor versus o fator de potência da carga                         | 15        |

| Figura 18 - Tensão de saída e corrente da carga para f.p. = 0.2                                           | 16        |

| Figura 19 - Tensão de saída e corrente da carga para f.p. = 1                                             | 16        |

| Figura 20 - Gráfico da tensão na saída e tensão no capacitor para carga puramente indutiva                | 16        |

| Figura 21 - Configuração do inversor trifásico usando capacitor flutuante                                 | 18        |

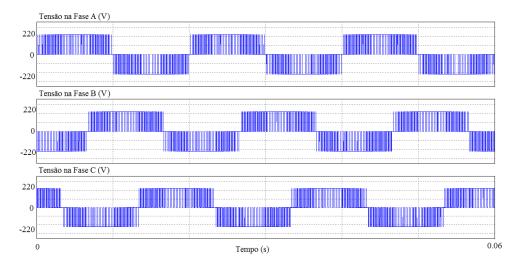

| Figura 22 - Tensões da fase A, fase B e fase C, respectivamente, da saída do inversor                     | 19        |

| Figura 23 - Tensões de linha-a-linha AB, BC e CA, respectivamente, da saída do inversor                   | 19        |

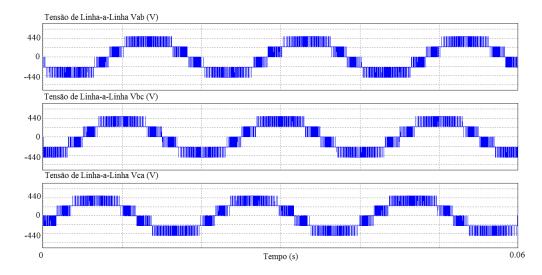

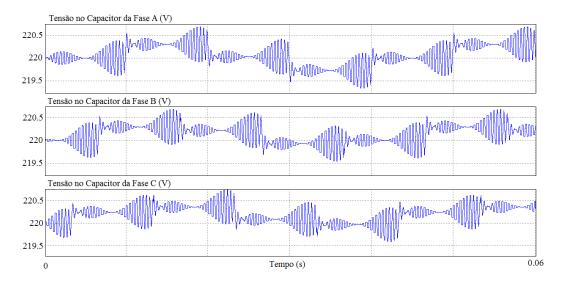

| Figura 24 – Balanço das tensões nos capacitores A, B e C, respectivamente                                 | 19        |

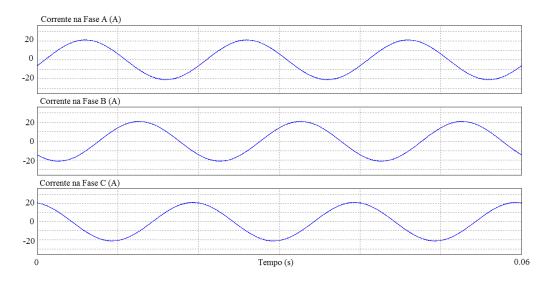

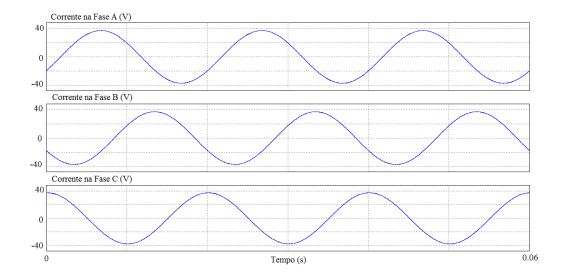

| Figura 25 - Correntes da Fase A, B e C, respectivamente, da saída do inversor                             | 20        |

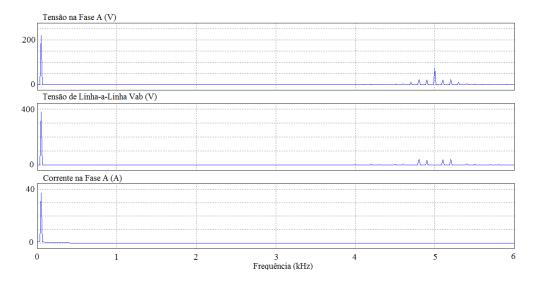

| Figura 26 - Transformada de Fourier da tensão de fase, tensão de linha-a-linha e corrente da saída        | ı do      |

| inversor, respectivamente                                                                                 | 20        |

| Figura 27 - Tensões da fase A, fase B e fase C, respectivamente, da saída do inversor                     | 21        |

| Figura 28 - Tensões de linha-a-linha AB, BC e CA, respectivamente, da saída do inversor                   | 21        |

| Figura 29 - Balanço das tensões nos capacitores A, B e C, respectivamente                                | 21 |

|----------------------------------------------------------------------------------------------------------|----|

| Figura 30 - Correntes da Fase A, B e C, respectivamente, da saída do inversor                            | 22 |

| Figura 31 - Transformada de Fourier da tensão de fase, tensão de linha-a-linha e corrente da saída do    |    |

| inversor, respectivamente                                                                                | 22 |

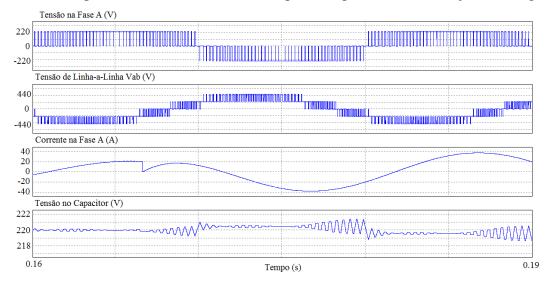

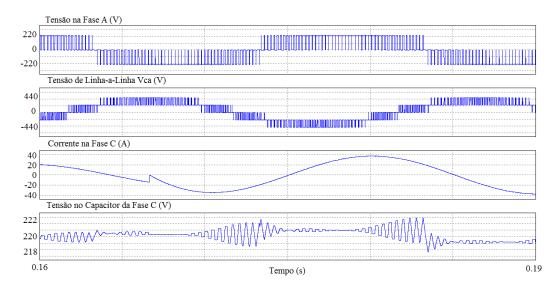

| Figura 32 - Gráfico da tensão de fase, tensão de linha-a-linha e corrente da carga na saída da fase A do |    |

| inversor, respectivamente                                                                                | 23 |

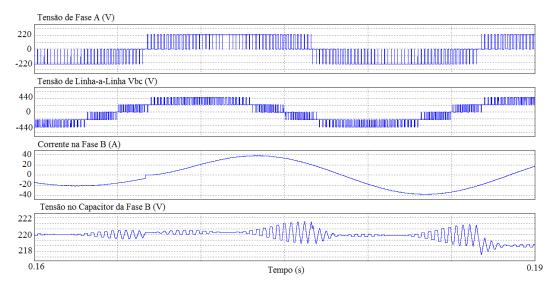

| Figura 33 - Gráfico da tensão de fase, tensão de linha-a-linha e corrente da carga na saída da fase B do |    |

| inversor, respectivamente                                                                                | 24 |

| Figura 34 - Gráfico da tensão de fase, tensão de linha-a-linha e corrente da carga na saída da fase C do |    |

| inversor, respectivamente                                                                                | 24 |

# LISTA DE TABELAS

| Tabela 1 - Tabela da verdade das chaves                    | . ( |

|------------------------------------------------------------|-----|

| Tabela 2 - Tabela da verdade dos estados permitidos        | . ( |

| Tabela 3 - Tabela da verdade do funcionamento do conversor |     |

#### LISTA DE ABREVIATURAS E SIGLAS

BJT (Bipolar Junction Transistor) – Transistor de Junção Bipolar

CA - Corrente Alternada

CC - Corrente Contínua

CFI (Current Fed Inverter) – Inversor Alimentado por Corrente

GTO (Gate Turn-off Thyristor) – Tiristor Desligamento pela porta

IGBT (Insulated Gate Bipolar Transistor) – Transistor Bipolar de Porta Isolada

MCT (MOS Controlled Thyristor) – Tiristor controlado tipo MOS

MOSFET (Metal Oxide Semiconductor Field Effect Transistor) – Transistor de Efeito

de Campo Metal-óxido Semicondutor

NPC (Neutral Point Clamped) – Ponto Neutro Fixo

PWM (Pulse Width Modulation) - Modulação por Largura de Pulso

STI (Static Thyristor Induction) - Tiristor de Indução Estática

THD (Total Harmonic Distorcion) – Distorção Harmônico Total

VFI (Voltage Fed Inverter) – Inversor Alimentado por Tensão

### 1 Introdução

Os conversores CC-CA são conhecidos como inversores. A função de um inversor consiste em converter uma tensão/corrente de entrada CC em uma tensão/corrente de saída CA simétrica, de amplitude e/ou frequência fixa ou variável. Uma tensão variável de saída pode ser obtida variando-se a amplitude da tensão CC de entrada e mantendo-se o ganho do inversor constante. Por outro lado, se a tensão CC de entrada for fixa e não controlável, uma tensão variável de saída pode ser obtida pela variação do ganho do inversor, a qual é normalmente realizada pelo controle da modulação por largura de pulso (do inlês *pulse width modulation – PWM*) dentro do inversor. O ganho do inversor pode ser definido como a relação entre a tensão de saída CA e a tensão de entrada CC (Rashid, 1993).

As formas de onda da tensão de saída de inversores ideais deveriam ser senoidais. Entretanto, as formas de onda de inversores práticos são não-senoidais e contêm certos harmônicos. Para aplicações de baixa e médias potências, tensões de onda quadrada ou quase quadrada podem ser aceitáveis e para aplicações de potência elevada, são necessárias formas de onda senoidais com baixa distorção. Com a disponibilidade de dispositivos semicondutores de potência de alta velocidade, o conteúdo harmônico da tensão da saída pode ser minimizado ou reduzido significativamente pelas técnicas de chaveamento (Rashid, 1993).

Quanto ao número de fase, os inversores mais comuns são de dois tipos: (1) inversores monofásicos e (2) inversores trifásicos. Cada tipo pode usar dispositivos com disparo ou bloqueio controlados (por exemplo, BJTs, MOSFETs, IGBTs, MCTs, GTOs) ou tiristores em comutação forçada, dependendo das aplicações. Esses inversores usam, em geral, sinais de controle PWM para produzir uma tensão CA de saída. Um inversor é chamado inversor alimentado por tensão (do inglês *voltage-fed inverter – VFI*) se tiver sendo alimentado por tensão constante ou alternada; inversor alimentado por corrente (do inglês *current-fed inverter – CFI*), se tiver sendo alimentado por corrente constante ou alternada; e inversor com alimentação CC variável, se a tensão de saída for controlável (Rashid, 1993).

Atualmente, há um crescente interesse nos inversores multi-níveis. Comparados com os inversores convencionais, os inversores de multi-níveis conseguem gerar uma maior potência, possuem eficiência maior e geram menos distorção harmônica na saída. As topologias para multiplo níveis, estratégias para modulação e bom desempenho dos conversores de multiplos níveis vêm sendo estudadas intensamente durantes essas duas últimas decadas. (Ruderman, to appear).

Existem três arquiteturas básicas usadas para os inversores de múltiplos níveis: 1) o inversor com grampeamento por diodos (do inglês *Diode Clamped*), 2) o inversor com capacitor flutuante (do inglês *Flying Capacitor inverter*) e 3) o ponte H em cascata (do inglês *cascade H-bridge*).

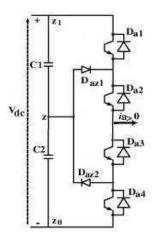

#### 1.1 TOPOLOGIA COM GRAMPEAMENTO POR DIODOS

Os inversores multi-níveis com diodo grampeado operam com diodos de grampeamento e capacitores CC em cascata para produzir formas de onda de tensão de corrente alternada com vários níveis, conforme a Figura 1. O inversor de três níveis do tipo NPC (Neutral Point Clamped, em inglês, Grampeamento do Ponto Neutro, em português), é o preferido pela indústria para aplicações de alta e média potência. Suas principais características são a redução do dv/dt e do THD de suas tensões de saída CA em comparação com os conversores tradicionais, e, mais importante, o inversor pode ser utilizado com alimentações de média tensão para atingir níveis de tensão maiores. Por exemplo, o inversor NPC atinge 6000V usando alimentação com tensão de 4160V (Bin Wu, 2006).

Os inversores com diodo grampeado apresentam algumas vantagens e desvantagens, como indicado a seguir:

#### Vantagens

- Evita a necessidade do uso de filtros para melhorar o sinal quando o número de níveis é alto, gerando baixa distorção harmônica.

- Apresenta alta eficiência pelo fato de todos os dispositivos são chaveados na frequência fundamental.

- Controle do fluxo de potência reativa.

#### Desvantagens

- Um grande número de diodos grampeados é necessário quando usado para gerar um inversor com muitos níveis de tensão.

- É difícil fazer o controle do fluxo da potência ativa para um inversor porque o nível médio CC do capacitor tende a sobrecarregar ou descarregar sem um bom controle e monitoramento.

Figura 1 - Configuração básica de um inversor com diodo grampeado de 3 níveis

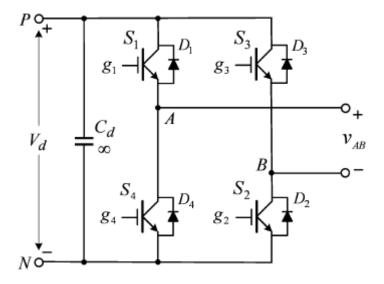

#### 1.2 TOPOLOGIA COM PONTE H EM CASCATA

O inversor multi-nível ponte H em cascata é uma das topologias de inversores mais populares usados em aplicações de alta potência com tensão média. É composto por várias unidades de células ponte H de uma fase (Figura 2). As células de ponte H são normalmente conectadas em cascata no lado CA para operar em médias tensões e alcançar baixa distorção harmônica. Na prática, o número de células em um inversor ponte H em cascata é determinando principalmente pela tensão de operação e pelo custo de fabricação. Por exemplo, em aplicações de média tensão com tensão de linha a linha de 3300V, um inversor de nove níveis de tensão pode ser usado, no qual o inversor ponte H em cascata terá um total de doze células usando componentes de 600V (Bin Wu, 2006).

A principal vantagem da topologia ponte H é que necessita de menos componentes dentre os conversores multi-níveis para atingir o mesmo número de níveis de tensao, deixando, em vários casos, o custo do inversor mais barato. Porém, é necessário isolar a fonte CC em cada célula do inversor, o que limita sua aplicação.

Figura 2 - Célula de um inversor ponte H monofásico.

#### 1.3 TOPOLOGIA COM CAPACITOR FLUTUANTE

O inversor com capacitor flutuante é um inversor de múltiplos níveis modulados por largura de pulsos cuja arquitetura interna garante, automaticamente, o equilíbrio da tensão do capacitor para cargas passivas. Dessa forma, proporciona uma alternativa atraente para o diodo grampeado. Além disso, um único braço do inversor pode ser usado para ambas conversões CC-CC e CC-CA, ao passo que um inversor com diodo grampeado não serve como conversor CC-CC. Isto porque uma corrente CC no clamping point descarrega/carrega o barramento de capacitores CC, fazendo com que não haja equilíbrio de tensão. Mesmo para o caso CC-CA, há o surgimento de oscilações de baixa frequência de tensão no ponto neutro em determinadas condições de operações (Jing Huang, 2006).

Essa arquitetura é relativamente nova, quando comparada ao diodo grampeado e ao ponte H em cascata. Embora a arquitetura com capacitores flutuantes não seja tão comum, possui algumas vantagens distintas sobre a topologia do diodo grampeado, como a ausência de diodos de grampeamento e a capacidade para regular a tensão dos capacitores flutuantes através de estados redundantes mesmo para o número de níveis maiores que três. Ao contrário da arquitetura ponte H, não há necessidade de fonte de tensão isolada. Por essas vantagens, a arquitetura com capacitores flutuantes vem encontrando espaço nas aplicalções industriais (Jing Huang, 2006).

Esses inversores são amplamente usados em aplicações industriais para média e alta potência. Alguns dessas aplicações são: controle de velocidade de motores de indução, fontes de alimentação ininterruptíveis (UPS), variadores de frequência, fontes de alimentação móveis e aquecimento por indução.

Neste trabalho será feito um estudo mais aprofundado da arquitetura do capacitor flutuante. Com essa finalidade, será mostrado como opera o inversor, a técnica de controle de carga/descarga do capacitor flutuante, a faixa de operação do fator de potência para carga e sua implementação, via simulação, da topologia.

### 2 INVERSOR COM CAPACITOR FLUTUANTE

#### 2.1 Modo de operação do conversor

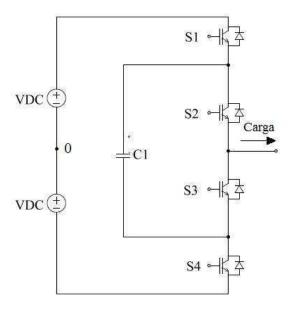

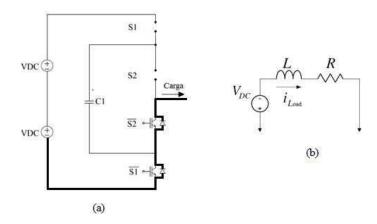

Para analisar o funcionamento do conversor da Figura 3, será utilizado uma tabela da verdade associado a cada chave do circuito, onde Sx = 0 significa que a chave está em aberto, e Sx = 1 a chave está fechada, onde x é a chave em questão.

Tabela 1 - Tabela da verdade das chaves

| <b>S</b> 1 | S2 | <b>S</b> 3 | S4 | Tensão na carga |

|------------|----|------------|----|-----------------|

| 0          | 0  | 0          | 0  | X               |

| 0          | 0  | 0          | 1  | X               |

| 0          | 0  | 1          | 0  | X               |

| 0          | 0  | 1          | 1  | -VDC            |

| 0          | 1  | 0          | 0  | X               |

| 0          | 1  | 0          | 1  | 0               |

| 0          | 1  | 1          | 0  | X               |

| 0          | 1  | 1          | 1  | X               |

| 1          | 0  | 0          | 0  | X               |

| 1          | 0  | 0          | 1  | X               |

| 1          | 0  | 1          | 0  | 0               |

| 1          | 0  | 1          | 1  | X               |

| 1          | 1  | 0          | 0  | +VDC            |

| 1          | 1  | 0          | 1  | +VDC<br>X       |

| 1          | 1  | 1          | 0  | X               |

| 1          | 1  | 1          | 1  | X               |

Figura 3 - Topologia do Capacitor Flutuante

Pode-se ver, na Tabela 1, X respresenta alguns estados não permitidos no circuito porque podem curto-circuitar a fonte de alimentação, ou também, por deixar a carga flutuando, tornando esse estado sem uso. Assim é possível simplificar a tabela, como mostra a Tabela 2.

Tabela 2 - Tabela da verdade dos estados permitidos

| <b>S</b> 1 | S2 | <b>S</b> 3 | S4 | Tensão na carga |

|------------|----|------------|----|-----------------|

| 0          | 0  | 1          | 1  | -VDC            |

| 0          | 1  | 0          | 1  | 0               |

| 1          | 0  | 1          | 0  | 0               |

| 1          | 1  | 0          | 0  | +VDC            |

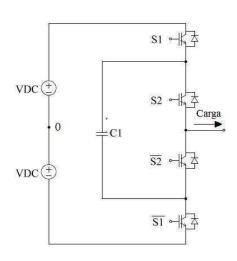

Através da tabela da verdade simplificada é possível perceber que a chave S1 nunca ligará no mesmo tempo que a chave S4 e que a chave S2 não ligará no mesmo tempo que a chave S3, assim pode-se simplificar ainda mais o controle da chave fazendo com que S4 seja o complementar de S1 e que S3 seja o complementar de S2, de acordo com a Figura 4 e a Tabela 3.

Tabela 3 - Tabela da verdade do funcionamento do conversor

| <b>S</b> 1 | S2 | Tensão na Carga |

|------------|----|-----------------|

| 0          | 0  | -VDC            |

| 0          | 1  | 0               |

| 1          | 0  | 0               |

| 1          | 1  | +VDC            |

Figura 4 - Conversor utilizando Capacitor Flutuante

Sendo assim, é possível expressar a equação da tensão de saída do inversor em função de *x*:

$$V_{A0} = S_1 (V_{DC} - V_{C1}) + S_2 (V_{C1}) - V_{DC} (x)$$

sendo  $V_{C1} = V_{DC}$  no estado permanente de funcionamento.

#### 2.2 TÉCNICA DE CONTROLE PWM UTILIZADA

Foi utilizada uma técnica de controle das chaves de modo a que fosse possível garantir um controle de tensão no capacitor onde não haveria variação na carga do capacitor em regime permanente, ou seja, haveria variação quase nula na tensão do capacitor (Sang-Gil Lee, 2001).

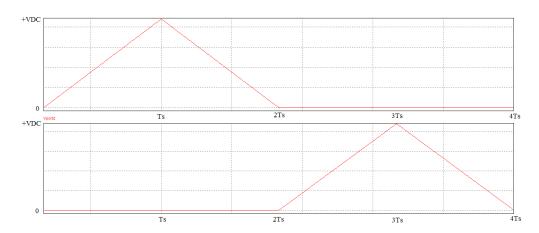

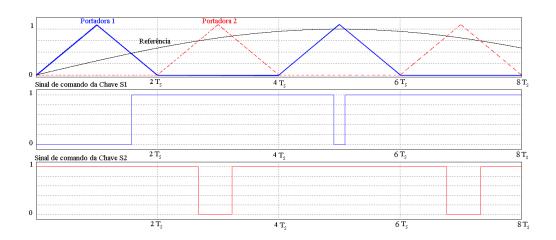

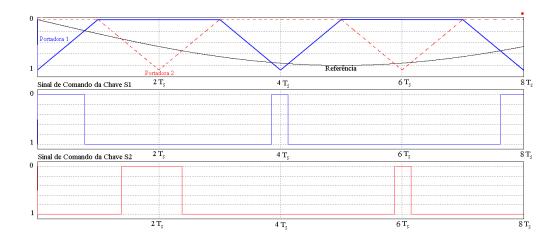

Essa técnica faz com que o chaveamento aconteça uma vez a cada 2(N-1) Ts, onde N é o número de níveis do inversor, e esse chaveamento ocorre somente por um período de tempo de no máximo Ts. Para tal, foram utilizadas duas portadoras, uma para cada par de chave onde no ciclo positivo da onda senoidal de referência é atribuída uma forma de onda e no ciclo negativo da senóide de referência, uma onda de forma diferente da primeira (Sang-Gil Lee, 2001). A Figura 5 mostra a forma de onda da portadora 1 e 2 no ciclo positivo da referência e a Figura 6 mostra a forma de onda no ciclo negativo.

Figura 5 - Forma de onda da portadora 1 e 2, respectivamente, no ciclo positivo da referência.

Figura 6 - Forma de onda da portadora 1 e 2, respectivamente, no ciclo negativo da referência.

Para melhor entedimento, será exemplificado o método com um índice de modulação de amplitude igual a 0.90 (amplitude da triagular igual a 220 V e amplitude da referência igual a 200) e índice de modulação de frequência igual a 10 (frequência da triangular igual a 500 Hz e frequência da referência igual a 50 Hz).

É visto na Figura 7, durante o ciclo positivo da referência, num periodo de tempo igual 4 T<sub>s</sub>, há o chaveamento somente uma vez de cada uma das chaves e podendo atingir um tempo máximo de permanência do estado de T<sub>s</sub> segundos. E também, na Figura 8, durante o ciclo negativo da referência, há uma única variação de estado das chaves, analogamente ao ciclo positivo. Isso faz com que o capacitor seja carregado ou descarregado um pouco durante esse pequeno intervalo de tempo e passe o resto flutuando no circuito. Esse ponto será melhor detalhado no tópico seguinte. Todos os valores no gráfico estão normalizados para os valores ditos acima.

Figura 7 - Sinais das portadoras em comparação com a referência, sinais de comando enviados para chave S1 e S2, respectivamente, para o ciclo positivo da referência.

Figura 8 - Sinais das portadoras em comparação com a referência [1], sinais de comando enviados para chave S1 [2] e S2 [3] para o ciclo negativo da referencia.

#### 2.3 CARREGAMENTO E DESCARREGAMENTO DO CAPACITOR

Para gerar os três níveis de tensão essa topologia usa um capacitor ligado após a chave S1 até a chave complementar de S1 para gerar uma tensão contrária a tensão de alimentação de acordo com a ligação das chaves, gerando a tensão nula.

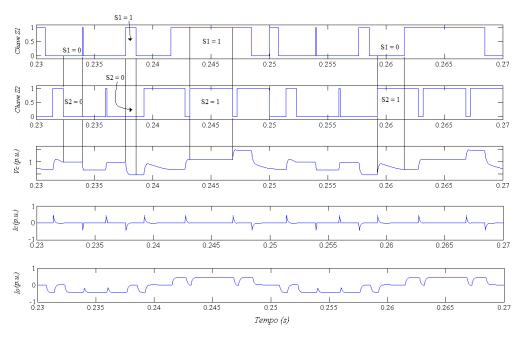

De acordo com a tabela 3, o conversor gera três níveis diferentes: +VDC, 0 e – VDC, no qual depende da sequência em que as chaves S1 e S2 são ligadas ou desligadas. Para mostrar o carregamento e o descarregamento do capacitor, será usado o exemplo passado para auxiliar na análise do problema.

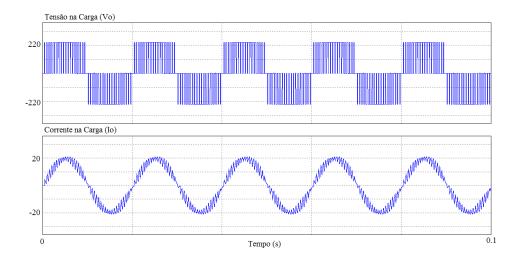

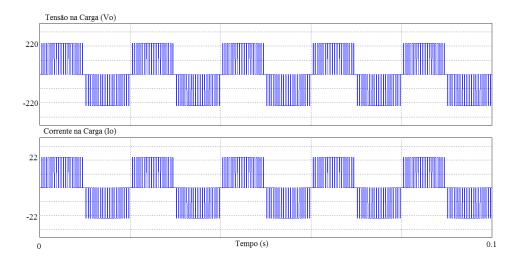

O capacitor pode permanecer em 3 estados diferentes no circuito: (1) quando está flutuando no circuito, (2) quando está ligado de forma que está a carregar e (3) quando está ligado de forma a descarregar. A Figura 9 mostra o sinal de controle das chaves, para uma carga predominantemente resistiva, em comparação com o estado em que o capacitor se encontra naquele determinado momento no circuito para uma carga predominatemente resitiva. Também mostra a corrente no capacitor e na carga. A Figura 10 mostra também os 3 estados diferentes, só que nesse caso para a situação de uma carga mais indutiva. Percebe-se que a forma de onda da corrente de saída se torna mais senoidal, ao contrário da Figura 9, onde é possível percerber que a corrente de saída apresenta uma forma mais quadrada. Os valores dos gráficos abaixo estão todas normalizados: tensão de 220V e corrente de 10A.

Figura 9 - Gráfico do sinal de comando da chave S1 e S2, tensão no capacitor, corrente no capacitor e na carga, respectivamente, para carga predominantemente resistiva.

Figura 10 - Gráfico do sinal de comando da chave S1 e S2, tensão no capacitor, corrente no capacitor e na carga, respectivamente, para carga predominantemente indutiva.

#### 2.3.1 ETAPA 1: QUANDO S1 = 1 E S2 = 1:

Quando S1 e S2 estão fechadas, o capacitor estará flutuando no sistema mantendo a tensão carregada, e não há corrente passando no capacitor, com isso não há carregamento nem descarregamento no capacitor, e a carga sofrerá influência direta da fonte de alimentação, ou seja, tensão na carga igual a +VDC, conforme a Figura 11.

Figura 11 - Circuito equivalente S1 = 1 e S2 = 0, (a) fluxo de corrente positiva e (b) circuito simplificado

#### 2.3.2 ETAPA 2: QUANDO S1 = 0 E S2 = 1 OU S1 = 1 E S2 = 0;

Quando S1 está desligado e S2 está ligado, Figura 12, o capacitor estará inserido no circuito sofrendo influência da fonte de alimentação, com tensão –VDC, e passando uma corrente por ele igual a corrente de carga, com isso, o capacitor começa a

carregar/descarregar, dependendo do sentindo que a corrente esteja passando. Quando S1 está ligado e S2 está desligado, Figura 13, o capacitor está quase da mesma forma da situação anterior, com diferença de que ele está diretamente polarizado, tensão igual +VDC, do mesmo jeito que o estado passado, a corrente que está passando no momento, vai dizer se o capacitor está em carregamento ou descarregamento.

Figura 12 - Circuito Equivalente S1=0 e S2=1, (a) fluxo de corrente positiva e (b) circuito simplificado

Figura 13 - Circuito equivalente S1 = 1 e S2 = 0, (a) fluxo da corrente positiva e (b) circuito simplificado

#### 2.3.3 ETAPA 3: QUANDO S1 = 0 E S2 = 0;

Quando S1 e S2 estão abertas, o capacitor flutua no sistema, ou seja, mantendo a tensão, da mesma forma que na primeira etapa, e não há corrente passando no capacitor. Com isso, não há carregamento nem descarregamento no capacitor, e a carga sofrerá influência direta da fonte de alimentação porém de forma a polarizar inversamente a carga; ou seja, tensão na carga igual a  $-V_{DC}$ , conforme Figura 14.

Figura 14 - Circuito equivalente S1 = 0 e S2 = 0, (a) fluxo da corrente positiva e (b) circuito simplificado

#### 2.4 LIMITAÇÃO DA TÉCNICA PWM E FAIXA DE OPERAÇÃO DO

#### **INVERSOR**

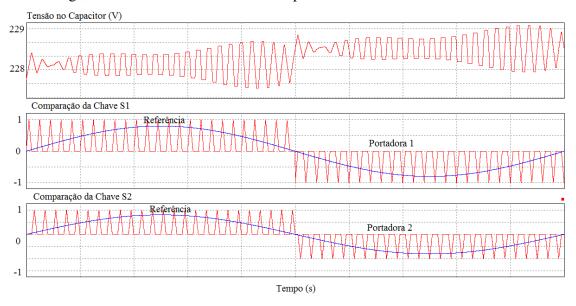

Utilizando a técnica mostrada anteriormente, não se considera a influência da intensidade da corrente que passa pela carga. Isso acontece porque essa técnica não consegue fazer o balanço de tensão perfeitamente e isso se torna mais evidente quando utilizado o inversor com correntes acima de 5 amperes. A Figura 15 evidencia, carga de 10 ohms e 10 mH com a amplitude de corrente de 20 amperes em regime permanente, a ineficiência da técnica em fazer com que o capacitor fica mais tempo em carga do que em descarga, não balanceando a tensão no capacitor.

Figura 15 - Tensão no capacitor, Comparação da Chave S1 e S2, respectivamente.

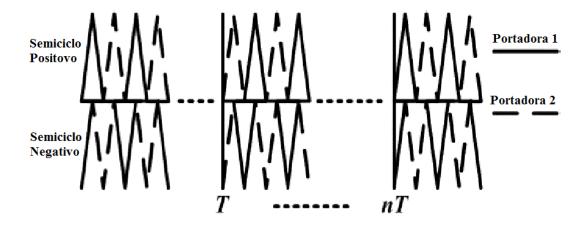

É possível corrigir essa limitação, utilizando o método da simetria das portadoras, que consiste numa pequena modificação no período da portadora para que o balanço da tensão no capacitor seja alcançado mesmo para altos valores de corrente na carga (Kang, 2005). A modificação proposta é feita trocando a forma da onda da portadora 1 pela forma de onda da portadora 2, e vice-versa, como ilustra a Figura 16, fazendo com que a carga extrapolada no capacitor em um período, seja descarregado no período seguinte, e assim por diante.

Figura 16 - Método da simetria das portadoras (Kang, 2005)

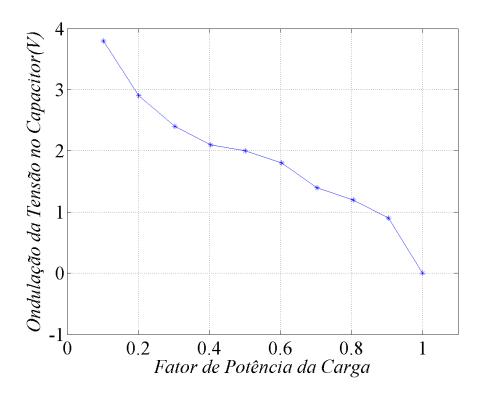

A Figura 17 mostra o gráfico da variação de tensão do capacitor no regime permanente versus o fator de potência da carga para sua faixa de operação e as Figuras 18 e 19 mostram o gráfico da saída do inversor para os fatores de potência 0.1 e 1, respectivamente, obtidos através de simulação utilizando uma carga com resistência fixa em 10 ohm, frequência da portadora 5 kHz e frequência fundamental de 50 Hz.

Figura 17 - Gráfico da ondulação no capacitor versus o fator de potência da carga

Figura 18 - Tensão de saída e corrente da carga para f.p. = 0.2

Figura 19 - Tensão de saída e corrente da carga para f.p. = 1

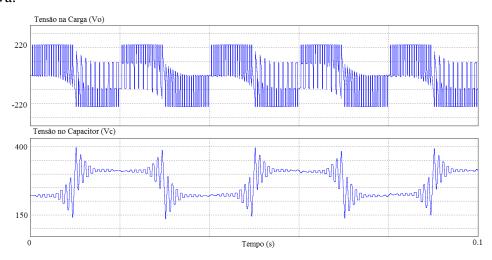

A Figura 20 mostra a tensão de saída do inversor para a carga puramente indutiva.

Figura 20 - Gráfico da tensão na saída e tensão no capacitor para carga puramente indutiva

Essa técnica modificada não opera com cargas puramente indutivas, podendo assim o inversor com capacitor flutuante operar desde cargas resistivas até cargas predominantemente indutiva

O motivo pelo qual não é possível usar essa estratégia para cargas puramente indutivas é pelo fato da ineficiência para balancear o capacitor nesse ponto de operação.

O balanço de tensão do capacitor não é alcançado, como mostra a figura, no regime permamente, o capacitor ondula bastante, chegando a ter ondulações na tensão de aproximadamente 250V, desconfigurando os níveis de tensão na saída e gerando níveis diferente de 0V e destruindo uma das grandes vantagens dessa topologia que é a redundância na geração do nível zero.

## 3 ESTUDO DE CASO ATRAVÉS DE SIMULAÇÃO

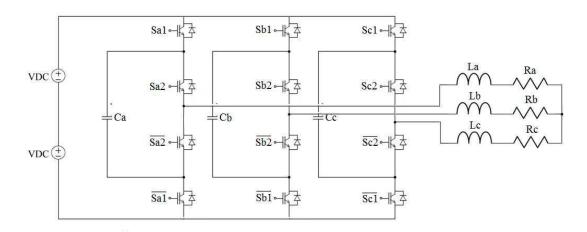

Utilizando todo o fundamento teórico mostrado nos capítulos anteriores, serão feitas a implementação virtual através do programa *Psim 9.0* de um inversor trifásico com dois tipos de cargas diferentes, segue as especificações:

$$V_{dc} = 220V;$$

$$C_a = C_b = C_c = 2200 \mu F$$

;

Frequência de chaveamento = 5 kHz;

Frequência da referência = 50 Hz;

Índice de modulação = 0.95;

- 1) Carga Ra = Rb = Rc =  $10 \Omega$  e La = Lb = Lc = 10 mH);

- 2) Carga Ra = Rb = Rc =  $5 \Omega$  e La = Lb = Lc = 10 mH);

Figura 21 - Configuração do inversor trifásico usando capacitor flutuante

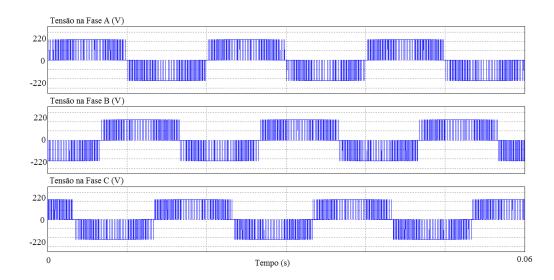

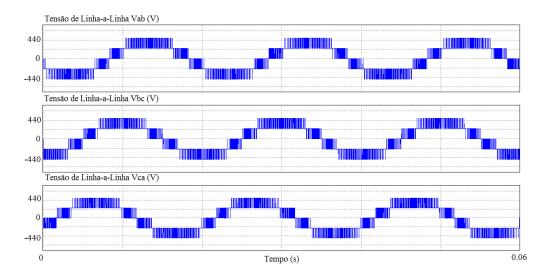

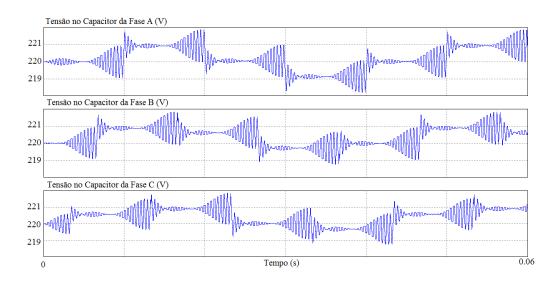

Os resultados apresentados a seguir estão relacionados com a operação do inversor para a carga de  $10~\Omega$  e 10~mH, o sistema já se inicia com os capacitores carregados com 220V, ou seja, em regime permanente. A Figura 22~ilustra as três tensões de fase da saída do inversor, a Figura 23~mostra as três tensões de linha-a-linha da saída do inversor, a Figura 24~apresenta as três correntes da saída do inversor e a Figura 25~apresenta a forma de onda das correntes na saída do inversor para as três fases e a Figura 26~mostra a transformada de Fourier das tensões de fase, tensões de linha-a-linha e correntes da saída do inversor.

Figura 22 - Tensões da fase A, fase B e fase C, respectivamente, da saída do inversor

Figura 23 - Tensões de linha-a-linha AB, BC e CA, respectivamente, da saída do inversor

Figura 24 – Balanço das tensões nos capacitores A, B e C, respectivamente

Figura 25 - Correntes da Fase A, B e C, respectivamente, da saída do inversor

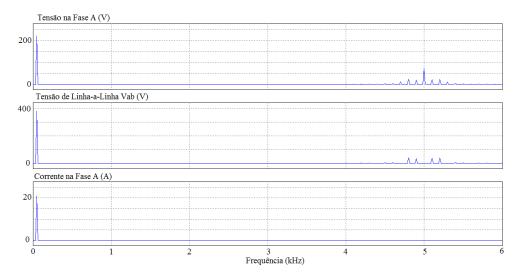

Figura 26 - Transformada de Fourier da tensão de fase, tensão de linha-a-linha e corrente da saída do inversor, respectivamente

Também nas mesmas condições da carga de  $10~\Omega$  e 10~mH, as Figuras 27, 28, 29, 30 e 31~mostram os resultados da simulção para a carga de  $5~\Omega$  e 10~mH.

Figura 27 - Tensões da fase A, fase B e fase C, respectivamente, da saída do inversor

Figura 28 - Tensões de linha-a-linha AB, BC e CA, respectivamente, da saída do inversor

Figura 29 - Balanço das tensões nos capacitores A, B e C, respectivamente

Figura 30 - Correntes da Fase A, B e C, respectivamente, da saída do inversor

Figura 31 - Transformada de Fourier da tensão de fase, tensão de linha-a-linha e corrente da saída do inversor, respectivamente

Mesmo com cargas diferentes, a tensão de fase e de linhas são iguais nas duas cargas, o que difere são as correntes que são menores na carga de  $10~\Omega$  do que na carga de  $5~\Omega$ , o que era previsível já que a corrente é dada através da razão entre a tensão e a resistência, e na ondulção da tensão no capacitor que também é menor na carga de  $10~\Omega$  do que na de  $5~\Omega$ , isso porque uma maior corrente vai gerar uma maior ondulação.

No gráfico das tensões de linha-a-linha, é possível perceber que a tensão de saída apresenta 5 níveis, isso acontece devido ao fato das tensões de fase serem defasadas em 120 graus, assim, quando feita a diferença entre as fases, há o surgimento desses 2 níveis, no caso de um inversor de 3 níveis. Quanto maior for o número de

níveis da tensão de fase, maior será o acréscimo de níveis na tensão de linha-a-linha, por exemplo, para um inversor de 5 níveis, sua tensão de linha-a-linha apresenta 9 níveis.

Assim, observa-se que a estratégia mostrada nesse trabalho é bem eficaz no balanço de tensão dos capacitores para a faixa de fator de potência aqui mostrada, e na simulação, é possível ver que a variação de tensão no capacitor gira em torno de mais ou menos 1V para a carga de  $10~\Omega$  e mais ou menos 2V para a carga de  $5~\Omega$ , o que é uma variação bastante pequena considerando que a tensão de operação do sistema é de 220V. Também é possível ver que a corrente de saída do inversor apresenta uma baixa oscilação nas duas cargas, isso porque elas são bastante indutivas, deixando-as quase que perfeitamente senoidais. No gráfico da transformada de Fourier, os harmônicos só começam a ser vistos em frequências muito altas, na faixa de  $5~\mathrm{kHz}$ , o que é um ótimo resultado, já que é bastante longe da frequência de operação o qual o inversor foi projetado ( $50~\mathrm{Hz}$ ).

Foi feito também um teste de transição de cargas, onde em um determinado momento, a carga de  $10~\Omega$  e 10~mH é substituida para uma carga de  $5~\Omega$  e 10~mH. A Figura  $31,\,32$  e 33~mostram a tensão na carga, tensão de linha-a-linha, corrente na carga e tensão no capacitor das três fases durante o período que ocorre a transição das cargas.

Figura 32 - Gráfico da tensão de fase, tensão de linha-a-linha e corrente da carga na saída da fase A do inversor, respectivamente

Figura 33 - Gráfico da tensão de fase, tensão de linha-a-linha e corrente da carga na saída da fase B do inversor, respectivamente

Figura 34 - Gráfico da tensão de fase, tensão de linha-a-linha e corrente da carga na saída da fase C do inversor, respectivamente

A técnica utilizada também se mostrou bastante robusta no teste de transição de cargas. Pelos resultados apresentados acima, é possível ver que durante a transição houve disturbios nas correntes de fase mas foi rapidamente estabilizado, voltando a funcionar normalmente. Além disso, não houve alteração nas tensões de saída e nem na carga dos capacitores.

#### 4 CONCLUSÃO

Após uma revisão das várias vantagens, em relação a um inversor convencional, de alguns inversores multi-níveis que estão sendo bastante estudados atualmente, foi realizada uma pesquisa com o foco na topologia de inversor utilizando capacitores flutuantes, mostrando as vantagens e desvantagens de seu uso. Nesse contexto, foi estudada, de forma simples e objetiva, sua implementação utilizando a técnica baseada na portadora para controle da tensão dos capacitores, que é a principal preocupação com relação a essa topologia. Uma das vantagens dessa técnica é a redundância de configuração cujo uso permite em gerar o nível zero, pois durante esse estado o capacitor pode carregar/descarregar sem mudar o valor da saída, e garantir que as chaves só mudem de estado uma vez por ciclo, que por sua vez, geram menores perdas por chaveamento.

Entretanto, a técnica utilizada inicialmente é incapaz de operar com cargas que necessitam de correntes altas, isso por causa da ineficiência no balanço da tensão no capacitor pois não foi considerado a influência da corrente na carga/descarga do capacitor. Por esta razão foi estudada uma variação da técnica inicialmente proposta para sanar essa limitação na técnica. A simulação dessa segunda técnica que utiliza a simetria da portadora, mostrou sua eficácia para uma longa faixa de operação de fator de potência da carga, que vai desde uma carga com fator de potência 0,1 até cargas puramente resistiva (f.p. = 1).

Pode-se dizer que o estudo na área de inversores multi-níveis só está começando e que há muito a ser estudado com relação à concepção de formas de conversão CC-CA com a menor produção de harmônicos possível.

#### **BIBLIOGRAFIA**

HUANG, J.; CORZINE, K.A.; Extended Operation of Flying Capacitor Multilevel Inverters. *IEEE Transactions on power electronics*, v. 21, p. 140-147, 2006.

KANG, D.; LEE, B.; JEON, J.; KIM, T.; HYUN, D.; A Symmetric Carrier Technique of CRPWM for Voltage Balance Method of Flying-Capacitor Multilevel Inverter. *IEEE Transactions on Industrial Electronics*, v. 52, p. 879-888, 2005.

LAI, J.; Peng, F.Z.; Multilevel Converters – A New Breed of Power Converters. *Industry Applications Conference*, v. 3, p. 2348-2356, 1995.

LEE, S.; KANG D.; LEE, Y.; HYUN, D.; The carrier-based PWM method for voltage balance of flying capacitor multilevel inverter. *Power Electronics Specialists Conference*, Vancouver, v. 1, p. 126–131, 2001.

LIANG, Y.; NWANKPA, C. 0.; A Power Line Conditioner Based on Flying capacitor multilevel Voltage Source Converter with Phase Shift SPWM. *IEEE Industry Applications Meeting*, Vol. 4, pp. 2337-2343,1999.

MEYNARD, T. A.; FOCH, H.; Multi-level conversion: high voltage choppers and voltage-source inverters. *Proc. IEEE Power Electronics Specialist Conf.*, pp. 397–403, 1992.

MEYNARD, T. A.; FOCH, H.; THOMAS, P.; COURAULT, J.; JAKOB, R.; NAHRSTAEDT, M.; Multicell converters: basic concepts and industry applications. *IEEE Trans. Ind. Electron.*, vol. 49, no. 5, pp. 955–964, 2002.

RASHID, M. H.. Eletrônica de Potência: Circuitos, Dispositivos e Aplicações. Segunda Edição. Prentice-Hall, Inc, 1993, p. 436-497.

RUDERMAN, A.; REZNIKOV, B.; MARGALIOT, M.; Analysis of a Flying Capacitor Converter: A Switched Systems Approach. *Int. J. Circuit Theory Applications*, to appear.

RUDERMAN, A.; REZNIKOV, B.; MARGALIOT, M.; Simple analysis of a flying capacitor converter voltage balance dynamics for DC modulation. *Power Eletronics and Motion Control Conference*, Poznan, p. 260-267, 2008.

WU, Bin. High-power converters and AC drives. Hoboken: IEEE Press, 2006. 333 pp.