# Universidade Federal de Campina Grande

## Centro de Engenharia Elétrica e Informática

Curso de Graduação em Engenharia Elétrica

JULIANO COSTA LEAL DA SILVA

CONVERSOR ANPC (ACTIVE NEUTRAL POINT CLAMPED) DE TRÊS NÍVEIS: SIMULAÇÕES E RESULTADOS EXPERIMENTAIS COM MODULAÇÃO PWM.

Campina Grande, Paraíba Fevereiro de 2013

#### JULIANO COSTA LEAL DA SILVA

# CONVERSOR ANPC (ACTIVE NEUTRAL POINT CLAMPED) DE TRÊS NÍVEIS: SIMULAÇÕES E RESULTADOS EXPERIMENTAIS COM MODULAÇÃO PWM.

Trabalho de Conclusão de Curso submetido à Unidade Acadêmica de Engenharia Elétrica da Universidade Federal de Campina Grande como parte dos requisitos necessários para a obtenção do grau de Bacharel em Ciências no Domínio da Engenharia Elétrica.

Área de Concentração: Eletrônica Industrial

Orientador:

Professor Maurício B. R. Corrêa, D. Sc.

Campina Grande, Paraíba Fevereiro de 2013

#### JULIANO COSTA LEAL DA SILVA

# CONVERSOR ANPC (ACTIVE NEUTRAL POINT CLAMPED) DE TRÊS NÍVEIS: SIMULAÇÕES E RESULTADOS EXPERIMENTAIS COM MODULAÇÃO PWM.

Trabalho de Conclusão de Curso submetido à Unidade Acadêmica de Engenharia Elétrica da Universidade Federal de Campina Grande como parte dos requisitos necessários para a obtenção do grau de Bacharel em Ciências no Domínio da Engenharia Elétrica.

Área de Concentração: Eletrônica Industrial

Aprovado em / /

Professor Avaliador Universidade Federal de Campina Grande Avaliador

Professor Maurício B. R. Corrêa, D. Sc. Universidade Federal de Campina Grande Orientador, UFCG

## **AGRADECIMENTOS**

Agradeço às forças do universo que me guiaram até o presente momento.

Agradeço à minha mãe Vera Lucia por não medir esforço em me ver feliz.

Agradeço ao meu pai Marcelino José pela paixão à razão.

Agradeço ao meu irmão João Marcelo pelo amor presente em seus conselhos.

Agradeço à minha namorada Roana d'Ávila por ser minha companheira desde o primeiro dia que nos conhecemos.

Ao meu primo Gabriel Costa pelo exemplo de disciplina e dedicação.

Aos professores Edison Roberto e Mauricio BR Côrrea pela paciência e positividade transmitidas.

A Adail e Tchai pela prontidão em todos os momentos.

Aos alunos da pós-graduação no LEIAM: João Helder, Antonio Isaac, Abinadabe, Luciano Barros, Ítalo Roger, Vagner Fonseca, Marcos Aurelio pela ajuda nas dúvidas inerentes ao aprendizado.

Agradeço também aos meus amigos Dorival, Bruno, Alone, Fausto. Ana Clara, Rubem, Marconni, Felipe, Pablo, Carlos Ângelo, Ruy, Victor, Lucas, Ravi, Bruno, Claudio, Marlo por todos os momentos felizes vividos.

Enfim, agradeço a todos que de alguma forma, passaram pela minha vida e contribuíram para a construção de quem sou hoje.

"Seja você a mudança que tanto quer ver no mundo."

Mahatma Gandhi.

## **RESUMO**

O conversor de três níveis ANPC (Active Neutral Point Clamped) foi proposto em 2001 como uma versão alternativa ao conversor de três níveis NPC (Neutral Point Clamped) criado nos anos 80 [1]. O NPC oferece uma solução relativamente simples para extensão das faixas de tensão e potência existentes nos conversores convencionais de dois níveis, ainda contribuindo para a melhoria na qualidade do sinal de saída. Atualmente o NPC é largamente utilizado em aplicações de alta/média potência tais como: acionamento de máquinas, conversores de energias renováveis, sistemas de distribuição entre outros. Um fator importante a ser considerado no NPC, diz respeito às perdas desiguais sobre os dispositivos de potência. Com isso pode-se considerar que os estresses sobre os semicondutores no NPC são desiguais, havendo maior dissipação em alguns dispositivos. Este fato acaba por limitar a frequência de chaveamento e a potência de saída do conversor. De modo a superar a distribuição desigual das perdas neste conversor, foi proposta a topologia ANPC, onde os diodos de grampeamento do NPC foram substituídos por chaves bidirecionais. Deste modo, as chaves adicionais do ANPC irão possibilitar mais estados de chaveamento e comutações se comparado ao NPC. Este aumento de estados de chaveamento gera um maior grau de liberdade na escolha da estratégia de modulação. De fato, a possibilidade de mais de um estado de chaveamento para atingir o estado O é o que torna possível uma distribuição mais igualitária das perdas sobre os dispositivos de potência no ANPC. Para tanto, se faz necessário o estudo das técnicas de modulação aplicadas ao conversor ANPC de modo que a solução mais eficiente se torne aplicável. Este trabalho de conclusão de curso propõe a obtenção e análise de resultados experimentais do conversor ANPC montado no Laboratório de Eletrônica Industrial e Acionamentos de Máquinas (LEIAM), pertencente ao departamento de engenharia elétrica da UFCG. Para a obtenção dos resultados experimentais, se faz necessária a simulação e análise dos resultados da topologia ANPC através do software PSim-versão 9.0.3 bem como a configuração do DSP modelo eZdsp TMS320F28335 para ser utilizado na geração dos pulsos de disparo/bloqueio das chaves.

Palavras-chave: Conversor ANPC de três níveis, técnicas de modulação PWM, DSP.

#### **ABSTRACT**

The three-level ANPC converter (Neutral Point Clamped Active) was proposed in 2001 as an alternative version of the converter three-level NPC (Neutral Point Clamped) created in the 80s [1]. The NPC provided a relatively simple solution for extending the ranges of voltage and power in conventional two levels, although contributing to an improvement in the quality of the output signal. Currently the NPC is widely used in applications of high/medium power such as driving machines, converters, renewable energy distribution systems among others. An important factor to be considered in the NPC, concerns about the unequal losses on the power devices. Thus we can consider that the stresses on the semiconductor NPC are unequal making some devices more heated than others. This factor ultimately limits the switching frequency and the output power converter. In order to overcome the unequal distribution of losses in converter was proposed ANPC topology, where the NPC clipping diodes were replaced by bidirectional switches. Thus, the additional switches in ANPC will enable more switching states and switching operations compared to NPC. This increase of switching states generates a greater degree of freedom in choosing the appropriate modulation strategy. In fact, the possibility of more than one switching state to attain O is what makes possible a more equitable distribution of losses on the power devices in the ANPC. For this purpose, it is necessary to study the modulation techniques applied in the converter ANPC to the most efficient solution becomes applicable. This course conclusion work proposes the acquisition and analysis of experimental results ANPC converter mounted in the Laboratory of Industrial Electronics and Drives Machines (LEIAM) belonging to the department of electrical engineering of UFCG. To obtain the experimental results, it is necessary to simulate and analyze the results of ANPC topology through PSIM software version 9.0.3, as well as the configuration of DSP TMS320F28335 eZdsp model to be used in the generation of switching states

**Keywords:** ANPC Three level converter, PWM strategies, DSP.

# LISTA DE ILUSTRAÇÕES

| rigura 1 - Braços genericos de conversores maitimiven.(a) Braço de um conversor com dois invers,(b)         |      |

|-------------------------------------------------------------------------------------------------------------|------|

| Braço de um conversor de três níveis;(c) Braço de um conversor com n níveis.                                |      |

| Figura 2: Conversor multinivel com capacitores flutuantes de três e quatro níveis respectivamente           |      |

| Figura 3 Conversor convencional em cascata de cinco níveis                                                  | 18   |

| Figura 4: Conversor NPC de três níveis convencional                                                         | 19   |

| Figura 5: Conversor ANPC de três níveis.                                                                    |      |

| Figura 6: Estado de condução O para uma corrente positiva: (a) pelo caminho superior; (b) pelo camir        | nho  |

| inferior.                                                                                                   |      |

| Figura 7: Estratégia PWM-1; (a) Portadora e tensão de referencia para geração dos níveis positivos          |      |

| Figura 8 Estratégia PWM-2. (a) Portadora e tensão de referencia para geração dos níveis positivos           |      |

| Figura 9: Estratégia PWM-3. (a) Portadoras e tensão de referencia para geração dos níveis positivos;        | 29   |

| Figura 10: Foto do DSP modelo eZdsp TMS320F2833                                                             |      |

| Figura 11: Resultados de simulação para ANPC com estratégia de PWM-1 com carga resistiva;                   | 32   |

| Figura 12: Resultados de simulação para ANPC com estratégia de PWM-1 com carga indutiva;                    | 33   |

| Figura 13: Sinais de gatilho. (a) T1a; (b) T1ca; (c) T2a; (d) T2ca; (e) T3a; (f) T3ca                       | 34   |

| Figura 14: Resultados de simulação para ANPC com estratégia de PWM-2 com carga resistiva;                   | 35   |

| Figura 15: Resultados de simulação para ANPC com estratégia de PWM-2 com carga indutiva;                    | 36   |

| Figura 16: Sinais de gatilho. (a) T1a; (b) T1ca; (c) T2a; (d) T2ca; (e) T3a; (f) T3ca                       | 37   |

| Figura 17: Resultados de simulação para ANPC com estratégia de PWM-3 com carga resistiva;                   | 38   |

| Apesar de não ser evidente a diferença dos resultados desta técnica com relação às anteriores, nesta        |      |

| estratégia de modulação há o dobro de transições de estados de comutação em cada período de                 |      |

| chaveamento, como pode ser visto na Figura 9. Isto é explicado pelo fato de nesta estratégia, serem         |      |

| utilizadas as quatro sequencias de chaveamento possível para gerar o estado O representadas por             |      |

| 01-, 02-, 01+, 02 +. Como será visto adiante, este fato não altera em grandes proporções o conteú           | ido  |

| harmônico dos sinais analisados.                                                                            | 38   |

| Figura 19: Resultados de simulação para ANPC com estratégia de PWM-3 com carga indutiva;                    | 39   |

| Figura 20: Sinais de gatilho. (a) T1a; (b) T1ca; (c) T2a; (d) T2ca; (e) T3a; (f) T3ca                       |      |

| Figura 21: Diagrama esquemático da montagem realizada.                                                      | 42   |

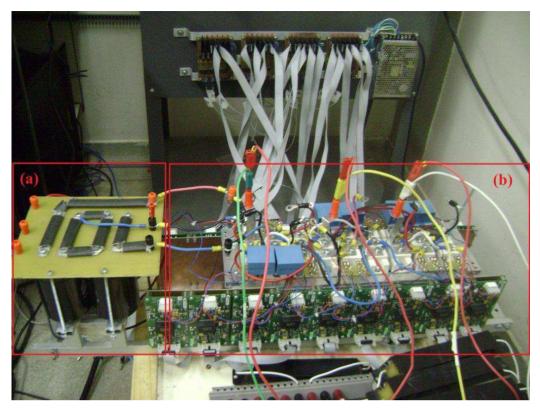

| Figura 22: Foto dos Componentes da montagem: (a) Conversor ANPC; (b) PC; (c) Equipamentos de                |      |

| medição;(d) Circuito de interface DSP/IGBts;(e)Varivolt; (f)DSP                                             | 43   |

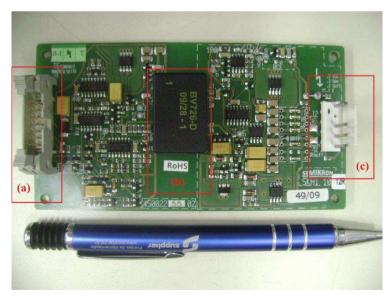

| Figura 23: Foto do Modulo Acoplado PCB; (a) canais de saída A/D via cabo coaxial; (b) canais de saí         |      |

| PWM via fibra ótica.                                                                                        |      |

| Figura 24: Foto do Circuito de interface DSP/Driver; (a) Entrada: receptores de fibra ótica; (b) Saída:     |      |

| Conectores <i>Latch</i> para cabo flat 16 pinos.                                                            |      |

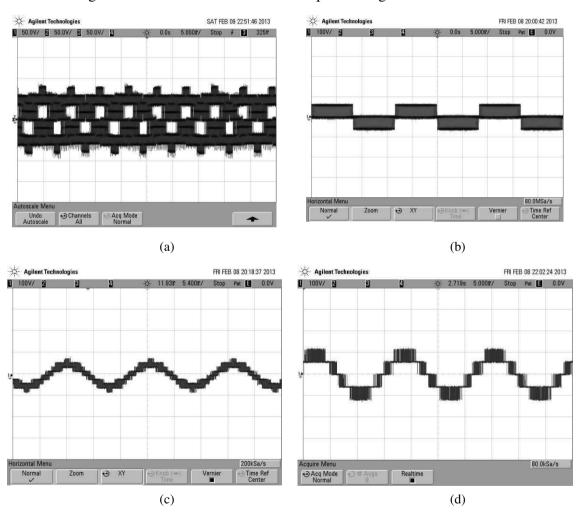

| Figura 25: Foto do Circuito de potência; (a) Retificador Trifásico e barramento DC; (b) Conversor AN        | NPC. |

|                                                                                                             |      |

| Figura 26:Foto do <i>driver</i> de acionamento do IGBT;(a) Entrada: Conector <i>latch</i> para cabo flat 16 |      |

| pinos;(b)Transformador de isolamento; (c)Saída: Conector de 4 pinos para gatilho dos IGBTs                  | 46   |

| Figura 27: Resultados Experimentais para ANPC com estratégia PWM-2 e carga resistiva;                       |      |

| Figura 28: Resultados Experimentais para ANPC com estratégia PWM-2 e carga indutiva; (a)Corrento            |      |

| de linha: (b) Tensão de polo: (c) Tensão de fase: (d) Tensão de linha                                       | 49   |

# LISTA DE TABELAS

| Tabela 1: Estados de comutação e a sequência de chaveamento para o conversor NPC    | 20 |

|-------------------------------------------------------------------------------------|----|

| Tabela 2: Estados de comutação a e sequência de chaveamento para o conversor ANPC   |    |

| Tabela 3: Sequencias de chaveamento para a estratégia PWM-1                         |    |

| Tabela 4: Sequencias de chaveamento para a estratégia PWM-2                         |    |

| Tabela 5: Sequencias de chaveamento para a estratégia PWM-3                         |    |

| Tabela 6: THD para cada estratégia de modulação considerando os dois tipos de carga |    |

| Tabela 7: THD para a estratégia PWM-2 considerando os dois tipos de carga.          |    |

# SUMÁRIO

| A  | gradecin   | nentos                                                                         | V      |

|----|------------|--------------------------------------------------------------------------------|--------|

| R  | esumo      |                                                                                | vii    |

| A  | bstract    |                                                                                | . viii |

| L  | ista de Il | ustrações                                                                      | ix     |

| L  | ista de T  | abelas                                                                         | X      |

| Sı | umário     |                                                                                | xi     |

| 1  | Intro      | dução                                                                          | 13     |

|    | 1.1        | Motivação                                                                      | 13     |

|    | 1.2        | Objetivos                                                                      | 14     |

|    | 1.3        | Fundamentação Teórica                                                          | 14     |

|    | 1.3.1      | Topologias de conversores multinível                                           | 15     |

|    | 1.3.2      | Conversor com capacitores flutuantes (Flying Capacitor Converter)              | 16     |

|    | 1.3.3      | Conversor Convencional em Cascata                                              | 18     |

|    | 1.3.4      | Conversor com diodos de grampeamento do neutro (NPC - Neutral Point Clamped)   | 19     |

|    | 1.3.5      | Conversor com grampeamento ativo do neutro (ANPC-Active Neutral Point Clamped) | 21     |

|    | 1.4        | Estratégias de Modulação Aplicadas ao ANPC                                     | 23     |

|    | 1.4.1      | Estratégia PWM-1                                                               | 24     |

|    | 1.4.2      | Estratégia PWM-2                                                               | 26     |

|    | 1.4.3      | Estratégia PWM-3                                                               | 28     |

|    | 1.4.4      | Processadores Digitais                                                         | 30     |

| 2  | Dese       | nvolvimento                                                                    | 31     |

|    | 2.1        | Material e Métodos                                                             | 31     |

|    | 2.2        | Resultados de Simulação                                                        | 32     |

|    | 2.2.1      | Estratégia PWM-1 Com Carga Resistiva (R = 33,33 Ω)                             | 32     |

|    | 2.2.2      | Estratégia PWM-1 Com Carga Indutiva (R = 33,33 $\Omega$ e L = 7mH)             | 33     |

|    | 2.2.3      | Sinais de gatilho na estratégia PWM-1                                          | 34     |

|    | 2.2.4      | Estratégia PWM-2 Com Carga Resistiva (R = 33,33 Ω)                             | 35     |

|    | 2.2.5      | Estratégia PWM-2 Com Carga Indutiva (R = 33,33 $\Omega$ e L = 7mH)             | 36     |

|    | 2.2.6      | Sinais de gatilho na estratégia PWM-2.                                         | 37     |

|    | 2.2.7      | Estratégia PWM-3 Com Carga Resistiva (R = $33,33 \Omega$ )                     | 38     |

|    | 2.2.8      | Estratégia PWM-3 Com Carga Indutiva (R = 33,33 $\Omega$ e L = 7mH)             | 39     |

|    | 2.2.9      | Sinais de gatilho na estratégia PMW-3                                          | 40     |

|    | 2.2.1      | O Análise dos Resultados de Simulação                                          | 41     |

|    | 2.3        | Implementação do ANPC no Laboratório                                           | 42     |

|    | 2.3.1      | DSP, Módulo PCB Acoplado e Circuito de Interface.                              | 43     |

|    | 2.3.2      | Conversor ANPC                                                                 | 45     |

|    | 2.3.3      | Limitações do Projeto                                                          | 47     |

|    | 2.3.4      | Implementação da Técnica de Modulação no DSP                                   | 47     |

| 2.4       | Resultados Experimentais                                                  | 48 |

|-----------|---------------------------------------------------------------------------|----|

| 2.4.1     | Carga Resistiva $R = 33,33 \Omega$                                        | 48 |

| 2.4.2     | Carga Indutiva $R = 33,33 \Omega$ e L = 7,0mH                             | 49 |

| 2.4.3     | Análise dos Resultados Experimentais                                      | 50 |

| 3 Cons    | iderações Finais                                                          | 51 |

| 3.1       | Trabalhos Futuros                                                         | 51 |

| Referênci | as Bibliográficas                                                         | 52 |

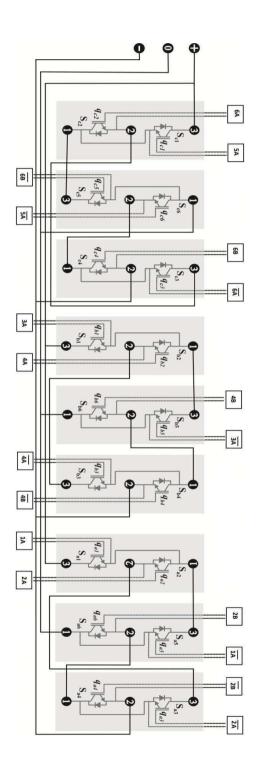

| APÊNDIC   | CE A – Esquemas do ANPC no PSim                                           | 53 |

| APÊNDIC   | EEB – Lista do Material Usado na Montagem do Conversor ANPC               | 54 |

| APÊNDIC   | CE C – Rotina para Calculo do THD                                         | 55 |

| ANEXO A   | A – Esquemático PCI do Circuito de Interface                              | 56 |

| ANEXO E   | B – Esquemático da Montagem do Circuito de Potência e Maneamento dos PWMs | 57 |

# 1 Introdução

Nos últimos anos a procura por sistemas elétricos de alta potencia e média/alta tensão cresceu bastante. O uso de conversores estáticos que controlam este fluxo de potência entre uma fonte e uma carga, nestes níveis de potência, também acompanhou esta demanda. Com os elevados níveis de tensão e/ou corrente em aplicações de alta potência, se faz necessário o uso de dispositivos em série ou paralelo de forma a superar as limitações dos semicondutores. Entretanto, conversores que utilizam chaves com elevadas frequências de chaveamento não operam com aplicações em altas tensões [2]. Para superar este problema pode-se fazer uso de conversores multinível. A conversão multinível em relação à conversão tradicional de dois níveis ainda tem a vantagem de ter um melhor rendimento devido a menores perdas de comutação e a redução de interferência eletromagnética. Por este fato, os conversores multinível ganham espaço nas aplicações de média/alta tensão como em fontes de energia ditas renováveis, máquinas elétricas, distribuição de energia entre outros.

Por outro lado, para fornecer tensões em vários níveis, é necessário o aumento no número de semicondutores e como consequência, a complexidade do sistema também aumenta. A implementação de conversores multiníveis somente se tornou realidade devido ao desenvolvimento tecnológico de semicondutores de potência, além de microcomputadores para o controle das chaves com elevada capacidade e velocidade de processamento, como o DSP (Digital Signal Processor) e o FPGA (Field Programmable Gate Array).

# 1.1 MOTIVAÇÃO

Este trabalho de conclusão de curso tem como motivação a obtenção de resultados experimentais de uma topologia específica de conversor multinível, o conversor ANPC (*Active Neutral Point Clamped*). Para tanto se faz necessário o domínio das técnicas de modulação utilizadas por esta topologia, análise das simulações realizadas e comparação com os resultados obtidos a partir da montagem experimental do conversor ANPC. Este trabalho servirá de base para estudos futuros no que concerne

a detecção e correção de falhas e o estudo da distribuição das perdas na topologia ANPC de acordo com a estratégia de modulação empregada.

#### 1.2 OBJETIVOS

O objetivo geral deste trabalho é a obtenção e análise dos resultados experimentais de um conversor multinível ANPC por meio de uma técnica específica de modulação. Para tanto, é necessário contemplar alguns objetivos específicos, a citar:

- i. Entendimento das técnicas de modulação aplicadas ao conversor ANPC.

- ii. Análise dos resultados de simulação obtidos para a topologia ANPC.

- iii. Implementação do algoritmo de modulação no DSP.

- iv. Resultados experimentais via DSP do conversor ANPC.

## 1.3 FUNDAMENTAÇÃO TEÓRICA

O termo multinível tem sido largamente utilizado para designar níveis intermediários de tensão e/ou corrente em conversores de potência. O conceito básico dos conversores multiniveis está no fato de poderem produzir tensões e/ou correntes em níveis discretos por meio de técnicas de modulação.

Estas tensões e/ou correntes multiníveis na saída dos conversores têm a vantagem de gerar ondas com menor conteúdo harmônico. O principal objetivo deste procedimento de divisão do sinal de saída em níveis é a redução das perdas e a melhoria da estabilidade mecânica dos acionamentos de motores CA. Com o acionamento de motores por meio de níveis suaves de tensão são reduzidos os esforços sobre o torque da máquina. Além disso, os conversores multiníveis têm aplicações que demandam alta potência e qualidade de energia, como nas energias renováveis, fontes de alimentação ininterruptas (UPS – *Uninterruptible Power Suplies*), sistemas de distribuição HVDC (*High Voltage Direct Current*), sistemas de armazenamento de energia em baterias (*BESS-Battery Energy Storage Systems*), entre outros [3].

#### 1.3.1 TOPOLOGIAS DE CONVERSORES MULTINÍVEL

Com a evolução e o desenvolvimento tecnológico dos semicondutores de potencia, além da existência de microprocessadores como os DSPs ou FPGAs a implementação de conversores multinivel tornou-se possível.

Por meio de uma lógica específica de controle das chaves é possível fixar os níveis de tensão alternada na saída. Neste contexto, é possível elencar algumas vantagens e desvantagens dos conversores multinível com relação aos conversores de dois níveis em aplicações de média e alta tensão e média e alta potência. Dentre as vantagens podem se destacar:

- a) Redução dos níveis de interferência eletromagnética (EMI);

- b) Possibilidade de obtenção de níveis mais altos de potência;

- c) Frequência de comutação superior à de um conversor convencional;

- d) Menor taxa de distorção harmônica devido à redução do conteúdo harmônico e consequentemente um maior fator de potência.

#### Como desvantagens, podem-se inferir:

- a) Maior complexidade do sistema devido ao maior número de interruptores, aumentando o custo de implementação;

- b) Maior complexidade nas estratégias de modulação;

- Maior número de capacitores no barramento CC para geração dos níveis discretos de tensão na saída;

Tais desvantagens têm sido reduzidas ao longo do tempo devido à evolução dos semicondutores no sentido de redução nos custos de produção com tecnologias mais eficientes. A mesma evolução é acompanhada pelos microprocessadores responsáveis pelo controle das chaves através de uma interface A/D.

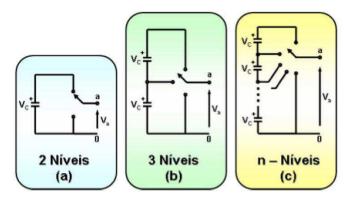

Na Figura 1são ilustrados braços genéricos de conversores multiníveis de acordo com o número de níveis de tensão que podem ser gerados na tensão de saída.

Figura 1 - Braços genéricos de conversores multinível:(a) Braço de um conversor com dois níveis;(b) Braço de um conversor de três níveis;(c) Braço de um conversor com n níveis.

Considerando n o número de níveis da tensão de pólo por braço de um conversor trifásico, a tensão entre fases para este conversor será igual a 2n-1, e a tensão de fase será igual a 4n-3. Assim, um conversor de três níveis terá cinco níveis de tensão entre fases e nove níveis de tensão de fase.

Atualmente existem diferentes topologias de conversores multinivel. Dentre as topologias existentes, três se impuseram no mercado sendo as mais desenvolvidas e com maior numero de aplicações. Tais topologias são:

- a) Conversor com Capacitores Flutuantes (Flying Capacitor Converter);

- b) Conversor Convencional em Cascata (Cascated Full Bridge Converter).

- c) Conversor com Diodos de Grampeamento do Neutro (NPC Neutral Point Clamped);

Nas próximas sub seções são discutidos brevemente os três tipos de conversores multinível com mais aplicações industriais. A atenção será dada nas suas vantagens e desvantagens operacionais. Há um interesse especial no conversor NPC, do qual foi derivado a topologia ANPC (*Active Neutral Point Clamped*), objeto de estudo deste trabalho de conclusão de curso.

# 1.3.2 CONVERSOR COM CAPACITORES FLUTUANTES (FLYING CAPACITOR CONVERTER)

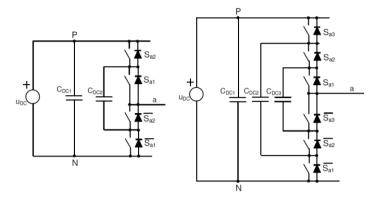

Esta topologia apresenta uma alternativa para os conversores com diodos de grampeamento do neutro (NPC), onde os diodos foram substituídos por capacitores. Dentre as topologias de conversores multinível, esta é uma das mais recentes sendo

introduzida na década de 90 por [4] e [5]. Os braços de um conversor com capacitores flutuantes de três e quatros níveis, respectivamente, estão representados no diagrama unifilar da Figura 2.

Figura 2: Conversor multinivel com capacitores flutuantes de três e quatro níveis respectivamente

Dentre as vantagens desta topologia se destacam:

- a) Limitação de  $\frac{dv}{dt}$  nas chaves semicondutoras;

- b) Introdução de estados adicionais que podem ser utilizados no balanceamento dos capacitores [6];

- c) Capacidade de controle da potência ativa e reativa, tornando sua utilização possível em sistemas de transmissão DC.

Por outro lado, por ser uma das mais recentes topologias, ainda possui algumas limitações tecnológicas, tais como:

- a) Necessidade excessiva de capacitores flutuantes quando o número de níveis é elevado;

- Necessidade de um controlador de carga nos capacitores, aumentando a complexidade do sistema de controle;

- c) A variação brusca de tensão no lado DC leva a uma lenta recuperação dos capacitores, fazendo com que as chaves superiores e inferiores de cada braço bloqueiem uma tensão maior que a prevista durante este tempo. Isto torna seu uso não viável em sistemas de geração distribuída onde se produz rápidas variações de potência transmitida durante afundamentos de tensão da rede.

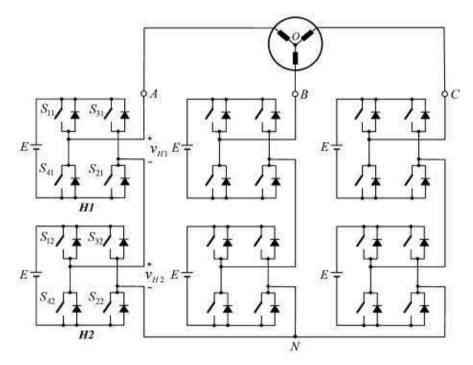

#### 1.3.3 Conversor Convencional em Cascata

Esta estrutura se baseia na conexão em cascata de conversores em ponte completa monofásicos de dois níveis. As formas de onda podem ser geradas através da adição vetorial de cada saída do conversor, com o uso de transformadores ou ainda, elos CC isolados. A Figura 3 ilustra o conversor trifásico multinível em ponte completa ligado em cascata.

Figura 3 Conversor convencional em cascata de cinco níveis

#### Como vantagens podem-se citar:

- a) Requer um número menor de componentes se comparado às outras topologias de multinível, para um mesmo número de níveis;

- Permite a ligação das estruturas em módulos já que todos os níveis têm a mesma estrutura, não necessitando de diodos de grampeamento ou capacitores flutuantes;

- c) Podem ser utulizadas técnicas de comutação suave evitando o uso de *snubbers*.

Por outro lado podemos considerar como desvantagens desta topologia:

- a) São necessárias fontes independentes de tensão continua para cada conversor da estrutura em cascata. Isto pode ser considerado como uma limitação do projeto;

- b) A ligação de fontes isoladas entre conversores em montagens do tipo CA/CC/CA (back-to-back) bidirecionais não é possível, pois produzem curto-circuito. Para evitar este fenômeno é necessária a comutação em sincronia.

# 1.3.4 Conversor com diodos de grampeamento do neutro (NPC - NEUTRAL POINT CLAMPED)

Introduzido em 1981 por Nabae [7], o conversor com diodos de grampeamento do neutro (NPC) é o conversor multinível mais amplamente aplicado e estudado até o momento. Na Figura 4 está o circuito do NPC de três níveis.

Figura 4: Conversor NPC de três níveis convencional

O conversor de três níveis ilustrado na Figura 3 mostra que o barramento DC do conversor, é dividido em três níveis  $\frac{V_{dc}}{2}$ , 0,  $-\frac{V_{dc}}{2}$  devido aos dois capacitores  $C_1e$   $C_2$  ligados em série. Os níveis das tensões de pólo de cada braço são obtidos por um conjunto de estados das chaves definidos pela técnica de modulação utilizada. Os estados das chaves são apresentados na Tabela 1.

| Tensão de Pólo      | Estado | $T_{1x}$ | $T_{1Cx}$ | $T_{2x}$ | $T_{2Cx}$ |

|---------------------|--------|----------|-----------|----------|-----------|

| $-\frac{V_{dc}}{2}$ | N      | 0        | 1         | 0        | 1         |

| 0                   | 0      | 0        | 1         | 1        | 0         |

| $V_{dc}$            | P      | 1        | 0         | 1        | 0         |

Tabela 1: Estados de comutação e a sequência de chaveamento para o conversor NPC

Podem ser consideradas como vantagens do NPC:

- a) Há uma maior divisão da tensão aplicada as chaves quando bloqueadas, dado que cada chave tem de bloquear uma tensão igual a  $\frac{V_{dc}}{n-1}$  para nníveis de tensão:

- b) Menor número de capacitores utilizados quando comparada a outras topologias de multinível, refletindo na redução dos custos de implementação;

- c) A mudança entre níveis de tensão é realizada apenas com o acionamento de uma das chaves diminuindo as perdas e interferências.

Por outro lado como desvantagens podem-se elencar:

- a) Nas topologias com mais de três níveis os diodos não bloqueiam os mesmos níveis de tensão sendo necessário adicionar diodos em série, aumentando os custos do projeto;

- b) Algoritmos de controle das chaves mais complexos devido ao controle do balanceamento da tensão no barramento CC e à geração dos pulsos PWMs;

- c) Os diodos de grampeamento devem ser de rápida recuperação uma vez que comutam à frequência de chaveamento;

- d) Distribuição desigual de perdas.

# 1.3.5 CONVERSOR COM GRAMPEAMENTO ATIVO DO NEUTRO (ANPC-ACTIVE NEUTRAL POINT CLAMPED)

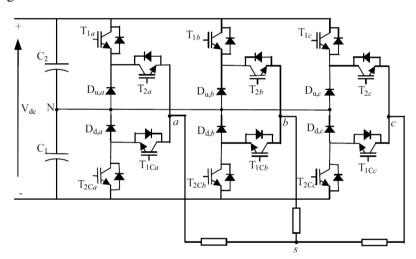

Recentemente foi apresentada uma variação da topologia NPC onde os diodos de grampeamento foram substituídos por chaves ativas com diodos em antiparalelo. A topologia do conversor ANPC de três níveis está na Figura 5. Deste modo, o conversor ANPC de três níveis passa a ser constituído por dezoito chaves bidirecionais, ao passo que o NPC possui doze chaves bidirecionais e seis diodos de grampeamento. As tensões de polo são definidas como sendo a diferença de potencial entre a fase x e o ponto O e as tensões de fase são definidas como a diferença de potencial entre a fase x e o ponto N, onde x representa a fase escolhida. Por fim, as tensões de linha são definidas como a diferença de potencial entre fases, duas a duas. Assim, para o conversor considerado na Figura 5, as tensões de polo são:  $V_{ao}$ ,  $V_{bo}$  e  $V_{co}$ , as tensões de fase são  $V_{aN}$ ,  $V_{bN}$  e  $V_{cN}$  e as tensões de linha são:  $V_{ab}$ ,  $V_{bc}$  e  $V_{ca}$ .

Figura 5: Conversor ANPC de três níveis.

Segundo [8] como o NPC possui uma distribuição desigual das perdas, a frequência de chaveamento e a potencia de saída do conversor tornam-se limitadas. De modo a evitar a distribuição desigual das perdas sobre os dispositivos semicondutores, foi desenvolvida a ideia do NPC ativo, ou ANPC. Com uma lógica especifica para os estados de chaveamento do ANPC é possível analisar a distribuição das perdas sobre as chaves semicondutoras, como será visto logo mais adiante.

O NPC visto na Seção 1.2.1, independente da técnica de modulação utilizada, tem apenas um único arranjo de chaveamento capaz de gerar o estado de comutação O, como é verificado na Tabela 1. Isto ocorre pelo fato do caminho de

circulação da corrente depender apenas do seu sentido. Acompanhando a Figura 4 verifica-se que a corrente circulará no diodo de grampeamento relativo à parte superior do barramento se o sentido for positivo e caso a corrente seja negativa, circulará pelo diodo de grampeamento relativo à parte inferior do barramento.

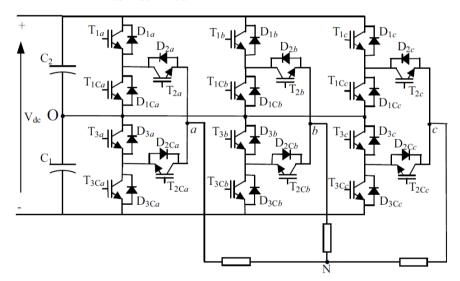

Por outro lado, para o ANPC existe mais de uma maneira de combinação das chaves de modo a atingirmos o estado O. Como as chaves são bidirecionais, então é possível a obtenção do estado O de forma independente do sentido da corrente, bastando apenas de uma técnica de modulação capaz de gerar um possível arranjo das chaves, para esta finalidade [8]. Diante desse possível modo de operação do ANPC pode-se fazer uma distribuição mais igualitária das perdas sobre os dispositivos de potencia, pois é possível fazer a seleção do caminho superior ou do caminho inferior para alcançar o estado O. A Figura 6 ilustra dois modos de obtenção do estado O, sendo um pelo caminho superior e o outro pelo caminho inferior. De fato, esta comutação do estado O (ou para o estado O) é quem determina a distribuição das perdas de chaveamento.

Figura 6: Estado de condução O para uma corrente positiva: (a) pelo caminho superior; (b) pelo caminho inferior.

O conversor ANPC da Figura 5 também tem três estados de comutação (*P*, *O e N*) que podem ser obtidos de acordo com a sequencia de chaveamento da Tabela 2.

| Tensão de Polo      | Estado | $T_{1x}$ | $T_{1Cx}$ | $T_{2x}$ | $T_{2Cx}$ | $T_{3x}$ | $T_{3Cx}$ |

|---------------------|--------|----------|-----------|----------|-----------|----------|-----------|

| $-\frac{V_{dc}}{2}$ | $N_1$  | 0        | 0         | 0        | 1         | 0        | 1         |

| 2                   | $N_2$  | 0        | 1         | 0        | 1         | 0        | 1         |

|                     | 0_1    | 0        | 0         | 0        | 1         | 1        | 0         |

| 0                   | 0_2    | 0        | 1         | 1        | 0         | 0        | 1         |

|                     | 01+    | 0        | 1         | 1        | 0         | 0        | 0         |

|                     | 02+    | 1        | 0         | 0        | 1         | 1        | 0         |

| $+\frac{V_{dc}}{2}$ | $P_1$  | 1        | 0         | 1        | 0         | 0        | 0         |

| 2                   | $P_2$  | 1        | 0         | 1        | 0         | 1        | 0         |

Tabela 2: Estados de comutação a e sequência de chaveamento para o conversor ANPC.

## 1.4 ESTRATÉGIAS DE MODULAÇÃO APLICADAS AO ANPC

Segundo a Tabela 2 a topologia ANPC permite mais de uma possibilidade de chaveamento para alcançar os estados de comutação *P*, *O e N*. De acordo com [8] isto permite a realização de três técnicas de modulação senoidal por largura de pulso (*PWM-1,PWM-2,PWM-3*). Estas estratégias diferem quanto a sequencia de chaveamento utilizada para alcançar o estado *O* e ao tipo de comutação no que diz respeito à frequência de chaveamento de cada chave, como será visto nas próximas seções.

Os estados O redundantes permitem uma distribuição mais igualitária das perdas sobre os dispositivos de potência do ANPC [9]. As estratégias *PWM-1 e PWM-2* permitem duas possibilidades de obtenção do estado *O* ao passo que a estratégia *PWM-3* habilita quatro possibilidades. As três estratégias de modulação serão discutidas a seguir.

#### 1.4.1 ESTRATÉGIA PWM-1

Nesta estratégia são obtidos quatro estados de chaveamento:  $N_1$ ,  $O_1^-$ ,  $O_1^+$ e  $P_1$ . Como visto na Tabela 2, o estado  $N_1$  é obtido quando as chaves  $T_{2Cx}$  e  $T_{3Cx}$  estão conduzindo e as chaves  $T_{1x}$ ,  $T_{1Cx}$ ,  $T_{2x}$  e  $T_{3x}$  estão bloqueadas. O estado  $O_1^-$  é obtido quando as chaves  $T_{2Cx}$   $T_{3x}$  estão conduzindo e as chaves  $T_{1x}$ ,  $T_{1Cx}$ ,  $T_{2x}$  e  $T_{3Cx}$  estão bloqueadas. O estado  $O_1^+$  é obtido quando as chaves  $T_{1Cx}$  e  $T_{2x}$  estão conduzindo e as chaves  $T_{1x}$ ,  $T_{2Cx}$ ,  $T_{3x}$  e  $T_{3Cx}$  estão bloqueadas. Finalmente o estado  $P_1$  é obtido quando as chaves  $T_{1x}$ ,  $T_{2x}$  estão conduzindo e as chaves  $T_{1Cx}$ ,  $T_{2Cx}$ ,  $T_{3x}$  e  $T_{3Cx}$  estão bloqueadas. A sequencia de chaveamento descrita acima, e os quatro estados de chaveamento obtidos, estão destacados na Tabela 3.

Tensão de Pólo Estado  $T_{1x}$  $T_{2x}$  $T_{2Cx}$  $T_{3x}$  $T_{3Cx}$  $T_{1Cx}$  $N_1$  $N_2$  $0_{1}^{-}$  $0_{2}^{-}$  $0_{1}^{+}$  $0_{2}^{+}$  $\boldsymbol{P_1}$  $P_2$

Tabela 3: Sequencias de chaveamento para a estratégia PWM-1.

Analisando a sequência anterior de chaveamento, nota-se que as chaves  $T_{1x}$ ,  $T_{1Cx}$ ,  $T_{3x}$  e  $T_{3Cx}$  comutam na frequência de chaveamento (alta frequência), enquanto as chaves  $T_{2x}$ ,  $T_{2Cx}$  comutam na frequência da tensão de referência (baixa frequência). A estratégia *PWM*-1 usa duas portadoras, uma para a comparação com a tensão de referência no semiciclo positivo para geração dos estados  $O_1^+$  e  $P_1$  e a outra (com mesma amplitude e frequência, mas deslocada em nível no eixo vertical) para a comparação com a tensão de referência no semiciclo negativo para a geração dos

estados  $N_1, O_1^-$ . As formas de onda consideradas para a estratégia de modulação senoidal PWM-1 estão na Figura 7.

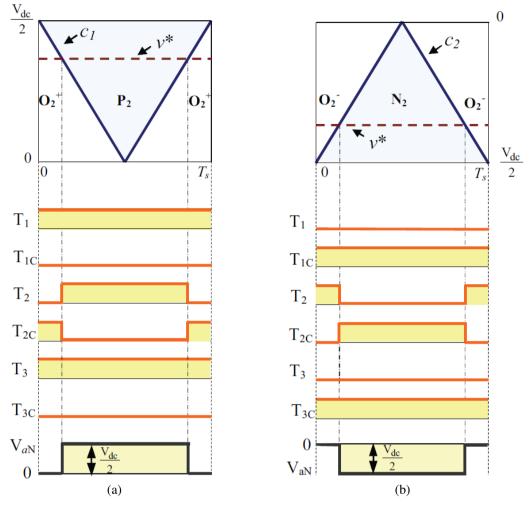

Figura 7: Estratégia *PWM-1;* (a) Portadora e tensão de referencia para geração dos níveis positivos. (b) Portadora e tensão de referência para geração dos níveis negativos

#### 1.4.2 ESTRATÉGIA PWM-2

Nesta estratégia são obtidos quatro estados de chaveamento:  $N_2$ ,  $O_2^-$ ,  $O_2^+$ e  $P_2$ . Como visto na Tabela 2, o estado  $N_2$  é obtido quando as chaves  $T_{1Cx}$ ,  $T_{2Cx}$  e  $T_{2Cx}$  estão conduzindo e as chaves ,  $T_{1x}$   $T_{2x}$  e  $T_{3x}$  estão bloqueadas. O estado ,  $O_2^-$ é obtido quando as chaves  $T_{1Cx}$ ,  $T_{2x}$  e  $T_{3Cx}$  estão conduzindo e as chaves  $T_{1x}$   $T_{2Cx}$  e  $T_{3x}$  estão bloqueadas. O estado  $O_2^+$  é obtido quando as chaves  $T_{1x}$   $T_{2Cx}$  e  $T_{3x}$  estão conduzindo e as chaves  $T_{1Cx}$ ,  $T_{2x}$  e  $T_{3Cx}$  estão bloqueadas. Finalmente o estado  $P_2$  é obtido quando as chaves  $T_{1x}$   $T_{2x}$  e  $T_{3x}$  estão conduzindo e as chaves  $T_{1x}$ ,  $T_{2x}$  e  $T_{3x}$  estão conduzindo e as chaves  $T_{1Cx}$ ,  $T_{2Cx}$  e  $T_{3cx}$  estão bloqueadas. A sequencia de chaveamento descrita acima, e os quatro estados de chaveamento obtidos, estão destacados na Tabela 4.

|                     |                                    |          |           | -        |           |          |           |

|---------------------|------------------------------------|----------|-----------|----------|-----------|----------|-----------|

| Tensão de Pólo      | Estado                             | $T_{1x}$ | $T_{1Cx}$ | $T_{2x}$ | $T_{2Cx}$ | $T_{3x}$ | $T_{3Cx}$ |

| $-\frac{V_{dc}}{2}$ | $N_1$                              | 0        | 0         | 0        | 1         | 0        | 1         |

|                     | $N_2$                              | 0        | 1         | 0        | 1         | 0        | 1         |

| 0                   | $O_{1}^{-}$                        | 0        | 0         | 0        | 1         | 1        | 0         |

|                     | 0-                                 | 0        | 1         | 1        | 0         | 0        | 1         |

|                     | 01+                                | 0        | 1         | 1        | 0         | 0        | 0         |

|                     | <b>0</b> <sub>2</sub> <sup>+</sup> | 1        | 0         | 0        | 1         | 1        | 0         |

| $+\frac{V_{dc}}{2}$ | $P_1$                              | 1        | 0         | 1        | 0         | 0        | 0         |

|                     | $P_2$                              | 1        | 0         | 1        | 0         | 1        | 0         |

Tabela 4: Sequencias de chaveamento para a estratégia PWM-2

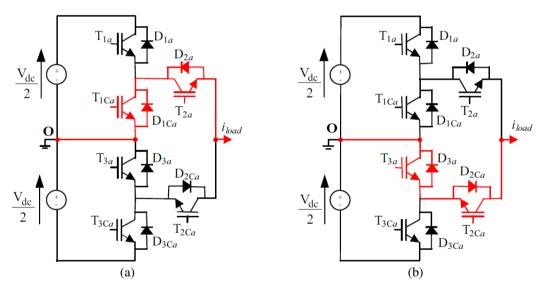

Analisando a sequência anterior de chaveamento, ao contrário da estratégia PWM-1, nota-se que as chaves  $T_{2x}$ ,  $T_{2Cx}$  comutam na frequência de chaveamento (alta frequência), enquanto as chaves  $T_{1x}$ ,  $T_{1Cx}$ ,  $T_{3x}$  e  $T_{3Cx}$  comutam na frequência da tensão de referência (baixa frequência). A estratégia PWM-2 usa duas portadoras, uma para a comparação com a tensão de referência no semiciclo positivo e geração dos estados  $O_2^+$  e  $P_2$  e a outra (com mesma amplitude e frequência, mas deslocada em nível no eixo vertical) para a comparação com a tensão de referência no semiciclo negativo e geração

dos estados  $N_2, O_2^-$ . As formas de onda consideradas para a estratégia de modulação senoidal PWM-2 estão na Figura 8.

Figura 8 Estratégia *PWM-2*. (a) Portadora e tensão de referencia para geração dos níveis positivos (b) Portadora e tensão de referência para geração dos níveis negativos

#### 1.4.3 ESTRATÉGIA PWM-3

Nesta estratégia são obtidos seis estados de chaveamento:  $N_2$ ,  $O_1^-$ ,  $O_2^-$ ,  $O_1^+$ ,  $O_2^+$  e  $P_2$ . Como já foi discutido nas seções anteriores para as estratégias *PWM-1 e PWM-2* a sequencia de chaveamento para a obtenção desses estados, então, na Tabela 5estão destacados a sequencia de chaveamento necessária para esta estratégia.

| Tensão de Pólo      | Estado                             | $T_{1x}$ | $T_{1Cx}$ | $T_{2x}$ | $T_{2Cx}$ | $T_{3x}$ | $T_{3Cx}$ |

|---------------------|------------------------------------|----------|-----------|----------|-----------|----------|-----------|

|                     | $N_1$                              | 0        | 0         | 0        | 1         | 0        | 1         |

| $-\frac{V_{dc}}{2}$ | $N_2$                              | 0        | 1         | 0        | 1         | 0        | 1         |

| 0                   | $O_1^-$                            | 0        | 0         | 0        | 1         | 1        | 0         |

|                     | 0-2                                | 0        | 1         | 1        | 0         | 0        | 1         |

|                     | 01                                 | 0        | 1         | 1        | 0         | 0        | 0         |

|                     | <b>0</b> <sub>2</sub> <sup>+</sup> | 1        | 0         | 0        | 1         | 1        | 0         |

| $\frac{V_{dc}}{2}$  | $P_1$                              | 1        | 0         | 1        | 0         | 0        | 0         |

|                     | $P_2$                              | 1        | 0         | 1        | 0         | 1        | 0         |

Tabela 5: Sequencias de chaveamento para a estratégia PWM-3.

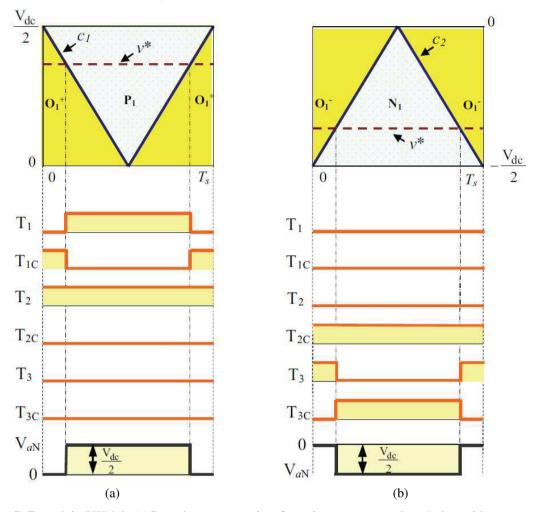

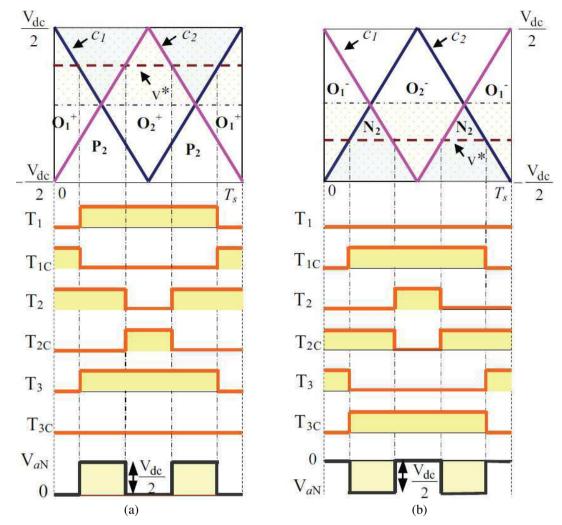

Analisando a sequência anterior de chaveamento, nota-se que todas as chaves do braço comutam na frequência de chaveamento. Os estados  $P_2$ ,  $O_1^+e$   $O_2^+$  são conseguidos quando a tensão de referência é positiva enquanto os estados  $N_2$ ,  $O_1^-e$   $O_1^+$  são conseguidos quando a tensão de referência é negativa. Pode-se notar que nessa estratégia de modulação são necessárias duas portadoras, uma para comparação com a tensão de referência no semiciclo positivo para geração dos estados  $P_2$ ,  $O_1^+e$   $O_2^+$  e a outra (com mesma amplitude e frequencia, mas deslocada no eixo horizontal em meio período de chaveamento  $-\frac{T_s}{2}$ ) para a comparação com a tensão de referência no semiciclo negativo para geração dos estados  $N_2$ ,  $O_1^-e$   $O_1^+$ . As formas de onda consideradas para a estratégia de modulação senoidal PWM-3 estão na Figura 9.

Figura 9: Estratégia *PWM-3*. (a) Portadoras e tensão de referencia para geração dos níveis positivos; (b) Portadoras e tensão de referência para geração dos níveis negativos.

#### 1.4.4 PROCESSADORES DIGITAIS

Com a evolução dos sistemas digitais, os processadores surgiram como uma alternativa aos sistemas analógicos que ao longo do tempo se tornaram complexos e de difícil ajuste. Dentre os processadores digitais destacam-se os microcontroladores PICs (*Programmable Interface Controller*) e os DSPs (*Digital Signal Processor*). Os PICs são mais baratos e de fácil acesso, entretanto, não são recomendados para o chaveamento de conversores pois têm número limitado de saídas PWMs. Uma alternativa são os DSPs, devido à sua alta velocidade de processamento, versatilidade quanto à linguagem de programação (C ou *Assembly*), e hardware próprio para operações com pontos flutuantes [10].

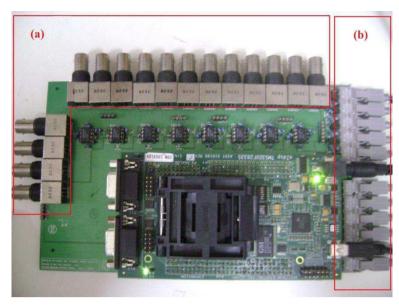

Neste trabalho é utilizado o DSP modelo eZdsp TMS320F2833 da Figura 10 para gerar os sinais PWM enviados aos IGBTs do conversor ANPC.

Figura 10: Foto do DSP modelo eZdsp TMS320F2833

### 2 DESENVOLVIMENTO

Neste capítulo são apresentados os resultados das simulações das técnicas de modulação aplicadas ao conversor ANPC de três níveis com cargas trifásicas em Y de natureza resistiva e indutiva. Também é discutido o material empregado no desenvolvimento experimental do conversor, além da configuração do DSP para a geração dos sinais de chaveamento no ANPC montado no LEIAM. Por fim, são analisados os resultados experimentais obtidos.

## 2.1 MATERIAL E MÉTODOS

Para a simulação da topologia multinível proposta, foi utilizado o *software* PSim versão 9.0.3 Trial, que por meio de "*dlls*" (Biblioteca de vínculo dinâmico, de *Dynamic-link library*) possibilita a criação de um código em C para gerar, de acordo com as técnicas de modulação apresentadas no Capítulo 1, os sinais de chaveamento.

Para a geração dos sinais de chaveamento na topologia montada no LEIAM, optou-se por utilizar o DSP e a programação em linguagem C.

#### A metodologia empregada consistiu na:

- a) Pesquisa, análise e revisão de material bibliográfico a respeito do tema abordado;

- b) Simulação das técnicas de modulação no conversor ANPC;

- c) Implementação do algoritmo simulado no DSP;

- d) Obtenção de resultados experimentais do ANPC;

- e) Elaboração do relatório;

# 2.2 RESULTADOS DE SIMULAÇÃO

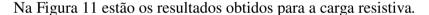

A seguir são discutidos os resultados obtidos para as técnicas de modulação *PWM-1, PWM-2 e PWM-3* na frequência de chaveamento de 10kHz. São apresentadas as formas de onda das tensões de polo, tensões de fase, tensões de linha e correntes de linha para cada fase do conversor. Para tanto, são consideradas dois tipos de carga trifásica em Y: uma resistiva e a outra indutiva. Depois disso, será feita uma análise da taxa de distorção harmônica (THD) para cada tipo de estratégia simulada e para cada tipo de carga. Os esquemáticos dos circuitos simulados no PSim para os dois tipos de carga estão no Apêndice A.

#### 2.2.1 ESTRATÉGIA PWM-1 COM CARGA RESISTIVA (R = 33,33 $\Omega$ )

Nesta estratégia são necessárias duas portadoras, com mesma frequência e amplitude, sendo uma deslocada da outra sobre o eixo vertical, como está representada na Figura 7.

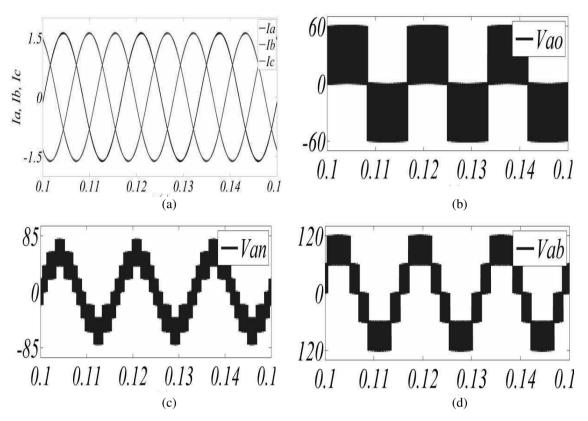

Figura 11: Resultados de simulação para ANPC com estratégia de PWM-1 com carga resistiva; (a)Correntes de linha; (b) Tensão de polo; (c) Tensão de fase; (d)Tensão de linha.

#### 2.2.2 ESTRATÉGIA PWM-1 COM CARGA INDUTIVA (R = 33,33 $\Omega$ e L = 7mH)

Na Figura 12 estão os resultados obtidos para a carga indutiva.

Figura 12: Resultados de simulação para ANPC com estratégia de PWM-1 com carga indutiva; (a)Correntes de linha; (b) Tensão de polo; (c) Tensão de fase; (d) Tensão de linha.

A partir dos resultados de simulação obtidos para a estratégia *PWM-1*é possível confirmar que independente da natureza da carga, as tensões de pólo, de fase e de linha têm três, nove e cinco níveis, respectivamente, como previsto no Capítulo 1. Com uma breve análise da Figura 11(a), nota-se que as correntes de linha acompanham as tensões de fase, como esperado para uma carga resistiva.

Para a carga indutiva, é possível perceber na Figura 12(a), uma corrente mais senoidal, fator este que pode ser compreendido pela propriedade da carga indutiva nesta configuração se comportar como um filtro passa baixas de corrente.

#### 2.2.3 SINAIS DE GATILHO NA ESTRATÉGIA PWM-1

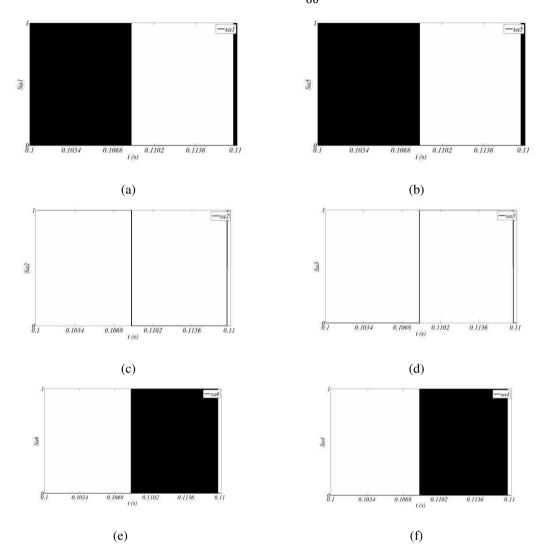

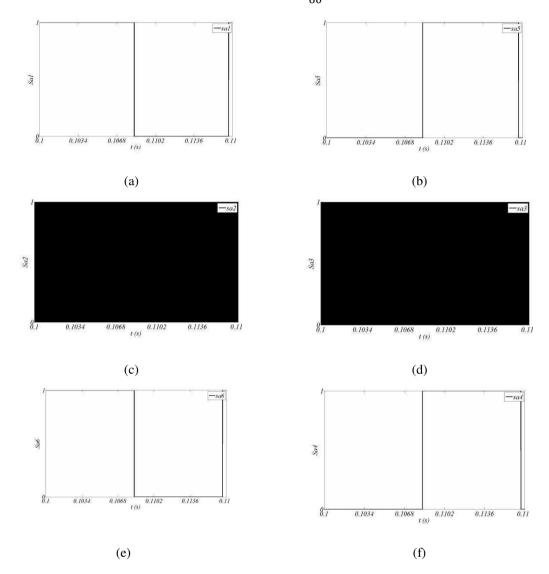

Os sinais de gatilho das chaves estão na Figura 13. Está sendo considerado em um intervalo de tempo aproximadamente igual a  $\frac{1}{60}$  s.

Figura 13: Sinais de gatilho. (a) $T_{1a}$ ; (b)  $T_{1ca}$ ; (c)  $T_{2a}$ ; (d)  $T_{2ca}$ ; (e)  $T_{3a}$ ; (f)  $T_{3ca}$ .

A partir dos sinais de gatilho percebe-se que na estratégia PWM-1 apenas as chaves  $(c)T_{2a}e(d)T_{2ca}$  comutam na frequência da modulante (60Hz). Devido a frequência de chaveamento ser 10kHZ, não é visível na Figura 13 a complementaridade entre as chaves (a) $T_{1a}e(b)T_{1ca}$  e tampouco entre as chaves (e)  $T_{3a}e(f)T_{3ca}$

#### 2.2.4 Estratégia PWM-2 Com Carga Resistiva ( $R = 33,33 \Omega$ )

Semelhante à estratégia anterior, nesta estratégia são necessárias duas portadoras, com mesma frequência e amplitude, sendo uma deslocada da outra sobre o eixo vertical, como está representada na Figura 8.

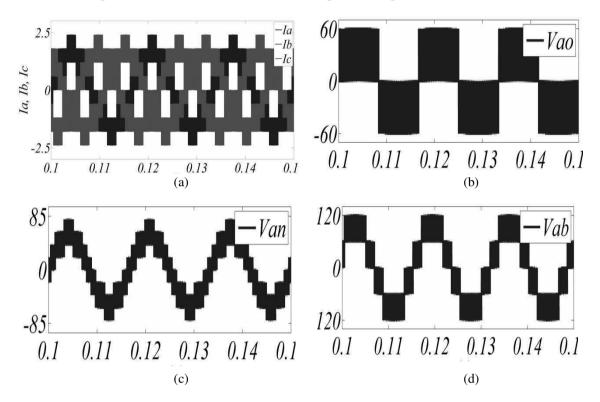

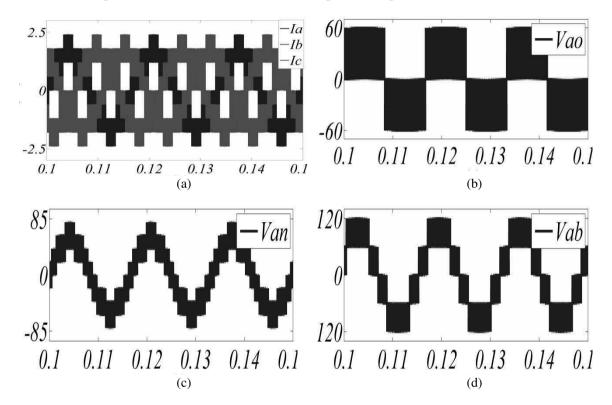

Na Figura 14 estão os resultados obtidos para a carga resistiva.

Figura 14: Resultados de simulação para ANPC com estratégia de PWM-2 com carga resistiva; (a)Correntes de linha; (b) Tensão de polo; (c) Tensão de fase; (d) Tensão de linha.

Novamente é possível perceber a sintonia entre as tensões de linha e as correntes de fase para este tipo de carga.

#### 2.2.5 ESTRATÉGIA PWM-2 COM CARGA INDUTIVA (R = 33,33 $\Omega$ e L = 7mH)

Na Figura 15 estão os resultados obtidos para a carga indutiva

Figura 15: Resultados de simulação para ANPC com estratégia de PWM-2 com carga indutiva; (a)Correntes de linha; (b) Tensão de polo; (c) Tensão de fase; (d) Tensão de linha.

Verifica-se correntes de linha senoidais, como esperado para uma carga indutiva, trifásica e ligada em Y.

#### 2.2.6 SINAIS DE GATILHO NA ESTRATÉGIA PWM-2.

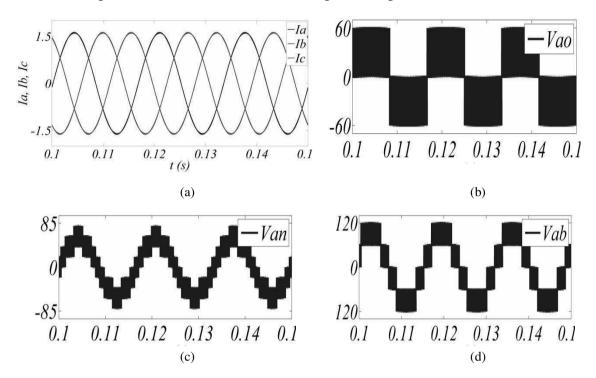

Os sinais de gatilho das chaves estão na Figura 16. Está sendo considerado em um intervalo de tempo aproximadamente igual a  $\frac{1}{60}$  s.

Figura 16: Sinais de gatilho. (a) $T_{1a}$ ; (b)  $T_{1ca}$ ; (c)  $T_{2a}$ ; (d)  $T_{2ca}$ ; (e)  $T_{3a}$ ; (f)  $T_{3ca}$ .

Na estratégia PWM-2 está claro que as chaves (a) $T_{1a}$  e (b)  $T_{1ca}$  são complementares bem como (e)  $T_{3a}$  (f)  $T_{3ca}$  e que comutam na frequência da modulante (60Hz). Por outro lado, devido a resolução dos sinais na frequência de chaveamento de 10kHZ, não é visível a complementaridade entre as chaves (c) $T_{2a}$  e (d)  $T_{2ca}$ .

#### 2.2.7 ESTRATÉGIA PWM-3 COM CARGA RESISTIVA (R = 33,33 $\Omega$ )

Nesta estratégia são necessárias duas portadoras, com mesma frequência e amplitude, sendo uma deslocada de  $\frac{T_s}{2}$  da outra sobre o eixo horizontal, visto na Figura 9.

Na Figura 17estão os resultados obtidos para a carga resistiva.

Figura 17: Resultados de simulação para ANPC com estratégia de PWM-3 com carga resistiva; (a)Correntes de linha; (b) Tensão de polo; (c) Tensão de fase; (d) Tensão de linha.

Apesar de não ser evidente a diferença dos resultados desta técnica com relação às anteriores, nesta estratégia de modulação há o dobro de transições de estados de comutação em cada período de chaveamento, como pode ser visto na Figura 918. Isto é explicado pelo fato de nesta estratégia, serem utilizadas as quatro sequencias de chaveamento possível para gerar o estado O representadas por  $O_1^-, O_2^-, O_1^+, O_2^+$ . Como será visto adiante, este fato não altera em grandes proporções o conteúdo harmônico dos sinais analisados.

#### 2.2.8 ESTRATÉGIA PWM-3 COM CARGA INDUTIVA (R = 33,33 $\Omega$ e L = 7mH)

Na Figura 19 estão os resultados obtidos para a carga indutiva.

Figura 19: Resultados de simulação para ANPC com estratégia de PWM-3 com carga indutiva; (a)Correntes de linha; (b) Tensão de polo; (c) Tensão de fase; (d) Tensão de linha.

#### 2.2.9 SINAIS DE GATILHO NA ESTRATÉGIA PMW-3

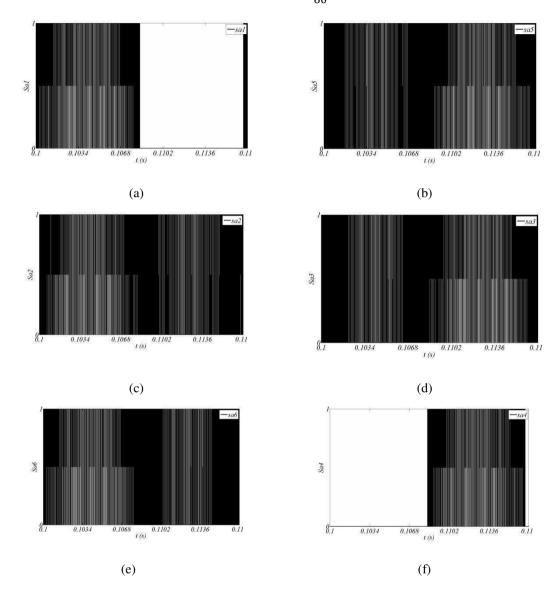

Os sinais de gatilho das chaves estão na Figura 20. Está sendo considerado em um intervalo de tempo aproximadamente igual a  $\frac{1}{60}s$ .

Figura 20: Sinais de gatilho. (a) $T_{1a}$ ; (b)  $T_{1ca}$ ; (c)  $T_{2a}$ ; (d)  $T_{2ca}$ ; (e)  $T_{3a}$ ; (f)  $T_{3ca}$ .

Na estratégia PWM-3 as chaves (a)  $T_{1a} e$  (f)  $T_{3ca}$  comutam na frequência da portadora durante um semiciclo da modulante enquanto que as outras chaves (b)  $T_{1ca}$ ,  $(c)T_{2a} e$   $(d)T_{2ca}$ , (e)  $T_{3a}$  comutam na frequência da portadora. Não há complementaridade em nenhum par de chaves nesta estratégia.

#### 2.2.10 Análise dos Resultados de Simulação

A Taxa de Distorção Harmônica Total (THD) é uma métrica muito utilizada para determinar o conteúdo harmônico de um sinal alternado. Em outras palavras, o THD demonstra o quanto um sinal alternado carrega de componentes harmônicas com relação à sua fundamental. Matematicamente o THD é expresso por:

$$THD = \frac{\sqrt{\sum_{h=2}^{\infty} y_h^2}}{y_1} \tag{1}$$

Onde  $y_1$  é a amplitude da tensão fundamental,  $y_h$  é a amplitude da componente harmônica de ordem h e  $N_h$  é o número de harmônicos considerados.

Com uma rotina criada no Matlab, foi calculada a Taxa de Distorção Harmônica (THD) para cada estratégia de modulação. A rotina está no Apêndice C e o resultado está apresentado na Tabela 6.

|            | •         | ě.     | ,        |          | O        |

|------------|-----------|--------|----------|----------|----------|

| Estratégia | Carga     | $I_a$  | $V_{ao}$ | $V_{an}$ | $V_{ab}$ |

| PWM -1     | Resistiva | 39,18% | 64,35%   | 39,20%   | 39,21%   |

|            | Indutiva  | 0,83%  | 64,35%   | 39,20%   | 39,21%   |

| PWM -2     | Resistiva | 39,21% | 64,34%   | 39,18%   | 39,20%   |

|            | Indutiva  | 0,85%  | 64,35%   | 39,20%   | 39,21%   |

| PWM -3     | Resistiva | 39,22% | 64,40%   | 39,20%   | 39,19%   |

|            | Indutiva  | 0,83%  | 64,41%   | 39,21%   | 39,19%   |

Tabela 6: THD para cada estratégia de modulação considerando os dois tipos de carga.

Comparando-se os resultados de simulação obtidos para as três técnicas de modulação desenvolvidas, é possível perceber que são bastante parecidas, comprovado pelo *THD* que não sofre grandes variações de acordo com a estratégia utilizada. Em todos os casos as tensões estão balanceadas e para o caso da carga indutiva, as correntes de linha são equilibradas e filtradas.

### 2.3 IMPLEMENTAÇÃO DO ANPC NO LABORATÓRIO

De modo a validar os resultados de simulação obtidos na seção 2.2, o conversor ANPC foi montado e a modulação das chaves implementada via DSP. Nesta seção será discutida a parte experimental deste trabalho bem como os resultados obtidos para a topologia supracitada.

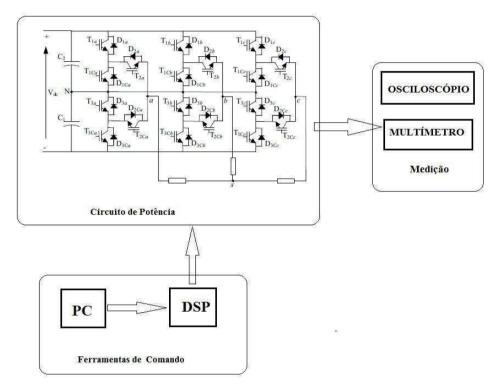

O diagrama apresentado na Figura 21 mostra esquematicamente a montagem desenvolvida no LEIAM.

Figura 21: Diagrama esquemático da montagem realizada.

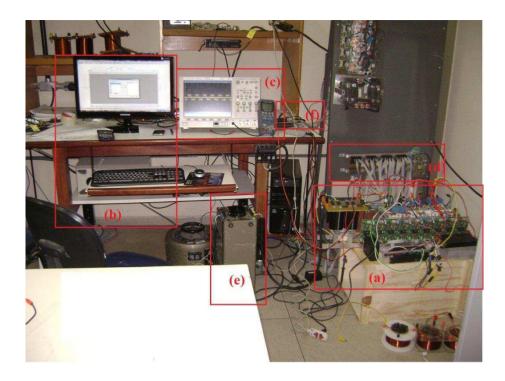

A configuração da montagem experimental pode ser visualizada na Figura 22 com destaque para alguns dispositivos e circuitos.

Figura 22: Foto dos Componentes da montagem: (a) Conversor ANPC; (b) PC; (c) Equipamentos de medição;(d) Circuito de interface DSP/IGBts;(e)Varivolt; (f)DSP

A lista detalhada de todo o material usado na montagem do conversor está no Apêndice B.

#### 2.3.1 DSP, MÓDULO PCB ACOPLADO E CIRCUITO DE INTERFACE.

A implementação das estratégias de modulação desenvolvidas no Psim foram modificadas para serem carregados no eZdsp TMS320F28335 através do software Code Composer Studio v3.3. De modo a ser compatível com o DSP, todo o código gerado no PSim é implementado no tempo discreto.

A Figura 23 na próxima página ilustra o DSP com o módulo PCB acoplado ao circuito do DSP. Este módulo é uma placa de circuito impresso criada no LEIAM. O módulo implementa duas interfaces: uma com os canais *A/D* através dos conectores de cabos coaxiais e a outra com os canais *PWM* através dos conectores de fibra ótica.

Figura 23: Foto do Modulo Acoplado PCB; (a) canais de saída A/D via cabo coaxial; (b) canais de saída PWM via fibra ótica.

Os blocos ePWM disponíveis no programa raiz do Code Composer Studio configuram os módulos da placa do DSP. Por meio de fibras óticas, os sinais transmitidos pelo DSP são acondicionados por um circuito de interface e depois são enviados para os *drivers* dos IGBTs.

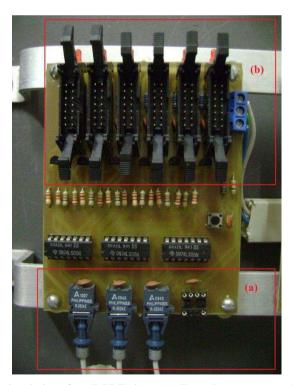

Este circuito de interface entre o DSP e os *drivers* dos IGBTs é visualizado na Figura 24.

Figura 24: Foto do Circuito de interface DSP/Driver; (a) Entrada: receptores de fibra ótica; (b) Saída: Conectores *Latch* para cabo flat 16 pinos.

O circuito é composto por três receptores de fibra ótica na entrada da placa e seis conectores *Latch* para cabo flat de 16 pinos na sua saída para conexão com os drivers.

O DSP disponibiliza seis módulos *PWM A* e seis módulos *PWM B. No* laboratório existem quatro placas idênticas ao circuito da Figura 24.. Este circuito de interface, além de realizar o condicionamento do sinal recebido por fibra ótica, gera o seu sinal complementar. Como pode ser visto na Figura 24 existem três entradas e seis saídas, ou seja, na saída estão os mesmos sinais recebidos da entrada além dos sinais invertidos (complementares).

Sendo assim, somando os quatro circuitos de interface é possível gerar :

- Seis PWMs A;

- Seis PWMs A complementares;

- Seis PWMs B;

- Seis PWMs B complementares;

Totalizando vinte e quatro sinais PWMs, dos quais doze são complementares dos outros doze. O esquemático deste circuito de interface esta detelhado no Anexo A.

#### 2.3.2 Conversor ANPC

O conversor ANPC da Figura 5 foi montado no LEAIM por três estudantes de graduação e um aluno de doutorado do curso de engenharia elétrica. O conversor é divido em uma parte de potência e outra responsável pelo comando das chaves. A parte de potência é composta principalmente pelo retificador de entrada, capacitores do barramento CC e pelas chaves de potência (IGBTs). A parte de comando é composta pelos drivers responsáveis pela transferência dos sinais de gatilho gerados no DSP para as chaves. Por motivos de segurança e ruído, as duas partes estão isoladas eletricamente uma da outra.

A Figura 25 na próxima página ilustra a montagem do circuito de potência.

Figura 25: Foto do Circuito de potência; (a) Retificador Trifásico e barramento DC; (b) Conversor ANPC.

Na Figura 26 está a imagem do *driver* utilizado para o disparo das chaves, com destaque para o transformador de isolamento entre o circuito de potência e o circuito de comando.

Figura 26:Foto do *driver* de acionamento do IGBT;(a) Entrada: Conector *latch* para cabo flat 16 pinos;(b)Transformador de isolamento; (c)Saída: Conector de 4 pinos para gatilho dos IGBTs

No Anexo B está o esquema utilizado para mapear as chaves e os sinais dos PWMs de acordo com a topologia no ANPC e a configuração dos *ePWM*s no DSP.

#### 2.3.3 LIMITAÇÕES DO PROJETO

Durante a execução da parte experimental do projeto, existiram fatores limitantes que devem ser considerados para a análise dos resultados. Dentre estes fatores se destacam:

- Foram considerados valores de tensão e de correntes relativamente baixos para os testes realizados na implementação do ANPC, diferentemente dos valores usados industrialmente:

- Foi realizada apenas a operação como inversor.

- O código gerado em C no PSim foi modificado para trabalhar com intervalos de tempo ao invés de níveis de tensão aplicados.

- Somente foi implementada a estratégia PWM-2.

#### 2.3.4 IMPLEMENTAÇÃO DA TÉCNICA DE MODULAÇÃO NO DSP

O DSP trabalha com uma única portadora triangular, com determinado valor de tempo. Como visto no Capitulo 1, em todas as estratégias de modulação consideradas há duas portadoras, sendo uma para comparação com a tensão de referência no semiciclo positivo e a outra para o semiciclo negativo. Para superar esta limitação, as tensões de referência foram modificadas durante o semiciclo negativo para que fosse possível a geração dos pulsos PWMs pela comparação com uma única triangular. A seguir está a condição gerada para superar esta limitação do DSP.

$$se v^* < 0$$

$$v^* = v^* + 1$$

De acordo com esta condição, durante o semiciclo negativo, as tensões de referência são deslocadas para o eixo positivo para assim, serem comparadas com a triangular gerada no DSP.

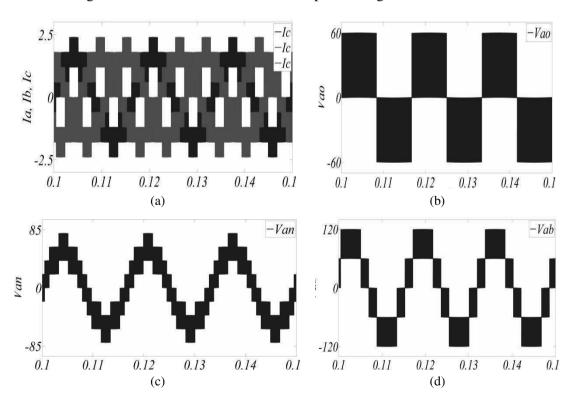

#### 2.4 RESULTADOS EXPERIMENTAIS

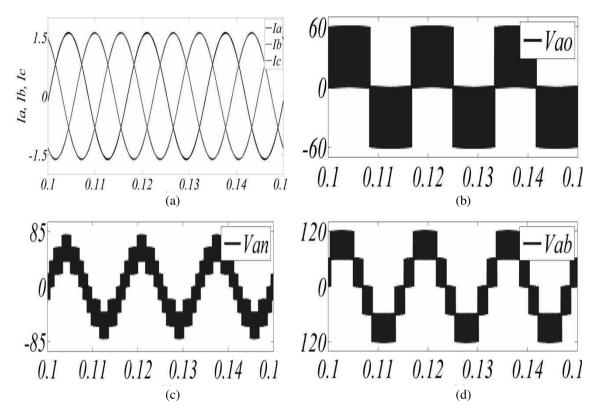

Aqui, estão os resultados experimentais do conversor ANPC. Os valores e as condições do circuito estão iguais aos das simulações. Foi considerada a frequência de chaveamento igual a 10kHz, e os dois tipos de carga trifásica em Y. Como observado na seção anterior, devido à limitação no número de canais *PWMs* do DSP, foi utilizada a estratégia de modulação *PWM-2*.

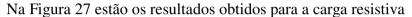

#### 2.4.1 CARGA RESISTIVA ( $R = 33,33 \Omega$ )

Figura 27: Resultados Experimentais para ANPC com estratégia PWM-2 e carga resistiva; (a)Correntes de linha; (b) Tensão de polo; (c) Tensão de fase; (d) Tensão de linha.

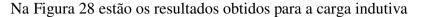

#### 2.4.2 CARGA INDUTIVA ( $R = 33,33 \Omega \, \text{E} \, \text{L} = 7,0 \, \text{MH}$ )

Figura 28: Resultados Experimentais para ANPC com estratégia PWM-2 e carga indutiva; (a)Correntes de linha; (b) Tensão de polo; (c) Tensão de fase; (d) Tensão de linha.

A partir de uma análise dos sinais obtidos experimentalmente é possível perceber as semelhanças entre estes resultados e os resultados gerados por simulação, usando a estratégia PWM-2.

Para todos os sinais de tensão a escala no osciloscópio foi ajustada para 100V/DIV. Comparando com as simulações realizadas, é possível perceber que as tensões estão balanceadas com valores de pico aproximadamente iguais a: 60 V (tensão de pólo), 80V (tensão de fase) e 120V(tensão de linha), de maneira semelhante ao simulado. Além disso, as correntes de linha também estão filtradas no caso da carga indutiva com um valor *rms* aproximadamente igual a 1,0A, também previsto na simulação.

#### 2.4.3 ANÁLISE DOS RESULTADOS EXPERIMENTAIS

De modo semelhante ao realizado aos resultados de simulação, foi feita análise da Taxa de Distorção Harmônica Total (THD) dos resultados experimentais obtidos. Os valores estão na Tabela 7.

| Estratégia  | Carga     | Ia     | $V_{ao}$ | $V_{an}$ | $V_{ab}$ |

|-------------|-----------|--------|----------|----------|----------|

| PWM -2      | Resistiva | 48,14% | 72,34%   | 50,18%   | 47,19%   |

| 1 44 141 -2 | Indutiva  | 2,15%  | 75,14%   | 51,48%   | 46,78%   |

Tabela 7: THD para a estratégia PWM-2 considerando os dois tipos de carga.

É possível verificar um maior THD para os resultados experimentais em comparação com os resultados de simulação obtidos. Isso se deve ao fato da presença de ruídos e pelo fato dos componentes usados na montagem não serem ideais. Entretanto, é possível perceber a mesma proporção entre estes resultados e os resultados obtidos na simulação (Tabela 6).

### 3 Considerações Finais

Este capítulo finaliza o trabalho de conclusão de curso com a análise gerada a partir do levantamento dos resultados obtidos e os possíveis trabalhos futuros. A revisão bibliográfica deste trabalho serviu para o entendimento das principais características das diferentes topologias de conversores multinível. Além disso, este projeto contribuiu para o aprofundamento teórico do aluno especificamente nas topologias de conversores multinível NPC e ANPC. Durante a etapa de simulação foi possível concretizar as três técnicas de modulação aplicadas ao conversor ANPC, e a partir da comparação entre elas, em nível de distorção harmônica (THD), foi comprovado que as técnicas têm resultados bem próximos.

Por outro lado, durante a parte experimental do projeto, o aluno conseguiu assimilar a geração de sinais de modulação através do DSP, entendendo a sua configuração e seu funcionamento como microprocessador. Os resultados experimentais demonstram um funcionamento esperado do conversor, para a estratégia utilizada.

#### 3.1 Trabalhos Futuros

Os resultados obtidos neste trabalho contribuem para análises futuras do conversor ANPC. Em uma próxima etapa, deseja-se analisar as perdas sobre os dispositivos de potência diante das diferentes técnicas de modulação aqui apresentadas, o que determina se uma técnica de modulação é mais eficiente do que a outra em termos da energia dissipada. Em seguida, deve-se realizar a operação do conversor como um retificador com elevado fator de potência inclusive em uma frequência de chaveamento de 720 Hz, objetivando a detecção e recuperação do conversor ante falhas.

#### REFERÊNCIAS BIBLIOGRÁFICAS

- [1] T. Brückner and S. Bernet, "Loss balancing in three-level voltage source inverters applying active NPC switches," Proc. IEEE PESC'01, 2001, pp. 1135–1140.

- [2] de Meireles, E.C.N.P, "Inversor Multinível Trifásico, Cascaded H-Bridge, Controlado por FPGA, Junho 2010,pp. 5-28. Dissertação.FEUP-Faculdade de Engenharia do Porto

- [3] Singh B.; Chandra A.; Al-Haddad, K.; Pandley, A. e Kothari, D.(2004). "A review of three phase improved Power quality ac-dc converters", IEEE Transactions on Industrial Electronics , 51(3): 641 -660.

- [4]J Rodriguez, J.S. Lai, F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications,", IEEE Transactions on Industrial Electronics, vol. 49,n°4,pp. 724-738, Aug 2002.

- [5] J.S. Lai, F. Z. Peng,; "Multilevel Converters a new breed of Power Converters," Conference Record of the 1995 IEEEIndustry Applications Conference. Thirtieth IAS Annual Meeting, IAS '95, vol. 3, pp. 2348-2356,8 -12 Oct, 1995.

- [6] Vieira, J.O., "Algoritmos de Controle para Conversores Eletrônicos de Potência Empregados em Sistemas de Geração Distribuída", Setembro 2008, pp. 10-21.

- [7] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point clamped PWM inverter," IEEE Trans. Ind. Application, vol. IA-17, pp. 518–523, Sept./Oct. 1981.

- [8] C. Attainese, M.Di Monaco, G. Tomasso, "Three-Phase Three Level Active NPC Converters for High Power Systems". SPEEDAM 2010 International Symposium on Power Electronics, Eletrical Drives, Automation and Motion

- [9] D. Floricau, E. Floricau and G. Gateau, "Three-level active NPC converter: PWM strategies and loss distribution", Proc. of IEEE IECON '08, 2008, pp. 3333-3338.

- [10] -[Microchip PIC24H Family Overview: High-Performance 16-Bit Microcontrollers.Disponível em: <a href="http://ww1.microchip.com/downloads/en/DeviceDoc/70166A.pdf">http://ww1.microchip.com/downloads/en/DeviceDoc/70166A.pdf</a>>. Acesso em 10 de Janeiro de 2013.]

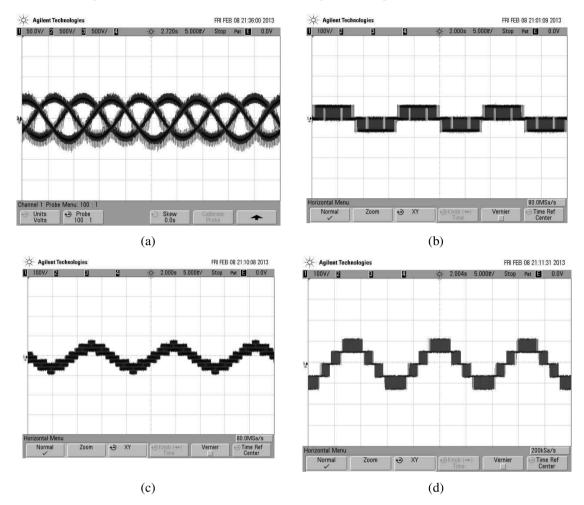

### APÊNDICE A – ESQUEMAS DO ANPC NO PSIM

#### Esquemático do conversor ANPC simulado no PSIM

Carga Resitiva

Carga Indutiva

# APÊNDICE B – LISTA DO MATERIAL USADO NA MONTAGEM DO CONVERSOR ANPC

- 1*x*Computador Pessoal (PC);

- 1x DSP modelo: *eZdsp* TMS320F28335;

- 1*x* Varivolt 420V;

- 9*x* IGBTs SKM 50GB123D;

- 18x Driver Semikron SKHI 10;

- 3x Diodos de disparo rápido SKKA 60F17;

- 4x Capacitores EPCOS 2,2 mF-450V;

- 6x Capacitores EPCOS Snubber 220 nF;

- 1x Dissipador P3 da Semikron;

- 1*x* Fonte de tensão chaveada STF 15-5 da POWERBRAS.

### APÊNDICE C – ROTINA PARA CALCULO DO *THD*

Aqui está a rotina gerada no Matlab para cálculo do THD de um sinal representado por pares de pontos salvos em arquivo com formato .txt.

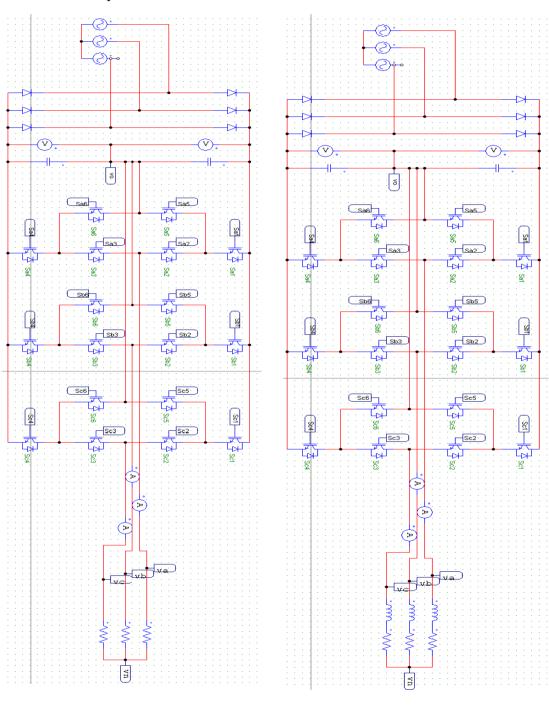

## ANEXO A – ESQUEMÁTICO PCI DO CIRCUITO DE INTERFACE

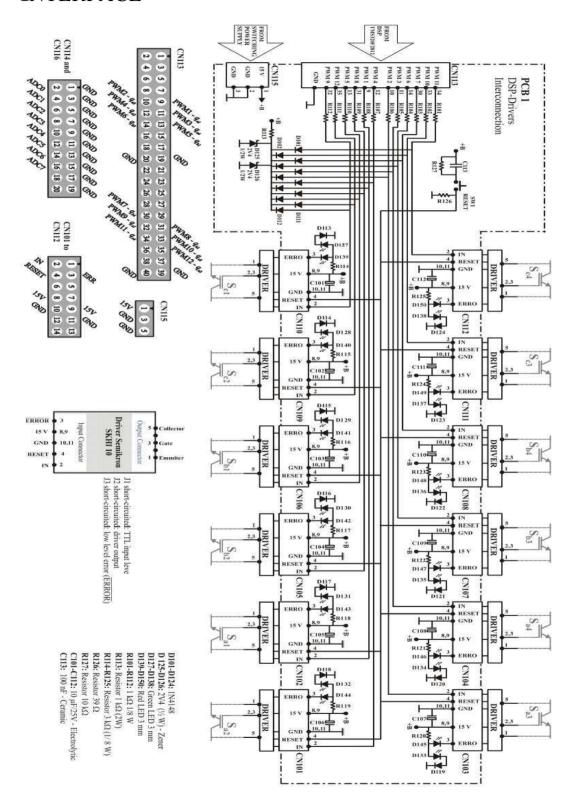

# ANEXO B – ESQUEMÁTICO DA MONTAGEM DO CIRCUITO DE POTÊNCIA E MAPEAMENTO DOS PWMS.