Saul Borges Nobre

# Implementação de um gerador de ambiente de verificação de IPs

Campina Grande, Brasil

25 de dezembro de 2018

#### Saul Borges Nobre

# Implementação de um gerador de ambiente de verificação de IPs

Trabalho de Conclusão de Curso submetido à Coordenação de Graduação em Engenharia Elétrica da Universidade Federal de Campina Grande, Campus Campina Grande, como parte dos requisitos necessários para obtenção do título de Graduado em Engenharia Elétrica.

Universidade Federal de Campina Grande - UFCG Centro de Engenharia Elétrica e Informática - CEEI Departamento de Engenharia Elétrica - DEE

Orientador: Gutemberg Gonçalves dos Santos Junior, D.Sc.

Campina Grande, Brasil 25 de dezembro de 2018

#### Saul Borges Nobre

# Implementação de um gerador de ambiente de verificação de IPs

Trabalho de Conclusão de Curso submetido à Coordenação de Graduação em Engenharia Elétrica da Universidade Federal de Campina Grande, Campus Campina Grande, como parte dos requisitos necessários para obtenção do título de Graduado em Engenharia Elétrica.

Trabalho aprovado em:

Gutemberg Gonçalves dos Santos Junior, D.Sc.

Orientador

Convidado

Campina Grande, Brasil 25 de dezembro de 2018

| Dedico este tra  | abalho aos meu | us amados pais, Jos           | sé Borges da Silv | a Filho e Maria |

|------------------|----------------|-------------------------------|-------------------|-----------------|

| BetâniaNobre Co. |                | ninha família e a n<br>Sousa. | ninha namorada    |                 |

| BetâniaNobre Co. |                |                               | ninha namorada    |                 |

| BetâniaNobre Co. |                |                               | ninha namorada    |                 |

| BetâniaNobre Co. |                |                               | ninha namorada    |                 |

| BetâniaNobre Co. |                |                               | ninha namorada    |                 |

### Agradecimentos

Primeiramente, agradeço a Deus pelo dom da vida. Em seguida, aos meus pais, José Filho e Maria Betania, por todo o apoio e suporte que me deram nessa longa jornada ate aqui e por sempre acreditarem que eu seria capaz.

À minha irmã, Débora, que embora não ter convivido comigo nos últimos anos, agradeço por ter me feito, inconscientemente, evoluir tanto no meu lado profissional quanto no lado pessoal.

À minha namorada, Nathália, agradeço por sempre ter estado comigo nas horas que precisei, sempre ter me ajudado a levantar quando cai, sempre ter me incentivado a ser melhor e evoluir. Agradeço por ter sido minha companheira e confidente, e acima de tudo, ter sido paciente.

Agradeço aos Pseudosmitos, grupo de estudantes, que sempre estiveram presentes ao longo dessa caminha, em varias noites de estudos e momentos de descontração. Agradeço , também, por todas as risadas que foram dadas, por todo apoio e incentivo que nos demos ao longo dessa jornada.

Agradeço aos grupos que participei ao longo da graduação, PET, RAMO Estudantil IEEE, X-MEN Lab, que me trouxeram engradecimento profissional e pessoal.

Aos meus professores, por todos os ensinamentos e oportunidades que me foram dadas, em especial ao professor Gutemberg, que me orientou nessa reta final e sempre acreditou no meu potencial.

### Resumo

O gerador de ambiente de verificação de IPs é uma ferramenta que deve auxiliar verificadores, de maneira a automatizar o processo de implementação de uma versão stub do ambiente. Este basei-se no uso de informações contidas em um arquivo e na determinação de um padrão a ser seguido para o stub do ambiente. O ambiente gerado possui um padrão comum e muito utilizado. A implementação deu-se utilizando a linguagem de alto nível Java.

Palavras-chaves: Java, Verificação, IP.

### **Abstract**

The IP verification environment generator is a tool that should aid verifiers in order to automate the process of implementing a textit stub version of the environment. This is based on the use of information contained in a file and on determining a pattern to be followed for the textit stub environment. The generated environment has a common and widely used standard and was implemented using the Java.

Key-words: Java, Verification, IP.

# Lista de ilustrações

| Figura 1 – | Lógica de funcionamento do gerador          | 2  |

|------------|---------------------------------------------|----|

| Figura 2 - | Fluxo do transição de dados                 | 2( |

| Figura 3 - | Exemplo de uma topologia de testbench       | 2  |

| Figura 4 - | Topologia de testbench utilizada no gerador | 24 |

| Figura 5 - | Fluxograma dos dados no gerador             | 39 |

## Lista de tabelas

| Tabela 1 – | Atributos e métodos da classe SpreadsheetReader  | 29 |

|------------|--------------------------------------------------|----|

| Tabela 2 – | Atributos e métodos da classe ParsedBlock        | 30 |

| Tabela 3 – | Atributos e métodos da classe ParsedSignal       | 30 |

| Tabela 4 - | Atributos e métodos da classe SignalTypeConstant | 31 |

| Tabela 5 - | Atributos e métodos da classe SignalType         | 32 |

| Tabela 6 - | Atributos e métodos da classe Signal             | 33 |

# Lista de Códigos

| 1  | Tipos de dados inteiros e suas sintaxes                              | 4  |

|----|----------------------------------------------------------------------|----|

| 2  | Sintaxe do uso de typedef                                            | 5  |

| 3  | Sintaxe do uso de parameter                                          | 6  |

| 4  | Sintaxe do uso de struct                                             | 6  |

| 5  | Sintaxe do uso de packed e unpacked                                  | 7  |

| 6  | Sintaxe do uso de packed e unpacked                                  | 8  |

| 7  | Sintaxe do uso de initial                                            | 9  |

| 8  | Sintaxe do uso de fork-join                                          | 10 |

| 9  | Sintaxe do uso de if-else                                            | 11 |

| 10 | Sintaxe do uso de case                                               | 11 |

| 11 | Sintaxe do uso das estruturas de <i>loops</i>                        | 12 |

| 12 | Sintaxe do uso de function                                           | 13 |

| 13 | Sintaxe do uso de task                                               | 13 |

| 14 | Sintaxe do uso de task para argumentos com valores padrões e pasagem |    |

|    | de argumento com o nome                                              | 14 |

| 15 | Sintaxe do uso de <i>clocking block</i>                              | 15 |

| 16 | Sintaxe do uso de mailbox                                            | 16 |

| 17 | Exemplo do uso dos padrões ANSI e não-ANSI                           | 17 |

| 18 | Exemplo de uso de program                                            | 18 |

| 19 | Exemplo de uso de interface                                          | 19 |

| 20 | Declaração de um interface como virtual                              | 19 |

| 21 | Declaração de um pacote                                              | 19 |

## Sumário

| 1     | INTRODUÇÃO 1                                |

|-------|---------------------------------------------|

| 2     | SYSTEMVERILOG                               |

| 2.1   | Tipos de dados                              |

| 2.1.1 | Inteiros                                    |

| 2.1.2 | Reais                                       |

| 2.1.3 | Tipos definidos pelo usuário                |

| 2.1.4 | Constante                                   |

| 2.1.5 | Estruturas (structures)                     |

| 2.1.6 | Packed e unpacked vetores                   |

| 2.1.7 | Vetores dinâmicos                           |

| 2.2   | Classes                                     |

| 2.3   | Processos                                   |

| 2.3.1 | Condicionais                                |

| 2.3.2 | Case                                        |

| 2.3.3 | Loops                                       |

| 2.3.4 | task e function                             |

| 2.4   | Clocking block                              |

| 2.4.1 | Sincronização e comunicação: mailboxes      |

| 2.5   | Construtores hierárquicos                   |

| 2.5.1 | Módulos                                     |

| 2.5.2 | Programas                                   |

| 2.5.3 | Interface                                   |

| 2.5.4 | Pacotes                                     |

| 3     | COMUNICAÇÃO ENTRE SYSTEMVERILOG E PYTHON 20 |

| 4     | AMBIENTE DE VERIFICAÇÃO                     |

| 5     | TESTBENCH MODELO 24                         |

| 6     | GERADOR DE TESTBENCH                        |

| 7     | CONSIDERAÇÕES FINAIS                        |

| 8     | ANEXO                                       |

| 8.1   | Códigos exemplos dos wrappers de comunicação Python - System-            |    |  |  |  |

|-------|--------------------------------------------------------------------------|----|--|--|--|

|       | Verilog                                                                  | 36 |  |  |  |

| 8.1.1 | Código exemplo em SystemVerilog usando DPI-C                             | 36 |  |  |  |

| 8.1.2 | Código exemplo em C servindo com wrappers                                | 38 |  |  |  |

| 8.1.3 | Código exemplo em Python que será acessado via o código em $8.1.2\ldots$ | 46 |  |  |  |

| 8.2   | Modelos utilizados para o testbench gerado                               | 47 |  |  |  |

| 8.2.1 | Modelo do testbench.sv                                                   | 47 |  |  |  |

| 8.2.2 | Modelo da interface.sv                                                   | 48 |  |  |  |

| 8.2.3 | Modelo do test.sv                                                        | 48 |  |  |  |

| 8.2.4 | Modelo do environment.sv                                                 | 49 |  |  |  |

| 8.2.5 | Modelo do driver.sv                                                      | 50 |  |  |  |

| 8.2.6 | Modelo do monitor.sv                                                     | 51 |  |  |  |

| 8.2.7 | Modelo do transaction.sv                                                 | 52 |  |  |  |

|       | REFERÊNCIAS                                                              | 53 |  |  |  |

## 1 Introdução

O processo de desenvolvimento de um IP é composto de etapas que podem ser divididas pelos setores presentes em uma empresa da área: modelagem, responsável por trazer o "modelo" digital do que o IP deverá fazer; design, o qual implementa a funcionalidade do IP em baixo nível; verificação, responsável por checar a corretude do design perante ao "modelo" entregue pela equipe de modelagem; e, por último, backend, setor encarregado de fazer a distribuição das células no próprio IP físico.

A totalidade do processo de desenvolvimento, entretanto, não possui um comportamento tão linear como o descrito, visto que muitas vezes as próprias especificações, como o número de bits das portas ou até mesmo a existência ou não de determinada porta, dos blocos que irão compor o IP ainda não foram determinadas de maneira definitiva. Com isso, tem-se versões de modelos e de design intermediárias que também passarão por uma verificação.

Essas mudanças podem ser desde a adaptação de algoritmo usado ou de interface. As mudanças de interface ocorrem principalmente na quantidade de bits das entradas e saídas dos blocos que compõem o IP, mas podem abranger também a alteração em nomes de sinais e adição ou retirada de sinais entrada/saídas de blocos. Para cada mudança na interface de algum bloco é necessário a mudança no ambiente de verificação para que o bloco e o ambiente sejam compatíveis e verificados de maneira homogênea.

Porém, tais mudanças demandam tempo dos engenheiros de verificação, e muitas vezes são mudanças mecânicas. Neste contexto e, considerando o fato que um ambiente de verificação possui estruturas básicas que demandam tempo para serem implementadas, é proposto e descrito neste trabalho a ideia e o algorítimo de um gerador, de modo que tanto as mudanças recorrentes no processo de desenvolvimento quanto a criação da estrutura comum sejam automatizadas, tornando assim o desenvolvimento mais eficiente e mais ágil.

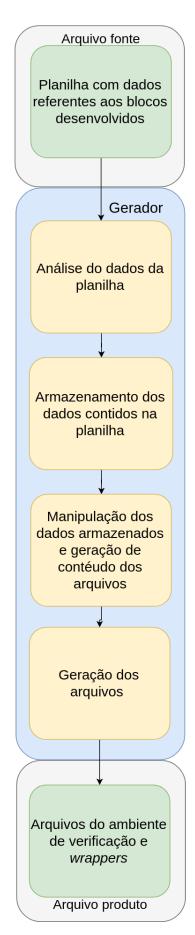

O gerador proposto baseia-se de um modelo de *testbench* comum com algumas modificações, como, por exemplo, a implementação da possibilidade de utilizar-se de modelos em alto nível para realizar a verificação ciclo a ciclo, possibilitando uma melhor precisão para os verificadores. Assim, a aplicação proposta possui uma lógica de funcionamento simples, que é ilustrada na Figura 1.

Figura 1 – Lógica de funcionamento do gerador

## 2 SystemVerilog

System Verilog, que foi padronizado como IEEE 1800, é um linguagem de descrição e de verificação de hardware usada para simular, testar e implementar sistemas eletrônicos. É comumente usada pela indústria de semicondutores e eletrônica como uma evolução do Verilog.

A sua padronização se deu com uma doação da linguagem Superlog para Accellera em 2002. As funções que dão suporte à parte de verificação foram baseadas na linguagem OpenVera doada pela Synopsys. Em 2005, SystemVerilog foi adotado como padrão IEEE 1800-2005, e apenas em 2009, o padrão recebeu como acréscimo a base padrão do Verilog (IEEE 1364-2005), criando assim o padrão IEEE 1800-2009.

System Verilog possibilita o uso de uma linguagem unificada para abstração e especificação de detalhes do design, especificação de assertions, cobertura e verificação baseada em metodologias manuais ou automáticas. Esta linguagem oferece também interface de programação de aplicativos (Application Programming Interfaces - API) para cobertura e assertions, uma API independente do fornecedor para acessar formatos de arquivos de forma de onda registrados, e uma interface de programação direta (Direct Programming Interface - DPI) para acessar as funcionalidades registradas.

Neste capitulo serão abordadas e explicadas algumas funções presentes na linguagem, principalmente as mais usadas para possibilitar a implementação dos componentes de um ambiente de verificação, com acréscimo de algumas funcionalidades que podem tornar-se úteis, e que foram implementadas no gerador.

#### 2.1 Tipos de dados

Em System Verilog podemos ter a representação de quatro valores lógicos, são eles:

- 0→ Representa o zero lógico, ou condição falsa;

- 1→ Representa o um lógico, ou condição verdadeira;

- X→ Representa um valor lógico desconhecido;

- $\mathbb{Z} \rightarrow$  Representa o estado de alta impedância.

Na maioria dos casos o efeito de valores x e z será o mesmo. Para se declarar uma variável com os quatro estados utiliza-se a palavra-chave logic. Esse termo pode ser

usado para declarar objetos e para construir outros tipos de dados partindo de um tipo existente.

#### 2.1.1 Inteiros

System Verilog provê um conjunto de dados que podem ser considerados inteiros, podendo dividido-los em inteiros de dois estados e de quatro estados, sendo eles:

- <u>Dois estados</u>: shortint, int, longint, byte, bit. Que possuem respectivamente, 16 bits inteiro com sinal, 32 bits inteiro com sinal, 64 bits inteiro com sinal, 8 bit inteiro com sinal ou caractere ASIC;

- Quatro estados: logic, ref, integer, time. Desses tipos, os únicos que já possuem tamanhos previamente definidos são integer, que possuem 32-bit inteiros com sinal e time, 64-bits inteiros com sinal. Nos demais, os tamanhos serão definidos pelo usuário, formando, assim, um vetor.

Alguns desses tipos de dados inteiros também podem ser declarados como "com sinal" (signed) e "sem sinal" (unsigned). Por exemplo, os dados tipos byte, shortint, int, interger, e longint, são tipicamente signed, assim como outros tipos tem seus padrões como unsigned. Para se declarar algum dos tipos inteiros como signed ou unsigned, basta utilizar as palavras chaves signed e unsigned após a declaração do tipo de dado.

```

//Inteiros: dois estados

1

2

signed

int

a;

unsigned shortint b;

3

signed

longint c;

4

signed

byte

5

d;

signed

bit

6

7

//Inteiros: quatro estatos

8

9

logic

f;

10

ref

g;

11

integer

h;

time

i;

12

```

Código 1 – Tipos de dados inteiros e suas sintaxes

#### 2.1.2 Reais

O tipo real seria o equivalente ao double em C. Em comparação com os tipos inteiros, existem algumas diferenças. A primeira é a capacidade de representação numérica em ponto flutuante, o que conta como ponto positivo, porém, negativamente, alguns dos

outros artifícios da linguagem não podem ser utilizados como: controle de eventos de borda, seleção de bits, entre outros.

A conversão de um **real** para o tipo inteiro se dá por arredondamento para o valor inteiro mais próximo, ou seja, se a parte fracionada estiver abaixo de 0.5, ele arredondará para zero, e caso esteja igual ou maior, arredondará para cima.

#### 2.1.3 Tipos definidos pelo usuário

Em System Verilog podem-se declarar tipos de dados de modo que eles venham a ser definidos pelo usuário usando a sintaxe typedef. De forma geral, o funcionamento se dá a partir da utilização de um tipo previamente existente, podendo esse ser uma classe ou um tipo de dado, e atribuindo um novo nome a esse.

```

class model;

typedef real data_r;

data_r data; // data will be from de type real

endclass

```

Código 2 – Sintaxe do uso de typedef

Quando se é utilizado typedef partindo de um tipo já existente, não é possível acessar os atributos internos deste, ou seja, não possuem referências hierárquicas com o tipo que foi utilizado. Tipos declarados, como interface, tem possível o acesso às portas, pois estes não são considerados uma referência hierárquica. Também é possível usar typedef para estruturas de dados como struct, enum e union. É importante destacar que a declaração deve ser feita no escopo (scope) do bloco.

#### 2.1.4 Constante

Constante é um tipo de dado ou objeto definido no tempo de elaboração, ou seja, não pode ser alterado durante a simulação. Esse tipo pode ser usado para declarar tamanhos de portas em módulos, interfaces, classes, pacotes, etc.

Deve-se notar que o local no qual a constante é declarada afetará seu acesso, como por exemplo, se esta for declarada em uma região de escope (scope), o acesso poderá ser feito em qualquer módulo, classe etc, que esteja incluído na simulação. Porém, o mesmo raciocínio não é válido quando definido dentro de uma classe, visto que só terá permissão de acesso à constante as propriedades e os métodos da classe, o mesmo valendo para outros tipos de estruturas.

É importante, ainda, a diferenciação entre const e parameter. A primeira pode ser definida durante a simulação, ao contrário da segunda, que será definida durante a elaboração dos arquivos.

```

//parâmetros que serão globais;

1

parameter PARAM um = 'd1;

2

parameter param_dois = 'd5;

3

4

//classes podem ter seus próprios parâmetros sendo passados atras da sintaxe:

5

//#(...);

6

7

class example_param #(

= 'd12;

8

parameter param_tres

9

parameter param_quatro = -'sd15; //essa sintaxe é utilizada para atribuir

//valores com sinal dentro do parâmetro

10

);

11

12

13

. . .

endclass

14

15

16

```

Código 3 - Sintaxe do uso de parameter

#### 2.1.5 Estruturas (structures)

O tipo estrutura (struct) é uma coleção de tipos de dados que pode ser referenciados como um único tipo e seus membros podem ser acessados de forma hierárquica.

```

struct (

1

real

code;

2

bit [5:0]; b;

3

4

) exemplo;

5

exemplo.code = 123;

6

7

typedef struct(

8

logic

9

valid;

int

count;

10

) exemplo_1;

11

12

exemplo_1 control; // control é do tipo exemplo_1, que é uma struct

13

//com dois atributos: valid e count.

14

```

Código 4 – Sintaxe do uso de struct

Estruturas de dados possuem o padrão "unpacked" tornando-as dependentes do packing do tipo de dados presentes dentro de sua declaração. Quando uma estrutura é declarada explicitamente como packed, os bits correspondentes são agrupados juntos na memória, sem espaços.

#### 2.1.6 Packed e unpacked vetores

Para o tipo vetor, não existe nenhuma palavra-chave a ser usada em sua implementação, utilizando-se dos tipos mais básicos, ditos como não agregados e que foram mencionados anteriormente. Esses termos são designados apenas para referência de como os vetores são declarados, como, por exemplo, se suas dimensões são declaradas antes do nome da variável, isso a torna um vetor *packed*, e caso seja delcarada após, a torna *unpacked*.

A diferença entre tais métodos é a forma de como os dados serão salvos na memória, pois vetores *packed* são armazenadas de forma sequencial e, em contrapartida, os *unpacked* podem ou não ser salvos sem espaços entre seus elementos na memória.

Vetores declarados na forma packed têm como dimensão máxima 65536 bits e só podem ser utilizados para tipos de dados simples, como: bit, logic e reg. Por outro lado, os vetores unpacked podem ser de qualquer tipo e possuem a dimensão máxima de 16777216 elementos.

Uma variável do tipo vetor pode ter numa mesma declaração tamanho *packed* e *unpacked*. Quanto à velocidade de variação, esta segue o mesmo padrão de C, no qual a dimensão mais a direita varia mais rapidamente, salientando que as dimensões *packed* variam mais rápido que as *unpacked*.

Para acessar um elemento ou valor de um vetor, é suficiente a utilização do *index* do elemento; o mesmo sendo válido para as dimensões *packeds*, seguindo o mesmo critério de C, ou seja que a dimensão que varia mais rápido, sempre estará mais a direita, assim o acesso se dá a partir da inserção do *index* após todas as dimensões *unpacked*.

```

bit [7:0] clear;

//variavel packed

1

real data [255:0];

//variavel unpacked

2

real [10:0] values [16:0];

//variavel unpacked e packed

3

4

values[0]

//atribui 1 para todos os valores packed, cados 0-10;

5

= 1;

values[0][1]

= 2;

//atribui 2 para um único elemento

```

Código 5 - Sintaxe do uso de packed e unpacked

#### 2.1.7 Vetores dinâmicos

Vetores dinâmicos não possuem um tamanho definido em sua declaração, ou seja, podem variar de tamanho durante a simulação. É importante ressaltar que não é possível a utilização desse artifício para vetores com dimensões exclusivamente packeds.

Para declarar os vetores de maneira dinâmica, é necessário apenas colocar colchetes vazios na dimensão mais a esquerda. O construtor utiliza-se do new[] para definir o

tamanho do vetor desejado. O vetor passa, ainda, a possuir dois métodos já existentes da própria linguagem: size(), que retorna o tamanho atual do vetor e, delete(), que deleta o vetor deixando-o com zero elementos.

#### 2.2 Classes

System Verilog também possui suporte ao uso de classe. As variáveis contidas numa classe são chamadas de propriedades, e as task e functions, ou seja, sub-rotinas, são chamadas de métodos. A classe, assim como em C, comporta-se como um tipo de dado que pode ser instanciado, e esta instanciação é chamada de objeto.

Uma classe também pode conter os próprios parâmetros, ou seja, no momento da sua instanciação pode-se passar parâmetros que serão utilizados em suas propriedades.

O acesso das propriedades e dos métodos acontece da maneira como é demostrado no Código 6. Os construtores de classe em *System Verilog* utilizam-se de palavra-chave que torna um dos métodos, chamado de new, em construtor. Assim, enquanto é criada é chamada a função new(). Como o construtor se comporta como uma função, ele pode receber argumentos em sua chamada, como mostrado em Código 6.

```

class model ;

1

2

//propriedade da classe

3

bit [2:0] pos;

logic

valid;

4

5

//construtor da classe ou inicialização

6

7

function new();

pos = 3'd0;

8

valid = 1;

9

endfunction

10

11

//métodos

12

13

function void reset();

pos = 'd1;

14

valid = 0;

15

16

endfunction

17

function real cal (input real a, input real b);

18

19

cal = a*b;

endfunction : cal

20

21

endclass : model

22

```

Código 6 - Sintaxe do uso de packed e unpacked

Uma outra maneira de acessar as propriedade da classe, ao fazer uma implementação dentro da classe, é o uso da palavra-chave this, a qual evita possíveis ambiguidades no momento da implementação e simulação.

#### 2.3 Processos

Em System Verilog os processos podem ser divididos em: procedimentos estruturados, declaração de bloco e controle de temporização.

O foco desta seção é percorrer, de forma geral, as funções de *System Verilog* que estarão presentes no código resultante do gerador, motivo pelo qual, só serão mencionadas as funções que foram utilizadas no modelo gerado.

Os procedimentos estruturados podem ser realizados através de: initial, always, final, task e function. initial é um procedimento que só será executado uma única vez, sendo utilizado, de forma geral, para inicialização de variáveis ou códigos que devem ser executados somente uma única vez. Sua sintaxe pode ser vista no Código 7. task e function serão explicados adiante.

```

module example();

initial begin

//códigos que serão executados apenas uma vez no inicio da simulação

//...

end

endmodule

```

Código 7 – Sintaxe do uso de initial

Declarações de blocos são uma maneira de agrupar declarações de modo que comportem-se como uma única declaração. Dessa forma, temos dois tipos: blocos sequenciais (begin-end) e blocos paralelo fork-join.

Em blocos sequenciais todas as declarações devem estar contidas entre begin e end, e serão executas pela ordem que foram implementadas, o mesmo sendo válido para atrasos colocados dentro do bloco.

Blocos paralelos são declarados atraves de fork e join, join\_any, join\_none. Todas as declarações internas serão executadas ao mesmo tempo, de forma que, nesse bloco, pode-se colocar um atraso para prover uma ordem temporal na sua execução. Este tipo não pode ser utilizado dentro de funções. Como mencionado anteriormente, existe mais de uma sintaxe para fechar o bloco, cada uma com sua devida peculiaridade:

- <u>join</u>: O processo do bloco só será finalizado após todos os processos lançados pelas declarações internas do bloco terem sido concluída;

- join\_any: O processo do bloco será finalizado quando um dos processos lançados pelas declarações internas do bloco for concluído;

• <u>join\_none</u>: Os processos do bloco serão executados em paralelo com o processo que iniciou o bloco (processo pai), e o bloco só iniciará seus processos internos após o processo pai ter realizado uma atribuição bloqueante.

Os tipos de blocos não são mutualmente excludentes, ou seja, dentro de um bloco paralelo podem conter blocos sequenciais e vice-versa, como pode ser visto em sua sintaxe no Código 8.

```

//Neste exemplo é possível ver um loop dentro de um loop

1

2

//para o primeiro fork ele irá ser concluido após qualquer

//um dos seus processos terminarem, neste caso tem-se só

3

//um processo. O segundo fork ele irá esperar que todos

4

5

//os seus subprocessos sejam finalizados.

fork

6

fork

7

$display("loop dentro de um loop");

8

9

join_any

10

fork

11

$display("loop dentro de um loop");

12

13

join

join

14

```

Código 8 – Sintaxe do uso de fork-join

A linguagem System Verilog fornece também estruturas que possam controlar os processos, como aguarda-lo terminar ou finaliza-lo enquanto esteja sendo executado. As declarações wait, wait fork e wait\_order dão o controle para esperar que um processo seja encerrado.

A simples declaração wait(expressão) irá esperar pelo fim do processo "expressão". Por sua vez, wait fork irá esperar que todos os processos, sem levar em consideração os subprocessos iniciado pelo fork, sejam concluídos.

#### 2.3.1 Condicionais

Estruturas condicionais em *SystemVerilog* são semelhantes às existentes em C, ou seja, elas são feitas através de estruturas de if-else, com as mesmas capacidade de intercalação e sequências, como pode ser visto no Código 9.

#### 2.3.2 *Case*

Há, ainda, em *System Verilog*, as estruturas de *case*, as quais são uma estrutura que se baseia na ideia do switch-case de C, que compara quando uma expressão é igual a outra, realizando assim, uma operação desejada, como é mostrado no Código 10.

```

//Exemplo de estrutura de condição em sequência

1

2

if (idx > 0) begin

3

if (val < 0) begin

result = idx+val;

4

5

end else begin

6

result = idx-val;

7

end

end else if(idx == 0) begin

8

9

result = result + idx;

10

end

```

Código 9 – Sintaxe do uso de if-else

```

1

logic [6:0] pos;

logic [15:0] values;

2

3

case (values)

4

5

16'd0: result = 7'd1;

6

16'd1: result = 7'd2;

16'd2: result = 7'd3;

7

16'd3: result = 7'd4;

8

9

16'd4: result = 7'd1;

16'd5: result = 7'd1;

10

16'd6: result = 7'd1;

11

16'd7: result = 7'd1;

12

16'd8: result = 7'd1;

13

16'd9: result = 7'd1;

14

default result = 'x;

15

16

endcase

```

Código 10 – Sintaxe do uso de case

#### 2.3.3 *Loops*

Loops, ou estruturas de repetição, também são suportados por System Verilog. Estas estruturas são: for-loop, forever, repeat, entre outras, porém, somente as mencionadas serão detalhadas no decorrer do trabalho.

Cada uma dessas estruturas tem sua peculiaridade, o que define, caso a caso, qual delas é a melhor opção. A estrutura for-loop é a única que contém em sua declaração uma inicialização de variável, a qual servirá para a condição de parada. O forever, por sua vez, não tem condição de parada, ou seja, é utilizada principalmente em situações nas quais se deseja *loops* infinitos. É importante salientar que sua utilização deve ser acompanha de algum controle de tempo ou outra função que consiga desabilitar o *loop*, para que assim evite repetições infinitas com zero de atraso, o que resultaria no travamento do escalonador da simulação com aquele processo.

A estrutura repeat tem a peculiaridade de receber o número de vezes que a sua declaração terá que ser executada, sendo, dessa forma, útil em situação na qual já sabe

quantas vezes será necessária a repetição. Um exemplo do uso dessas estruturas pode ser encontrado no Código 11.

```

//exemplo da estrutura de for-loop

1

for (int i = 0; i < MAX; i++) begin

2

//codigo que deverá ser executado MAX vezes

3

4

//..

5

end

6

7

//exemplo da estrutura de forever

8

forever begin

9

//código que deverá ser repetido infinitas vezes

10

11

12

end

13

//exemplo da estrutura repeat

14

15

repeat(10) @(posedge clk) //a thread que esteja sendo executa esperará por 10

16

// eventos de clk, para assim de o procedimento na

// na execução do código

17

```

Código 11 – Sintaxe do uso das estruturas de loops

#### 2.3.4 task e function

task e function são estruturas que também podem ser chamadas de sub-rotinas, permitindo a execução de procedimentos comuns em diferentes lugares do código. Ainda, realizam a função de "modularização" do código, fazendo com que grandes processos possam ser divididos em processos menores, possibilitando que o debug seja realizado mais facilmente.

As principais diferenças entre task e function são:

- As declarações contidas dento de function serão executadas em uma unidade de tempo de simulação, já a task, pode conter uma declaração de controle tempo;

- Uma function não pode iniciar uma task, porém uma task pode inciar outras task e também function;

- Uma task não possui retorno, ou seja, sempre será "void", ao contrário de function, que pode ou não ter retorno.

O padrão no momento de declaração de uma task é que ela será do tipo static, sendo assim, todos os seus valores sendo declarados de maneira estática. Esta tarefa também pode ser declarada de maneira que venha a ter um armazenamento automático, utilizando-se da palavra-chave automatic em sua declaração ou declarando-a dentro de

estruturas que são, por padrão, automatic. A seu turno, task que não são estáticas possuem suas variáveis internas e suas declarações alocadas dinamicamente. Quando declaradas como automatic não se pode acessar atributos internos de maneira hierárquica.

O uso de function não deve conter nenhuma declaração de controle de tempo, uma vez que não deve fazer uso de chamada de task, a menos que esta task possua alguma declaração de controlador de tempo.

```

//exemplo de função com retorno do tipo

1

2

//void

function func_01 (input logic a, output int b);

3

4

endfunction

5

6

7

//exemplo de função com retorno

function logic [5:0] func_02 (input logic a, output logic b);

8

9

10

return c

endfunction

11

12

//exemplo de determinar o retorno da função

13

//utilizando o nome da função

14

function logic [5:0] func_03 (input logic a, output logic b);

15

16

func_03 = 2 * a + b;

17

endfunction

18

```

Código 12 – Sintaxe do uso de function

Como pode ser visto no Código 12, a declaração pode incluir o tipo de dados de retorno ou ter uma declaração implícita, que será considerada do tipo *void*. A declaração de uma task se dá de maneira semelhante, vide Código 13.

```

//Exemplo de declaração de uma task. É importante mencionar

//que a task pode ter algum mecanismo de controle de tempo,

//sendo assim possivel a declara de um @(posedge ...)

task my_task (input logic a, input logic b);

...

b = a;

endtask

```

Código 13 – Sintaxe do uso de task

Os argumentos para essas estruturas podem ser passados por valor, que é o modo mais comum de passar argumentos para sub-rotinas. Este consiste em passar um objeto para a função. Uma outra maneira é a passagem por referência, na qual diferente da anterior, que copia o valor passado para o escopo da função, aquele modo acessa diretamente o argumento original. Para tanto, deve-se usar a palavra-chave ref.

A passagem por referência tem condições para ser utilizada: os tipos e tamanhos que foram declarados tem que ser os mesmos que estão sendo utilizados pelo argumento passado, e não podem ser do tipo static. Assim, os únicos elementos que podem utilizar-se desse artificio são: variável, uma propriedade de uma classe, membro de uma estrutura unpacked ou um elemento de um vetor unpacked. Importante notar que o uso de passagem por referência deve ocorrer apenas em variáveis automatic.

As function e as task podem possuir em sua declarações valores padrão para seus argumentos, ou seja, caso não seja atribuído nenhum valor a algum deles, esses terão o valor utilizado na implementação. Um outro artifício que pode ser usado no momento da sua instanciação é a atribuição dos argumentos usando os seus próprios nomes, evitando, assim, uma possível inversão na ordem de instanciação, como demostrado no código 14.

```

//exemplo de função com valores padrões de arugmentos

1

2

task write(int valid = 0, int data, int o_ready=0);

3

endtask

4

5

//exemplo de instanciação utilizando os nomes dos argumentos

6

7

//e não a ordem

write writa_inst(

8

9

.valid

(1),

10

.data

(13),

.o_ready ()

11

)

12

```

Código 14 – Sintaxe do uso de task para argumentos com valores padrões e pasagem de argumento com o nome

#### 2.4 Clocking block

Como será mencionado mais adiante, existem estruturas que podem ser utilizadas para conectar as portas e especificar sinais pelos quais o testbench irá se comunicar com o dispositivo que está sendo testado. Porém, no tocante ao controle de tempo, através de um clock(em tradução literal: relógio), o clocking block é bastante eficiente quando comparado a outras estruturas.

Visando ter esse controle de sincronização, tem-se a estrutura de um *clocking block*, que é declarado entre as palavras-chaves **clocking-endclocking**, fazendo com que os *clocking blocks* se tornem uma chave importante em metodologias que baseiam-se em ciclos, dando a possibilidade dos testes tenham noção de ciclo e de transação.

Clocking blocks separam detalhes de tempo e de sincronização das informações estruturais, funcionais e elementos procedurais de um testbench. Com isso, é possível realizar as operações de eventos síncronos, amostragem de sinais e drives síncronos.

Em suma, com essa estrutura é possível determinar o momento em que deverá ser feita a leitura de uma sinal e/ou o momento que deverá ser atualizados os sinais com novos valores. Desta forma, um dos seus principais usos é evitar que ocorra uma condição de corrida no seu testbench. A sua estrutura é simples, porém é importante mencionar que existem outras opções além das vistas no Código 15, que podem ser encontradas no manual de Systemverilog.

```

//exemplo de clocking block. clk é o sinal que o clocking block deverá usar

1

//como base para realizar as mudanças do sinal. Os sinais podem ser declarados

2

3

//como inout, input e ouput.

4

clocking cb @(posedge clk);

default input #1step output #1step //os valores de #1step referen-se ao

5

//atraso ou adiantamento dos sinais

6

//declaração das portas da interface

7

inout i_valid;

8

9

inout i_data;

10

inout o_valid;

11

inout o valid;

12

endclocking :cb

13

```

Código 15 – Sintaxe do uso de clocking block

#### 2.4.1 Sincronização e comunicação: mailboxes

Quando há necessidade de fazer uma comunicação entre os processos, pode-se utilizar uma classe já existente de *Systemverilog*, mailbox. Essa classe funciona como uma caixa de correios, na qual alguém (processo) pode colocar algo dentro e outra pessoa (outro processo) pode retirar o que foi colocado. Algo importante que torna-se útil para sincronização entre os processos é o fato que quando a *mailbox* está cheia, o processo que tentar colocar algo dentro irá entrar em estado de suspensão, até que outro processo venha e retire um elemento de dentro da *mailbox*, realizando, com isso, a sincronização entre dois processos.

A classe mailbox, por ser uma classe própria de *Systemverilog*, possui os seguintes métodos:

- Construtor: new();

- Inserir item dentro da mailbox: put();

- Tentar inserir um item dentro da mailbox sem bloquear o processo: try put();

- Retirar um item: put() ou peek();

- Tentar retirar um item sem bloquear o processo try\_put() ou try\_peek();

• Retornar a quantidade de itens dentro da mailbox: num().

```

program test();

1

2

mailbox t2d; //para a declaração de uma mailbox de um tipo especifico

//usar a seguinte sintaxe:

3

mailbox #(<tipo_de_dado_definido>) t2d;

4

5

initial begin

6

drive = new(t2d);

7

8

9

int a = 23;

10

t2d = new(1); //pode-se incluir ou não o número de espaços que terá a

11

//mailbox, neste caso ela terá um único espaço. Caso deseje

12

13

//um numero infinito de espaços não deve ser inserido nenhum

// número

14

15

t2d.put(a);

16

17

end

18

19

endprogram

20

21

22

class drive;

23

mailbox t2d;

24

int

a;

25

function new(mailbox in_t2d);

26

27

this.t2d = in_t2d;

28

endfunction

29

task run();

30

31

t2d.get(a);

endtask

32

endclass

33

```

Código 16 – Sintaxe do uso de mailbox

#### 2.5 Construtores hierárquicos

Em System Verilog existem diferentes construtores hierárquicos, ou estruturas, que podem ser acessados de maneira hierárquica ou são utilizados para encapsular dados, funcionalidades, temporização etc. Alguns deles são: módulos (module), programas (programs), interface (interface) e pacotes (packages). Cada uma dessas estruturas têm suas peculiaridades, que serão explanadas mais adiante.

#### 2.5.1 Módulos

Módulos (module) são as estruturas básicas em *SystemVerilog* para um *design*. Possuem como principal objetivo encapsular dados, funcionalidades e temporização de

objetos digitais, ou seja, os componentes de baixo nível, sejam portas lógicas simples ou complexas. De forma geral, existem duas maneiras de fazer a declaração de um módulo, ANSI e não-ANSI, ambas maneiras são demostradas no Código 17.

```

//declaração com o padrão não-ANSI

1

2

module example(a,b,c,d,e);

3

[3:0] a;

4

input

input

[5:0] b;

5

input

[10:0] c;

6

output

[8:0] d;

7

output

[15:0] e;

8

//...

9

10

11

endmodule

12

//declaração com o padrão ANSI

13

14

module example(

15

input

[3:0] a,

16

input

[5:0] b,

17

18

input

[10:0] c,,;

output

[8:0] d,

19

[15:0] e

20

output

);

21

22

//...

23

endmodule

24

```

Código 17 – Exemplo do uso dos padrões ANSI e não-ANSI

#### 2.5.2 Programas

Enquanto o foco de módulos é a descrição do hardware propriamente dito, os programas (programs) são voltados ao suporte no *testbench*, pois para isto não é necessário o foco em nível de hardware, não sendo relevantes fios, estruturas hierárquicas etc. Assim, os blocos chamados de programas (programs) possuem os seguintes objetivos:

- Proveem um ponto de entrada para o execução dos testbenchs;

- Criam um escopo para encapsular dados, task e funções;

Junto com os *clocking blocks*, os programas proveem interações livres de condições de corrida entre o design e o *testbench* e ainda possibilitam abstrações de ciclos e transações. Um exemplo da implementação de um programa é mostrado no Código 18.

```

//exemplo de uso da estrutura de program

1

program test #(

2

parameter MAX = 'd10,

3

4

parameter SIZE = 'd5

5

6

)(

7

input clk,

input [15:0] dado,

8

9

int

10

count,

);

11

12

//aqui pode ser chamada os construtores do ambiente (environment) do

13

//testbench

14

initial begin

15

//..

16

17

end

endprogram

18

```

Código 18 – Exemplo de uso de program

#### 2.5.3 Interface

A sua principal função é a comunicação entre blocos, abrangendo tanto alto nível quanto baixo nível. Uma interface também pode conter parâmetros, constantes, funções e *tasks*, ou seja, essa também pode comportar-se como uma classe e consegue realizar a comunicação entre blocos de maneira suave. Um exemplo de sua implementação e uso pode ser visto no Código 19

Uma interface pode ainda ser declarada como virtual, fazendo com que se possa manipular os sinais da interface sem referenciar os sinais atuais. Estes tipos de interfaces também podem ser passados como argumentos de tasks, funções ou métodos. A declaração de uma interface como virtual é feita como é mostrado no Código 20

É importante salientar que uma interface virtual não pode ser usada como porta e nem em assigns, ou lista de sensibilidade. Para que sua utilização seja possível nestes cenários, a interface deve conter ou um clocking block ou um driver que esteja ligado a uma interface que não seja virtual.

#### 2.5.4 Pacotes

Um outro mecanismo para compartilhar parâmetros, dados, *tasks* e funções entre módulos, interfaces e programas, são os pacotes (ou packages). A declaração de um package cria um escopo que contém as declarações que serão compartilhadas. Como pode ser visto no Código 21.

```

interface block_if (

1

2

input logic clk

3

4

//declaração dos sinais

5

6

wire i_valid;

7

wire i_data;

//...

8

wire o_valid;

9

wire o_data;

10

11

//...

12

endinterface

13

14

module top():

15

block_if if_b; //declaração de uma interface para o block

16

17

18

block a_block(

.i_valid(if_b.i_valid),

19

.i_data(if_b.i_data),

20

21

.o_valid(if_b.o_valid),

22

23

.o_data(if_b.o_data)

)

24

endmodule

25

```

Código 19 – Exemplo de uso de interface

```

virtual blcok_if vif_b;

```

Código 20 – Declaração de um interface como virtual

```

//exemplo de implementação de um package

1

2

package example;

class util 1;

3

int a;

4

real b;

5

6

function new(input int in_a, input real in_b);

7

this.a = in_a;

8

9

this.b = in_b;

10

endfunction

11

function sum(input int c, output real d);

12

13

d = a + b + c;

endfunction

14

endclass

15

endpackage : example

16

```

Código 21 – Declaração de um pacote

# 3 Comunicação entre *SystemVerilog* e Python

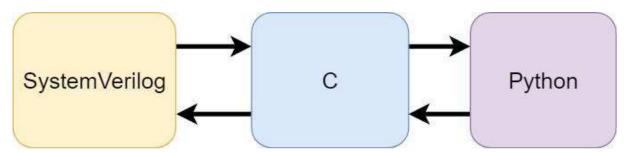

O gerador foi desenvolvido partindo do princípio que o modelo de referência estaria em Python e poderia ser comparado com o DUT ciclo a ciclo. Para que isso fosse possível, foram desenvolvidas cascas (*wrappers*) que fariam as traduções de uma linguagem para outra.

Como ponte da linguagem de alto nível para a linguagem de baixo nível foi utilizado C. Assim, foi possível utilizar a DPI-C (*Direct Programing Interface - C*) que realiza a comunicação entre C e *SystemVerilog*, e é uma ferramente desta linguagem. Para a comunicação entre Python e C foi utilizada a API (*Application Programming Interface*) de Python para C, juntamente com a API da biblioteca *Numpy* de Python para C.

Figura 2 – Fluxo do transição de dados

Assim, esse tópico irá tratar das funções que possibilitaram essa comunicação entre *SystemVerilog* e uma linguagem de alto nível, através de um código exemplo, que pode ser encontrado no Anexo 8.1.2.

Como pode ser observado no Anexo 8.1.1, pode-se enviar qualquer tipo de dados de System Verilog para C. A maioria desses tipos podem ser enviados através de uma struct, e os tipos que não são passíveis de envio neste molde, utilizam funções próprias existentes na biblioteca da DPI (como o caso de um vetor dinâmico). Em suma, em System Verilog, torna-se simples o uso de uma linguagem "estrangeira", sem o uso de nenhuma função especial, com exceção do import.

A parte que deve-se ter uma maior atenção é o código que encontra-se em C. Nesse, estão contidas algumas funções necessárias para traduzir os tipos de dados de *SystemVerilog* para C, e as funções da API-C de Python.

As funções da API-C de Python possuem uma complexidade maior quando comparadas com as funções da DPI-C de *SystemVerilog*. Visando uma maior praticidade na explanação das funções da API-C, as funções que foram utilizadas serão explicadas sucin-

tamente através de tópicos, e sua demonstração de uso estará no Anexo 8.1.2 (IEEE..., )(FOUNDATION, 2018).

- **Py\_Initialize**(): Função que irá inicializar o interpretador de Python. Caso algum interpretador já tiver sido inicializado, ao chamar esta função pela segunda vez, não ocorrerá nada;

- **PyObject**: É um tipo que contém todas as informações necessárias para que o C trate um ponteiro de um ponteiro de um objeto da biblioteca como um objeto de Python. É o tipo básico de todos os objetos da API.

- PyObject\_CallOject(PyOject \*obj, NULL): Chama um objeto. O objeto que puder ser chamado, chamará, consequentemente, seu construtor;

- Py\_BuildValue(const char \*format, value): De forma geral, essa função serve para criar um objeto PyObject com um valor de um tipo de dado conhecido (int, float, string, etc);

- PyObject\_CallMethodObjArgs(PyObject \*obj, PyObject \*method, PyObject \*arg1, PyObject \*arg2, NULL): Chama um método de um objeto previamente inicializado e com a referência em *obj* e seus argumentos;

- PyTuple\_GetItem(PyObject \*tuple\_obj, int pos): Retorna o elemento na posição pos da tupla tuple\_obj. O retorno se dá através de um PyObject;

- PyList\_New(int/Py\_ssize\_t dim): Retorna uma nova lista em caso de sucesso. Esta lista deverá ser armazenada em um ponteiro do tipo PyObject;

- PyList\_SetItem(PyObject \*list, Py\_ssize\_t index, PyObject \*item): Coloca o valor que está em *item* dentro de *list* na posição *index*;

- PyTuple\_Pack(Py\_ssize\_t n, PyObject \*item1, PyObject \*item2, ...): Retorna uma nova tupla de tamanho n, inicializada com item1, item2, .... O retorno deve ser armazenado dentro de um PyObject.

Foram explicadas algumas funções utilizadas para a confecção dos wrappers. Caso o leitor deseje adquirir um conhecimento mais profundo sobre o assunto, deve consultar a documentação de referência externa. Um código exemplo encontra-se em Anexo 8.1.3 e faz parte da comunicação com o System Verilog, juntamente com o código em Python, demonstrando assim, a conexão completa dos wrappers.

## 4 Ambiente de verificação

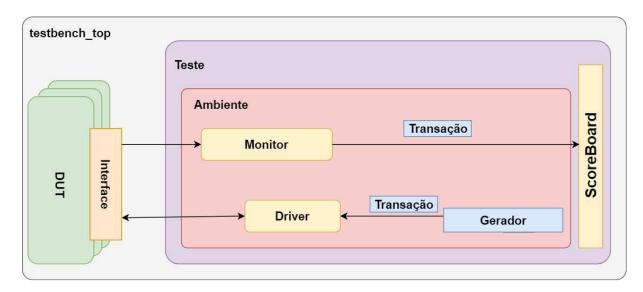

Figura 3 – Exemplo de uma topologia de testbench

O ambiente de verificação possui uma estrutura padrão que visa manter o dispositivo sobre teste DTU (*Device Under Test*) sobre constante monitoramento. De forma geral, pode-se dividir nos seguintes componentes: *driver*, monitor, interface, transação, ambiente, gerador, *checker/scoreboard*, teste e topo. É importante destacar que alguns desses componentes encontram-se contidos dentro de outros, como é o caso do *driver* e monitor que estão contidos dentro do ambiente.

Cada um dos componentes possui uma função específica. O driver tem como função receber os estímulos (transação) advindas de um gerador de dados e atribuir tais valores de entradas para o DUT e para o modelo de referência; o monitor é responsável por monitorar os sinais de saída de ambos, DUT e modelo de referência, através da interface para que assim seja possível obter uma comparação entre eles. A referida comparação é feita pelo componente chamado de checker, no qual basicamente deverá pegar as saídas e compará-las, incrementando um contador de erro ou emitindo um alerta quando uma discrepância entre os sinais comparados existir ou algum sinal adquirir um valor ilegal. A transação define a atividade no nível de pino, ou seja, se comporta como um pacote de dados para que o driver tenha as informações necessárias para realizar sua atividade, também podendo ser utilizado para armazenar valores de saída e transacioná-los para o monitor.

A transação recebe os dados que serão utilizados no *driver*, advindo de outro componente, o gerador. Este componente tem a função de produzir estímulos, partindo de princípios que tornem esses dados válidos e de maneiras pseudoaleatórias.

Os componentes anteriormente mencionados podem ser agrupados como agente (agent), ambiente (environment) e teste. O grupo/componente agente é composto por componentes menores que são específicos a uma interface ou a um protocolo, no caso: gerador, driver e monitor. Já o ambiente, conterá os componentes de alto nível, como os agentes e o scoreboard. O teste, que também pode ser chamado de program test, é responsável por configurar o testbench, iniciar os processos de construtores dos componentes do testbench e iniciar os estímulos. O último componente é o que conecta todos os outros, testbench top, ou topo do testbench. Esse é o o arquivo mais externo, que conecta o DUT ao testbench, consistindo em instâncias do DUT, test e interface, na qual a instância da interface conecta o DUT ao testbench.

Todos esses componentes, com exceção do teste e do topo do testbench, são implementados como classes, comportando-se, assim, como parte de alto nível do testbench. O teste é construído usando um tipo de bloco chamado program, o qual é suportado pela linguagem SystemVerilog, como já foi mencionado anteriormente. O propósito segundo o manual de referência da linguagem (IEEE..., ): é prover um ponto de entrada para execução dos testbenchs e criar um escopo que encapsule todo os dados, tasks, e funções do program.

O topo do *testbench* é implementado com um nível mais baixo de abstração, utilizando o module, que neste caso é utilizado para ter a possibilidade de se conectar com os blocos ou componentes de verificação, com os blocos de design, ou DUT.

## 5 Testbench modelo

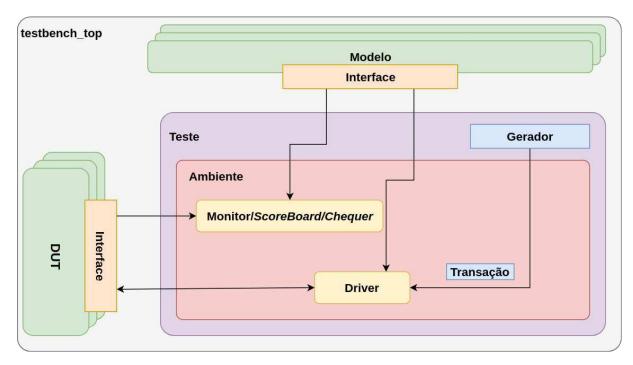

O *TestBench* gerado segue um modelo que é de acesso público em (SYSTEMVE-RILOG..., 2016), o qual foi escolhido por utilizar-se de uma ambiente completo com praticamente todos os componentes de um *testbench*.

Figura 4 – Topologia de testbench utilizada no gerador

Este ambiente possui uma organização que torna o arquivo testbench.sv(vide 8.2.1) o arquivo de topo. Este arquivo irá conectar o DUT ao ambiente de verificação, utilizando-se, para tanto, de um interface virtual, visando a possibilidade de manipulação dos valores dos sinais sem que estes sejam alterados instantaneamente no DUT.

Neste arquivo, por ser o arquivo de topo, irá conter a geração do *clock*. No exemplo encontrado, ele gera um *reset* que será utilizado apenas no início da simulação. Visando testes que exercitem mais o DUT, o ambiente gerado terá seus *reset* ativados por controle do teste, assim podendo ser ativado quando o teste desejar.

Uma outra adaptação em relação ao arquivo é que, no exemplo, não existe um modelo de referência propriamente dito. Assim, para aumentar as possibilidades de testes quanto à capacidade do ambiente gerado e poder ter um leque maior de modelos suportados, ou seja, o modelo não se limitar a um modelo que seja implementado em System Verilog e ser possível comparar algoritmos complexos que são possíveis de ser implementados em linguagens de alto nível, criou-se wrappers. Estes são capazes de realizar a comunicação de um modelo de referência em Python (linguagem de alto nível) com o

ambiente de verificação. Com os *wrappers*, o modelo de referência passa a ser um modelo instanciado no topo, que terá sua própria interface.

Assim, neste arquivo são instanciados todos os DUT e todos os modelos de referências necessários para realizar os testes, juntamente com suas respectivas interfaces.

A instanciação das interfaces acontecem no testbench.sv, mas sua declaração acontece dentro do arquivo interface.sv. A declaração da interface do bloco é feita da maneira ANSI, recebendo os parâmetros do bloco e os sinais de reset e do clock como entradas para a interface. Seguindo o padrão, a interface possui sua declaração de parâmetros, seus dois sinais e, internamente, a declaração dos sinais ao bloco que ela corresponde. Atentando ao detalhe que os sinais aqui foram declarados como wire, visando a possibilidade do uso de inout, pois julgou-se melhor a implementação de um único clocking block em que este tem os sinais declarados de maneira inout e sem a declaração de um modport. Fazendo assim, com que um único bloco comporte-se como se tivesse a utilidade para o driver e para o monitor, deixando, assim, a necessidade da instanciação de dois modport, um para cada componente.

Dessa forma, a estrutura final da interface, que pode ser vista no Código 8.2.2, ficou apenas com a declaração dos sinais e de um *clocking block*.

A próxima instanciação no arquivo testbench.sv é a instanciação do teste. O arquivo de declaração de teste não pode ser gerado completamente, pois, em razão de sua característica peculiar para cada bloco, torna-se difícil generaliza-lo. Assim, pensouse em montar uma estrutura básica, só para conter objetos e declarações que tornam-se obrigatórios devido ao resto dos componentes do testbench.

Com isso, o *stub*(vide 8.2.3) do teste acabou sendo composto por um bloco de initial, no qual tem-se a instanciação do ambiente (*environment*) sendo passado para o seu construtor todas as interfaces necessárias e um bloco de fork, no qual mantém-se a repetição do ambiente, até que este detecte a condição para terminar.

O construtor do ambiente contém a instanciação de outros componentes, como o monitor e o drive. O construtor do drive irá receber a interface do DUT (que servirá como meio de propagação dos valores do drive para as outras interfaces) e o monitor receberá as interfaces virtuais do DUT e o do modelo. Para manter o sincronismo entre o teste o ambiente, utiliza-se uma variável declarada como mailbox, que é instanciada no teste e passada através do construtor do ambiente para o drive, assim, quando o teste colocar uma transação ele só irá colocar a próxima depois que o drive tirar o item já existente. Além do seu construtor recebendo parâmetros, tem-se a declaração de uma task chamada de run para ser invocada pelo teste e iniciar os processos do monitor e do drive e o comando para finalizar a simulação, \$finish. Os processos iniciados por essa task estão dentro de um fork-join\_any, juntamente com o processo de outra task, responsável por checar se

a condição de término do teste foi atingida, no caso de as quantidades de ciclos desejada terem sido atingida no monitor.

Para dar suporte a essas necessidades, no ambiente também são declarados alguns tipos através do uso de typedef(vide 8.2.4), como os tipos das interfaces virtuais dos blocos para que assim seja possível o construtor receber tais informações.

A declaração do *driver* é feita no arquivo nome\_block\_drive.sv(vide 8.2.5). O seu construtor recebe a interface do DUT e o mailbox, assim como a quantidade de ciclos que o drive terá que operar. A classe drive foi implementada com o construtor e uma *task* drive, que tem com principal funcionalidade retirar o item do mailbox e realizar a atribuição dos sinais da interface do DUT, tornando-a uma classe simples.

A classe monitor nesse modelo terá duas funções extras (vide 8.2.6): checar as saídas e contabilizar os erros. Ainda, tem como entradas do seu construtor as interfaces virtuais do modelo de referência e do DUT. A classe possui um único método monitor que irá acessar os dados advindos das interfaces virtuais e compará-los, e, caso estes dados divirjam, deverá incrementar um valor que servirá como flag para detectar se ocorreu algum erro entre o DUT e modelo.

Todos os dados são armazenados em um objeto de uma classe chamada transaction ( em tradução livre: transação), a qual contem propriedades variáveis equivalentes aos sinais que o drive é responsável por atribuir valores, pode ser observado seu modelo no Anexo 8.2.7.

O seu construtor não receberá nenhum parâmetro, mas a classe terá método de *init*, para inicializar valores internos e randomize\_static, para randomizar variáveis/sinais. É importante salientar que a parte de constraints deve ser implementada pelo usuário do código, ou seja, não será gerado com o gerador.

## 6 Gerador de *TestBench*

Visando a praticidade e eficiência no decorrer de um projeto de um IP, no qual se requer uma verificação a cada mudança, seja ela de interface, na quantidade de bits internos para algoritmos de convergência ou em sua arquitetura, pensou-se na implementação de gerador para o ambiente de verificação, fazendo com que o engenheiro tenha seu tempo melhor aproveitado.

Para que a utilização do gerador implementado seja possível, utiliza-se uma planilha na qual deve conter informações cruciais quanto aos sinais do bloco que se deseja verificar, como: nome do bloco; nome dos sinais; quantidade de bits de cada sinal; a quantidade daqueles bits que serão inteiros e se a porta terá bit para a representação do sinal ou não, para o uso em conjunto com um modelo de referência em Python. Esta última informação é necessária devido ao fato de que o modelo em Python deverá operar em floating point, tornando necessário que o valor no sinal seja convertido de maneira correta através de aritmética de ponto fixo.

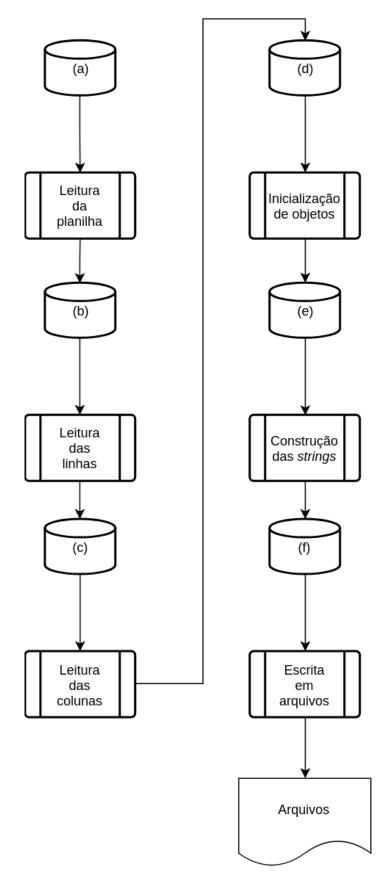

Assim, o funcionamento do algoritmo irá percorrer a planilha e armazenar as informações em variáveis das classes do gerador. Tendo assim, fluxo de dados e resultados como mostrados na Figura 5.

O fluxograma possui o seguintes elementos:

- a) Arquivo em formato de planilha onde estão contidas as informações dos blocos e suas interfaces;

- b) Conjuntos de objetos que contém as informações contidas nas abas do arquivo fonte;

- c) Conjunto de objetos que contém as informações contidas nas linhas de cada aba do arquivo fonte;

- d) Conjunto de objetos que contém as informações contidas em cada células das linhas que foram armazenadas;

- e) Objetos inicializados com as informações completas adquiridas da planilha, como, por exemplo, nome do bloco, tamanho do sinal, direção do sinal etc;

- f) Strings construídas partindo da análise dos dados obtidos no processo anterior;

Cada classe possui métodos que servem para armazenar e manipular as informações para que seja possível a impressão dos arquivos de *testbench*. Seguindo o fluxo de dados no gerador um objeto deve ser criado, inicialmente, da classe SpreadsheetReader, a

Figura5 – Fluxograma dos dados no gerador

qual possui os métodos e os atributos mostrados na Tabela 1. O construtor desta classe recebe o caminho para onde se encontra a planilha que deverá ser utilizada para obter as informações necessárias.

| $\operatorname{SpreadsheetReader}$ |                           |  |

|------------------------------------|---------------------------|--|

| Atributos                          | Métodos                   |  |

| mPath                              | SpreadsheetReader(string) |  |

| mInputStream                       | parseWorkbook(int)        |  |

| mWorkbook                          | ${ m getBlocks}$          |  |

| maBlock                            |                           |  |

Tabela 1 – Atributos e métodos da classe SpreadsheetReader

A classe é composta por um atributo que armazenará o caminho para a planilha juntamente com o nome da planilha em um objeto do tipo InputStream, que faz parte de um pacote de Java para entrada e saída de dados. Assim, esse objeto receberá os bytes referentes ao arquivo da planilha no sistema. A classe ainda contém um atributo do tipo XSSFWorkbook, que possui métodos para manipular a planilha, sendo, este tipo de objeto, próprio de bibliotecas de Java. O último atributo é de um tipo de outra classe implementada para o gerador, o qual também é ArrayList. Este atributo referenciará a aba da planilha (útil para caso em uma única planilha encontram-se vários blocos declarados em diferentes abas), em que cada elemento do vetor é uma aba da planilha.

O método da classe parseWorkbook visa à atribuição dos valores na planilha para objetos, mais especificamente do tipo ParsedBlock, ou seja, ele "adiciona" as abas das planilhas nas posições do vetor maBlock. A classe ainda tem um outro método, getBlocks, que tem como funcionalidade o retorno do vetor, que possui as informações contidas nas abas em cada elemento.

Para adicionar os elementos ao vetor é necessário chamar o construtor da classe ParsedBlock, que possui atributos e métodos mostrados na Tabela 2. O construtor recebe um objeto do tipo XSSFSheet e irá analisar as linhas de cada aba e adicionar em um vetor do tipo ParsedSignal, que servirá como objeto, contendo informações das linhas nas quais devem estar os sinais e seus dados. Para que seja possível ter esse acesso, se utiliza o tipo XSSFRow, que faz parte da biblioteca que trata a interação de Java com arquivos .xlsx. Com isso, o construtor da classe ParsedSignal receberá um objeto que conterá informações de uma das linhas da planilha e acessará as informações contidas nas células das linhas armazenando o conteúdo em seus atributos.

A classe ParsedBlock possui mais um método, toBlock, que converterá as informações do objeto ParsedBlock em Block. O toBlock chama um dos métodos da classe ParsedSignal, que tem como funcionalidade converter os sinais, no caso, os elementos que estão dentro do atributo maSignal, para um objeto da classe Signal, que será utilizado no construtor da classe Block sendo este, o retorno do método.

| ${f ParsedBlock}$ |                        |  |

|-------------------|------------------------|--|

| Atributos         | Métodos                |  |

| mName             | ParsedBlock(XSSFSheet) |  |

| maSignal          | parseWorkbook(int)     |  |

| maIgnore          | toBlock                |  |

Tabela 2 – Atributos e métodos da classe ParsedBlock

| ${f Parsed Signal}$ |                                |  |

|---------------------|--------------------------------|--|

| Atributos           | Métodos                        |  |

| mIo                 | ParsedSignal(XSSFRow)          |  |

| mName               | $\operatorname{getConstants}$  |  |

| mNbw                | $\operatorname{getSignalType}$ |  |

| mSigned             | $\operatorname{getDirection}$  |  |

| mType               | $\operatorname{getRole}$       |  |

| mNs                 | $\operatorname{getSigned}$     |  |

| mObs                | parseOptions                   |  |

| mDefault            | to Signal                      |  |

Tabela 3 – Atributos e métodos da classe ParsedSignal

ParsedSignal, uma outra classe, possui atributos de informações que estão contidas em cada linha da planilha, na qual cada atributo será inicializado no construtor através de funções de bibliotecas de Java, que servem para manipular células de planilhas e obter os valores de cada célula.

Os métodos da classe acima referida, têm como objetivo criar objetos para que seja possível a construção dos dados de retorno da função toSignal. Assim, como mostrado na Tabela 3, a classe possui os seguintes métodos que serão detalhados a seguir.

- **getConstants**: é utilizado para criar, inicializar e retornar um vetor de objetos da classe **SignalTypeConstant**, que armazena as informações sobre o tamanho dos sinais e constata se há bits dedicados à parte inteira ou não;

- getSignalType: é utilizado para constatar de que tipo será o sinal, se terá ou não partes packed e se terá que utilizar lógica de fixed point na sua comunicação com o modelo. Utiliza-se do método getConstants para conseguir construir o seu objeto de retorno;

- **getDirection**: retornará através de um *enum* se o sinal é de entrada ou saída do bloco;

- **getRole**: identificará a natureza do sinal, se ele é de *reset*, *clock* ou dados/controle do bloco;

- getSigned: utilizará da informação existente na planilha sobre como o sinal irá se comportar sobre o seu sinal, ou seja, se ele possuirá ou não bit para representatividade do sinal;

- parseOptions: servirá para obter informações de um campo onde se pode colocar peculiaridades do sinal. Este campo varia mais de bloco para bloco.

Todos os métodos detalhados são utilizados no método toSignal, que retornará um objeto do tipo Signal. Para tanto, se faz o uso do seu construtor, este, que por sua vez, recebe o retorno de quase todos os métodos da classe e também instancia um objeto do tipo SignalTypeHub e do tipo Name, ambos necessários, junto com os métodos, para a inicialização do objeto do tipo Signal.

Assim, pode-se perceber que as principais classes do gerador são as classes Block, Signal, SignalType, SignalTypeConstant. Essas classes armazenam as informações referentes aos sinais de cada bloco da planilha, fazendo com que o acesso aos seus atributos através de métodos seja necessário e frequente.

A classe SignalTypeConstant possui os métodos e atributos mostrados na Tabela 4, os quais irão montar constantes para serem utilizadas nos arquivos como #define, para os arquivos de wrappers, e parameter para arquivos em SystemVerilog. O construtor da classe tem como parâmetros o nome do sinal, a quantidade de bits e se a quantidade de bits representa o sinal completo ou só a parte inteira. Com isso, o método getConstantName consegue retornar uma string com o nome da constante a ser definida.

| SignalTypeConstant |                                                         |  |

|--------------------|---------------------------------------------------------|--|

| Atributos          | Métodos                                                 |  |

| mName              | SignalTypeConstant(String, int, EnumSignalTypeConstant) |  |

| mValue             | $\operatorname{getConstantName}$                        |  |

| mType              | $\operatorname{setConstantType}$                        |  |

|                    | ${\rm find By Constant Type}$                           |  |

Tabela 4 – Atributos e métodos da classe SignalTypeConstant

SignalType é a classe que utiliza diretamente de objetos originados da classe SignalTypeConstant. Seus atributos possuem características que armazenam as *strings* referentes às constantes utilizadas no código, no caso também envolvendo informação. Caso se utilize de SystemC como modelo de referência, também pode-se adicionar as informações referentes ao tipo de sinal: sc\_bv, sc\_fixed\_fast, etc. Entre seus atributos há um vetor do tipo SignalTypeConstant, no qual serão armazenadas as informações de quantidade de bit de cada sinal juntamente com o nome da sua respectiva constante.

O seu construtor recebe atributos sobre os tipos do sinal em SystemVerilog, com possibilidade de receber os tipos de SystemC, um vetor de inteiros que conterá as dimensões para o uso em SystemVerilog, um vetor que deverá estar em sincronismo com o vetor

anterior que determina se a dimensão do sinal será packed/unpacked e, por fim, um vetor com informações para a construção das constantes.

| ${f Signal Type}$ |                                                     |  |

|-------------------|-----------------------------------------------------|--|

| Atributos         | Métodos                                             |  |

|                   | SignalType(                                         |  |

|                   | String,                                             |  |

|                   | EnumScBaseType,                                     |  |

| mCustomName       | ArrayList <integer>,</integer>                      |  |

|                   | ArrayList <enumpackedness>,</enumpackedness>        |  |

|                   | ArrayList <signaltypeconstant></signaltypeconstant> |  |

|                   | )                                                   |  |

| mSvBaseType       | getConstantByType(EnumSignalTypeConstant)           |  |

| mScBaseType       | getConstantExist(EnumSignalTypeConstant)            |  |

| mScTemplate       | getParameterName(String)                            |  |

| mScFlatTemplate   | ${\it getDimensionDeclaration}$                     |  |

| maDimension       | ${ m get}{ m TemplateDeclaration}$                  |  |

| maSvPackedness    |                                                     |  |

| maConstant        |                                                     |  |

Tabela 5 – Atributos e métodos da classe SignalType

A classe possui os seguintes métodos(vide Tabela 5):

- **getConstantByType**: tem como objetivo filtrar as contantes pelo tipo desejado (tamanho do sinal em *bit*, tamanho da parte inteira em *bits* do sinal, etc);

- getConstantExist: retorna se um determinado tipo de constante foi declarado, tornando assim, seu valor de retorno True/False;

- getTemplateDeclaration: é utilizado para compor as declarações de typedef;

- **getDimensionDeclaration**: é utilizado na construção da declaração dos sinais em System Verilog, para retornar de acordo com os valores das partes packed e unpacked.

A próxima classe é a Signal, na qual seus atributos formam um conjunto de informações quanto ao sinal (vide Tabela 6). Os atributos mName e mDefault são declarados como *strings*, e mhOption é um HashMap. Todos esses tipos já existem previamente em Java, tornando, assim, o conjunto de atributos que não tiveram seus tipos criados. Esse último atributo tem como objetivo conter informações sobre a última coluna, a qual foi pensada para opções que venham a se fazer necessárias sobre possíveis peculiaridades do bloco. Para o uso, é necessário um padrão que se tornará uma chave, e esta pode ou não conter valor, fazendo com que seja bastante útil para seu uso.

Os outros atributos são de tipos que foram implementados para auxiliar o armazenamento de informações advindas da planilha, como: mPortDirection, mRole e mSigned,

| Signal         |                        |  |

|----------------|------------------------|--|

| Atributos      | Métodos                |  |

|                | Signal(                |  |

|                | Name,                  |  |

|                | EnumSignalDirection,   |  |

| mName          | EnumRole,              |  |

|                | EnumSignedSignal,      |  |

|                | HashMap                |  |

|                |                        |  |

| mDefault       | getDeclaration         |  |

| mPortDirection | get Signal Declaration |  |

| mRole          | getStrBaseType         |  |

| mSigned        | getTypedefDeclaration  |  |

| mhOption       |                        |  |

Tabela 6 – Atributos e métodos da classe Signal

que são declarados como um tipo específico de enum, que representam a direção do sinal, seu papel no bloco (se o sinal é de entrada ou saída, clock ou reset) e se o sinal possui ou não bit de sinal, respectivamente. As informações que as classes SignalType podem conter (ou armazenar) são acessadas através do atributo mType, que, assim como os outros atributos, é inicializado no construtor da classe.

Os atributos desta classe possuem um foco para retornar as declarações dos sinais. Assim, as declarações necessárias para o testbench e seus componentes foram implementadas como métodos desta classe. O método getDeclaration retornará a declaração dos sinais em System Verilog, utilizando das informações de dimensões e packed/unpacked contidas em seu tipo no atributo da classe. Supondo uma interação com System C, os métodos getTypedefDeclaration e getStrBaseType retornam strings para que seja possível a declaração dos tipos que serão utilizados nos wrappers para System C.

Dessa forma, com todos os elementos da variável aBlock inicializados devidamente, temos no programa todas as informações úteis contidas na planilha sobre todos os blocos que estejam devidamente descritos. Partindo deste ponto, pode-se utilizar os métodos e atributos contidos no tipo de aBlock para que os arquivos comecem a serem gerados.

O método do objeto aBlock invocado é createFiles, que irá chamar o método setupFiles, da própria classe. Este, por sua vez, constrói todos os arquivos através da inicialização dos atributos que referem-se aos arquivos em si. O primeiro método chamado irá invocar um método em particular de cada atributo, write, que tem como função receber uma string, a qual irá conter todo o conteúdo do arquivo. Para que esta última ação seja possível, foram implementadas classes para cada grande componente, como: driver, monitor, wrappers etc. Assim, Block possui atributos referentes a todos os componentes, e suas classes possuem métodos que retornam a string, que serão escritos nos arquivos.

Alguns métodos foram implementados para que os referidos dados fossem gerados antes que a função de escrita no arquivo fosse utilizada. Por padrão eles seguem a característica: generate<nome do arquivo>. Dentro desse métodos são construídos e inicializados os atributos correspondentes aos componentes como: mEnvironment, mPyWrapper, etc.

As classes dos componentes possuem métodos que irão utilizar das informações contidas nos seus atributos, que são passadas através do seu construtor que, por sua vez, recebe um objeto do tipo Block. Este objeto conterá todas as informações referentes a um bloco que estava na planilha. Com essas informações é possível gerar a *string* que será impressa nos arquivos, pois se optou por seguir um padrão predefinido como *testbench* e, assim, com as informações que foram adquiridas da planilha é possível determinar como será o código final.

# 7 Considerações Finais