### Universidade Federal de Campina Grande Centro de Engenharia Elétrica e Informática Departamento de Engenharia Elétrica

RODRIGO PEREIRA DE LACERDA

# DESCRIÇÃO DO PROJETO E DOS PROCEDIMENTOS DE USO DE UMA BANCADA PARA TESTES DE CONVERSORES ESTÁTICOS CONTROLADOS E NÃO-CONTROLADOS

Campina Grande, Paraíba Março de 2017

#### RODRIGO PEREIRA DE LACERDA

## DESCRIÇÃO DO PROJETO E DOS PROCEDIMENTOS DE USO DE UMA BANCADA PARA TESTES DE CONVERSORES ESTÁTICOS CONTROLADOS E NÃO-CONTROLADOS

Relatório de Estágio Supervisionado apresentado à Coordenação do Curso de Graduação em Engenharia Elétrica da Universidade Federal de Campina Grande como parte dos requisitos necessários para a obtenção do grau de Bacharel em Engenharia Elétrica.

Área de Concentração: Eletrônica de Potência

Orientador: Prof. Dr. Cursino Brandão Jacobina

Campina Grande, Paraíba Março de 2017

#### RODRIGO PEREIRA DE LACERDA

#### DESCRIÇÃO DO PROJETO E DOS PROCEDIMENTOS DE USO DE UMA BANCADA PARA TESTES DE CONVERSORES ESTÁTICOS CONTROLADOS E NÃO-CONTROLADOS

Relatório de Estágio Supervisionado apresentado à Coordenação do Curso de Graduação em Engenharia Elétrica da Universidade Federal de Campina Grande como parte dos requisitos necessários para a obtenção do grau de Bacharel em Engenharia Elétrica.

| Aprovado em | / | ′/ |  |

|-------------|---|----|--|

|             |   |    |  |

#### Professor Avaliador

Universidade Federal de Campina Grande Avaliador

Prof. Dr. Cursino Brandão Jacobina Universidade Federal de Campina Grande Orientador

> Campina Grande, Paraíba Março de 2017

Dedico este trabalho a minha família, que sempre acreditou nos meus sonhos.

#### Agradecimentos

A Jeová Deus, primeiramente, por me conceder a força e a sabedoria que foram fundamentais para realização desta atividade, assim como pelas oportunidades que me foram postas na vida.

Aos meus pais, Roberto e Maria, a minhas irmãs, Ranielly e Noêmia, e a minha avó, Livina, pelo apoio incondicional para que eu sempre pudesse continuar estudando e jamais desistisse dos meus objetivos.

Aos meus amigos de graduação, José Fábio, Filipe Vieira, Ruan Gomes, Carlos Juacyr, Matheus Lucena e outros pelo companheirismo, incentivo e todo apoio durante os anos da graduação.

Aos meus grandes amigos Júnior Souza e Matheus Pedrosa, pelos momentos de descontração e por sempre me escutarem e me apoiarem em todas as horas.

Ao meus colegas do LEIAM Ítalo Roger, Bruno Emmanuel, Nayara Brandão e outros pelo apoio, conselhos e sugestões que também foram essenciais para a realização deste trabalho.

Ao Professor Doutor Cursino Brandão Jacobina, pelo privilégio de tê-lo como orientador, e pela paciência e disposição em oferecer a devida orientação aos estudos realizados.

A todos aqueles que contribuíram de forma direta ou indiretamente para a concretização desta atividade.

#### Resumo

Neste trabalho são apresentadas as atividades desenvolvidas durante o Estágio Supervisionado no Laboratório de Eletrônica Industrial e Acionamento de Máquinas (LEIAM) da Universidade Federal de Campina Grande (UFCG), que incluíram a análise do sistema e do funcionamento de uma das bancadas do Laboratório, a descrição das suas principais características, a realização de experimentos e testes, e a produção de um manual didático que poderá auxiliar na compreensão das principais funcionalidades da bancada, na identificação de erros e na construção de novas bancadas. Esse manual é apresentado na forma deste relatório que ficará disponível aos alunos que utilizarão a bancada.

Palavras-chave: Conversores Estáticos. Bancada de Testes. Diagramas. Testes Experimentais.

#### Lista de ilustrações

| Figura 2.4 – Layout da bancada. (a) Vista lateral esquerda da estrutura. (b) Vista lateral direita da estrutura.  Figura 2.5 – Diagramas elétricos. (a) Circuito monofásico. (b) Diagrama de comando. (c) Diagrama de força                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figura 2.3 – Layout da bancada. (a) Vista frontal da estrutura. (b) Vista traseira da estrutura.  Figura 2.4 – Layout da bancada. (a) Vista lateral esquerda da estrutura. (b) Vista lateral direita da estrutura.  Figura 2.5 – Diagramas elétricos. (a) Circuito monofásico. (b) Diagrama de comando. (c) Diagrama de força  Figura 2.6 – Componentes do circuito de proteção da bancada |

| da estrutura.  Figura 2.4 – Layout da bancada. (a) Vista lateral esquerda da estrutura. (b) Vista lateral direita da estrutura.  Figura 2.5 – Diagramas elétricos. (a) Circuito monofásico. (b) Diagrama de comando. (c) Diagrama de força                                                                                                                                                 |

| Figura 2.4 – Layout da bancada. (a) Vista lateral esquerda da estrutura. (b) Vista lateral direita da estrutura.  Figura 2.5 – Diagramas elétricos. (a) Circuito monofásico. (b) Diagrama de comando. (c) Diagrama de força                                                                                                                                                                |

| lateral direita da estrutura                                                                                                                                                                                                                                                                                                                                                               |

| Figura 2.5 – Diagramas elétricos. (a) Circuito monofásico. (b) Diagrama de comando. (c) Diagrama de força                                                                                                                                                                                                                                                                                  |

| (c) Diagrama de força                                                                                                                                                                                                                                                                                                                                                                      |

| Figura 2.6 – Componentes do circuito de proteção da bancada                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                            |

| D: 07 D : 1 D : ~                                                                                                                                                                                                                                                                                                                                                                          |

| Figura 2.7 – Botoeiras de Energização                                                                                                                                                                                                                                                                                                                                                      |

| Figura 2.8 – Terminais de acesso a tensão do varivolt                                                                                                                                                                                                                                                                                                                                      |

| Figura 2.9 – Conexões do Bloco B                                                                                                                                                                                                                                                                                                                                                           |

| Figura 2.10–Circuito correspondente a cada módulo                                                                                                                                                                                                                                                                                                                                          |

| Figura 2.11–IGBTs e Diodos                                                                                                                                                                                                                                                                                                                                                                 |

| Figura 2.12–Driver para acionamento das chaves IGBTs                                                                                                                                                                                                                                                                                                                                       |

| Figura 2.13–Snubber                                                                                                                                                                                                                                                                                                                                                                        |

| Figura 2.14–Vantagem de se usar <i>snubbers</i>                                                                                                                                                                                                                                                                                                                                            |

| Figura 2.15–Sensor de tensão LV-20P                                                                                                                                                                                                                                                                                                                                                        |

| Figura 2.16–Sensor de Corrente LTS15-NP                                                                                                                                                                                                                                                                                                                                                    |

| Figura 2.17–Regulador de tensão LM1086                                                                                                                                                                                                                                                                                                                                                     |

| Figura 2.18–Foto do circuito de alimentação dos sensores e $drivers$                                                                                                                                                                                                                                                                                                                       |

| Figura 2.19–Alimentação de sensores e $drivers$                                                                                                                                                                                                                                                                                                                                            |

| Figura 2.20–Conexões no Bloco D                                                                                                                                                                                                                                                                                                                                                            |

| Figura 2.21–Características da chave analógica TS5A3159                                                                                                                                                                                                                                                                                                                                    |

| Figura 2.22–CI's SN74HC541N e SN74HC540N                                                                                                                                                                                                                                                                                                                                                   |

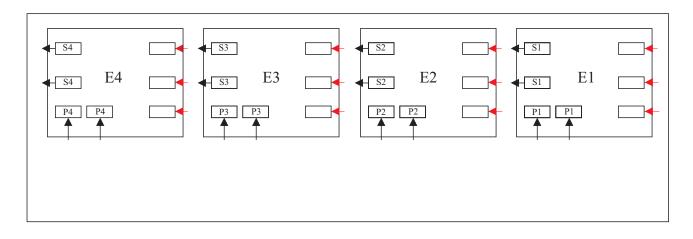

| Figura 2.23–Conexões no Bloco E. (a) Vista traseira. (b) Vista frontal                                                                                                                                                                                                                                                                                                                     |

| Figura 2.24–Kit eZdsp TMS 320F28335                                                                                                                                                                                                                                                                                                                                                        |

| Figura 2.25–Ligações do sensor de corrente LTS15-NP                                                                                                                                                                                                                                                                                                                                        |

| Figura 2.26–Ligações do sensor de tensão LV-20P                                                                                                                                                                                                                                                                                                                                            |

| Figura 2.27–Alimentação dos sensores                                                                                                                                                                                                                                                                                                                                                       |

| Figura 2.28–Placas S1, S2, S3 e S4                                                                                                                                                                                                                                                                                                                                                         |

| Figura 2.29–Junção dos sinais diferenciais dos sensores                                                                                                                                                                                                                                                                                                                                    |

| Figura 2.30–Conexões dos sensores ao DSP                                                                                                                                                                                                                                                                                                                                                   |

| Figura 2.31–Conexões dos <i>drivers</i> ao DSP                                                                                                                                                                                                                                                                                                                                             |

| Figura 2.32–Alimentação                                                                                                                                                                                                                                                                                                                                                                    |

| Figura 2.33–Sinais PWM                                                           | <u>.</u> 1 |

|----------------------------------------------------------------------------------|------------|

| Figura 2.34–Sinais PWM e seus complementares                                     | 2          |

| Figura 2.35–Sinais PWM diferenciais                                              | :3         |

| Figura 2.36–Interface - Sinais PWM                                               | 4          |

| Figura 2.37–Sinais PWM para os drivers                                           | :5         |

| Figura 2.38–Sinais dos <i>drivers</i> para os IGBTs                              | 6          |

| Figura 3.1 – Teste dos $drivers$ e IGBTs                                         | :7         |

| Figura 3.2 – Esquema de ligação da topologia testada                             | :8         |

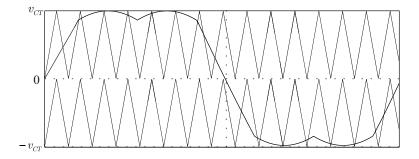

| Figura 3.3 – Portadoras utilizadas na estratégia $Level\text{-}Shifted$ PWM 4    | 8          |

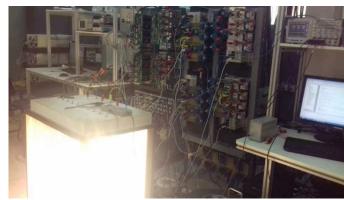

| Figura 3.4 – Montagem                                                            | 9          |

| Figura 3.5 – Resultado Experimental                                              | 9          |

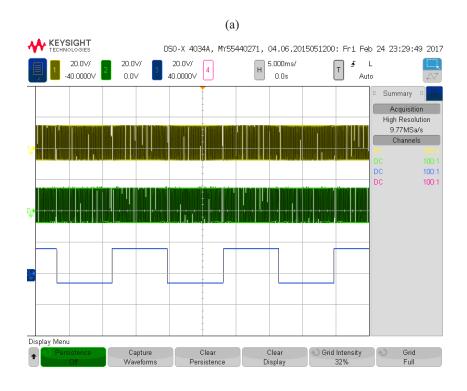

| Figura 3.6 – Sinais PWM enviados aos drivers. (a) Sinal no gate dos IGBTs. (b)   |            |

| Valor médio dos sinais PWM                                                       | 0          |

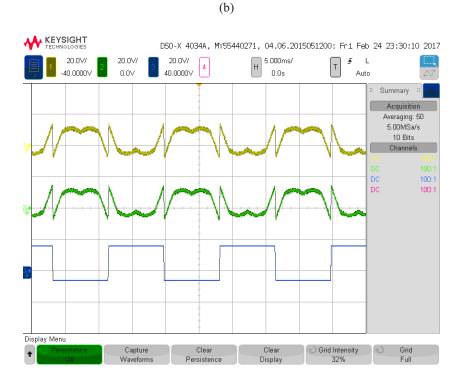

| Figura 3.7 – Resultado obtidos no CCS v3.3. (a) Referências geradas. (b) Leitura |            |

| nos sensores de corrente e tensão                                                | 1          |

#### Lista de abreviaturas e siglas

CA Corrente Alternada (Alternating current)

CC Corrente Contínua

DC Tensão Contínua

IGBT Transistor Bipolar de Porta Isolada (Insulated Gate Bipolar Transistor)

PWM Modulação por Largura de Pulso (Pulse Width Modulation)

DSP Processador Digital de Sinais (Digital Signal Processor)

UTP Par Trançado Não-Blindado (Unshielded Twisted Pair)

#### Lista de símbolos

$v_{CT}$  tensão total do barramento CC.

#### Sumário

| 1   | INTRODUÇÃO                                         | 11 |

|-----|----------------------------------------------------|----|

| 1.1 | Considerações Iniciais                             | 11 |

| 1.2 | Cronograma de Atividades                           | 12 |

| 2   | DESCRIÇÃO DA BANCADA                               | 13 |

| 2.1 | Especificações do Projeto                          | 15 |

| 2.2 | Bloco A: Proteção e Alimentação                    | 17 |

| 2.3 | Bloco B: Módulos - Conversores                     | 20 |

| 2.4 | Bloco C: Alimentação dos sensores e <i>drivers</i> | 26 |

| 2.5 | Bloco D: Sinais dos sensores e sinais PWM drivers  | 27 |

| 2.6 | Bloco E: Roteamento                                | 30 |

| 2.7 | Microprocessador                                   | 31 |

| 2.8 | Diagramas Técnicos                                 | 32 |

| 3   | RESULTADOS EXPERIMENTAIS                           | 47 |

| 4   | CONCLUSÕES                                         | 52 |

|     | REFERÊNCIAS                                        | 53 |

#### 1 Introdução

#### 1.1 Considerações Iniciais

O aumento no uso de energia elétrica em todo o mundo por parte de consumidores residenciais, comerciais e industriais tem feito com que os conversores estáticos ganhem cada vez mais importância, o que tem estimulado o desenvolvimento de novas topologias e o estudo de novas técnicas de controle desses conversores. Diversos tipos de conversores estáticos são estudados, dentre os quais podem ser destacados os conversores CA-CC, CC-CA e CA-CC-CA controlados e não-controlados, com estradas e saídas trifásica e/ou monofásicas, que são aplicados em muitos sistemas de conversão. Para validação desses estudos é muito importante o desenvolvimento de modelos dinâmicos, o desenvolvimento de programas de simulação do sistema e a realização de testes experimentais.

Neste trabalho são apresentadas as atividades desenvolvidas no Estágio Supervisionado realizado no Laboratório de Eletrônica Industrial e Acionamento de Máquinas (LEIAM), que é um dos laboratórios do Departamento de Engenharia Elétrica (DEE) da Universidade Federal de Campina Grande (UFCG) e realiza pesquisas nas áreas de acionamento e controle de máquinas elétricas, qualidade de energia e fontes alternativas. Sendo assim, o projeto e desenvolvimento de novas topologias de conversores estáticos é um dos ramos de pesquisa do Laboratório.

As pesquisas realizadas no LEIAM adotam aspectos importantes que devem ser considerados no projeto um sistema de conversão os quais incluem a realização de pesquisas bibliográficas no tema, elaboração de modelos dinâmicos e de regime permanente, definição de estratégias PWM para o chaveamento dos conversores, desenvolvimento de sistemas de controle, desenvolvimento de programas de simulação e a obtenção de resultados experimentais, que é de imprescindível importância para validar a aplicabilidade das novas topologias propostas. Para tanto, o LEIAM disponibiliza de uma infraestrutura que permite a execução de todas essas atividades, inclusive disponibiliza diversas bancadas experimentais que permitem a realização de testes práticos de diversas topologias de conversores.

A maior parte desses bancadas experimentais foram desenvolvidas por alunos que fazem parte do grupo de pesquisa do Laboratório, seguindo um mesmo padrão no que diz respeito a estrutura, porém cada uma com suas variações e características peculiares de forma a permitir o teste prático de diversas topologias diferentes de conversores estáticos. No entanto, a maior parte dessas bancadas não disponibilizam um manual ou guia didático que auxiliem no seu uso e que descrevam como foram realizadas as ligações elétricas, as

conexões dos cabos e as principais características dos componentes presentes na estrutura, o que poderia facilitar na identificação de erros e falhas durante a realização dos testes experimentais.

Assim, o estágio referido neste documento teve como principal objetivo descrever os procedimentos para uso e as principais características de uma das bancadas de testes do Laboratório e produzir um documento guia que servisse de base para a compreensão das funcionalidades da bancada, de forma a facilitar a introdução de novos alunos nas atividades práticas do Laboratório e auxiliar na identificação de falhas nos experimentos, além de mostrar de forma didática um exemplo prático.

Este relatório é dividido em quatro capítulos. O primeiro apresenta os objetivos a serem alcançados no estágio e o cronograma de atividades. O segundo capítulo apresenta uma descrição da bancada, mostrando suas características estruturais e detalhes técnicos do projeto. O terceiro capítulo apresenta o exemplo de uma topologia testada na bancada. E no capítulo quatro e último é feita uma análise geral do estágio e dos resultados alcançados.

#### 1.2 Cronograma de Atividades

O estágio supervisionado foi realizado no período de 15/01/2017 até 25/02/2017, totalizando seis semanas. O mesmo apresentou uma carga horária de 180 horas, distribuídas em 30 horas semanais (6h/dia). As atividades desenvolvidas durante o estágio incluíram:

- Análise do sistema e do funcionamento da bancada;

- Descrever as principais características da bancada;

- Calibrar sensores da bancada;

- Realizar experimentos e testes;

- Avaliar resultados obtidos;

- Produzir manual didático;

- Descrever melhorias a serem realizadas.

#### 2 Descrição da Bancada

A bancada de testes foi projetada para ser modular, sendo formada por quatro módulos de conversores da *Semikron*. Cada módulo possui oito IGBTs, quatro sensores de tensão e dois sensores de corrente. Além disso, para cada módulo existem um sensor de tensão e um sensor de corrente extras que podem ser usados conforme a necessidade de quem está realizando os experimentos. A Figura 2.1 mostra a estrutura da bancada. Para facilitar o entendimento das principais funcionalidades da bancada, dividiu-se a estrutura nos blocos A, B, C, D e E.

O dispositivo central da bancada é o microcontrolador, o DSP (digital signal processor), que realiza o processamento dos dados lidos nos sensores e que gera os sinais PWM para o chaveamento dos conversores. O modelo utilizado na bancada é o TMS320F28335, que é também o modelo usado na maioria das bancadas de testes do Laboratório, sendo assim sua compreensão de fundamental importância para a realização dos projetos de pesquisa, sobretudo para testar e implementar estratégias PWM diversificadas.

A transmissão de todos os sinais que provêm dos sensores para o DSP e que são enviados do DSP para o acionamento das chaves é feita em modo diferencial, isso porque os cabos por onde os sinais são transmitidos estão expostos a interferências magnéticas diversas. Logo, esses sinais são um somatório do sinal puro (S) mais ruído (R). A ideia de utilizar sinais diferenciais é duplicar o sinal S e inverter a fase de um deles, criando assim um sinal de fase invertida (-S). Os dois sinais são transmitidos em condutores diferentes pelo mesmo cabo e na parte receptora são colocados amplificadores diferenciais responsáveis por subtrair um sinal do outro. Como o ruído será idêntico nos dois condutores, considerando que eles estão muito próximos um do outro, o resultado será a eliminação do ruído (R) e a duplicação da amplitude do sinal. Então, por utilizar a transmissão em modo diferencial, os sinais têm maior imunidade a interferência eletromagnética e a os ruídos são diminuídos significativamente.

Em conformidade com essa última característica citada, os cabos utilizados para a transmissão dos sinais são cabos de rede feitos com cabos de par trançado do tipo UTP (*Unshielded Twisted Pair*) e o conector utilizado é o RJ-45, conforme a Figura 2.2. Esse cabo consiste em um par de fios elétricos de cobre. Os fios são recobertos de uma camada isolante, de plástico, e entrelaçados em forma de trança. Este entrelaçamento é feito para evitar a interferência eletromagnética entre cabos vizinhos e para aumentar a sua resistência. É um cabo de fácil manuseio e instalação.

Figura 2.1 – Fotos da bancada. (a) Foto frontal da estrutura. (b) Foto traseira da estrutura.

(a) TOTAL MARKET STATE OF THE STATE

Figura 2.2 – Cabo UTP com conector RJ-45

Nas seções seguintes serão discutidas em mais detalhes as funções de cada parte da bancada e os principais componentes que fazem parte de sua estrutura. Note também que a medida que a funcionalidade de cada bloco for sendo discutida serão apresentados também indicações de como foram realizadas as conexões e o caminho dos sinais.

#### 2.1 Especificações do Projeto

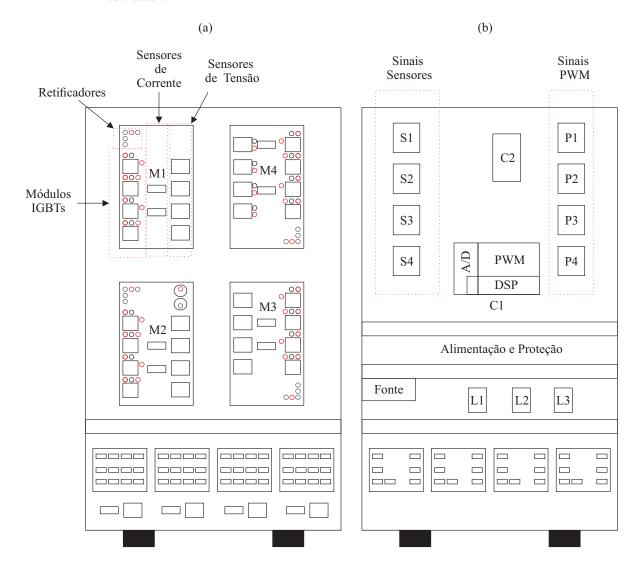

As Figuras 2.3 e 2.4 apresentam o *layout* da bancada de testes. Esta bancada disponibiliza o uso de até dezesseis braços com controle implementado por um processador digital de sinais, DSP. Na vista frontal observa-se os quatro módulos de conversores da *Semikron* identificados por M1, M2, M3 e M4 e os bornes de acesso aos terminais destes conversores. Na vista traseira nota-se as fontes de alimentação dos sensores e *drivers*, as placas que recebem sinais por meio dos cabos UTP/RJ-45, e o circuito de alimentação e proteção da bancada . Na vista lateral direita observa-se as botoeiras de energização e na vista lateral esquerda os terminais de força.

Figura 2.3 – Layout da bancada. (a) Vista frontal da estrutura. (b) Vista traseira da estrutura.

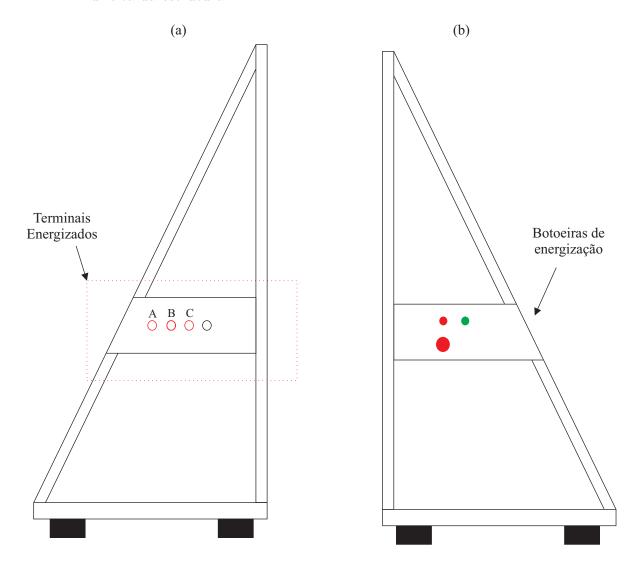

Figura 2.4 – Layout da bancada. (a) Vista lateral esquerda da estrutura. (b) Vista lateral direita da estrutura.

A bancada trabalha com uma corrente nominal de até 15A e uma tensão nominal de  $380V_{rms}$ .

#### 2.2 Bloco A: Proteção e Alimentação

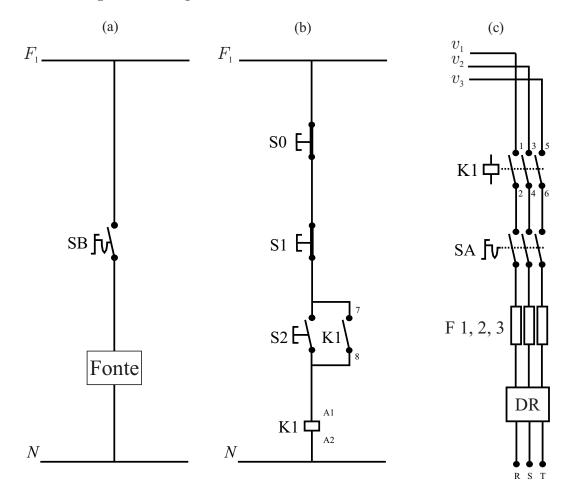

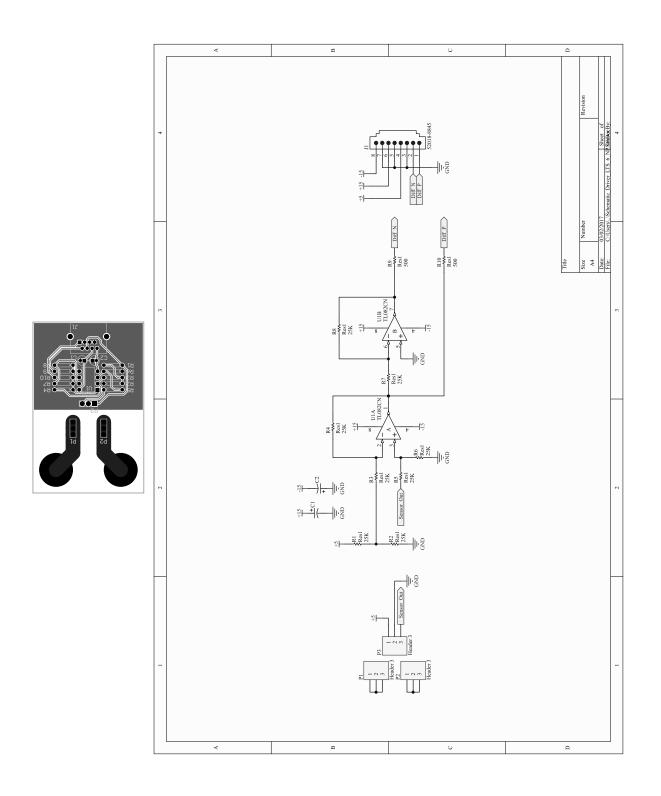

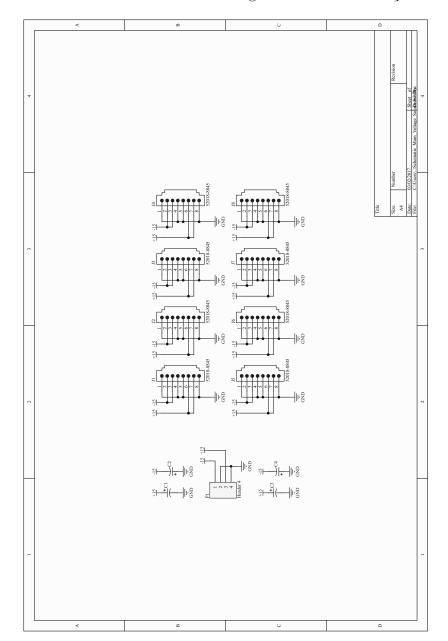

O Bloco A conforme a Figura 2.1 é responsável pela alimentação e proteção da bancada que é formada por um circuito monofásico e um circuito trifásico. O circuito monofásico é responsável por alimentar a fonte (15V e -15V) que por sua vez alimenta todos os sensores e os *drivers*. Já o circuito trifásico é utilizado na realização dos experimentos, por exemplo, para alimentar uma máquina ou uma carga trifásica. A Figura 2.5 mostra os diagramas de comando e de força da bancada e a Figura 2.6 os componentes que fazem parte desse circuito e que foram aqui referenciados.

O circuito de proteção está instalado entre o varivolt e os bornes R, S e T da bancada que possui um disjuntor monofásico modelo MDW C16 da WEG que suporta uma corrente nominal de 16A e um disjuntor trifásico modelo MDW C20 que suporta uma corrente nominal de 20A. Possui também fusíveis convencionais (500V, 25A) e um disjuntor residual tetrapolar. Logo, esse circuito é projetado para atuar quando submetido a uma corrente de 20A. O circuito de proteção desempenha um papel importante no que diz respeito a garantir a segurança dos componentes da bancada e também das pessoas que estão realizando os experimentos.

Figura 2.5 – Diagramas elétricos. (a) Circuito monofásico. (b) Diagrama de comando. (c) Diagrama de força

Figura 2.6 – Componentes do circuito de proteção da bancada

Antes de ligar a bancada é necessário que o disjunto monofásico, o disjuntor trifásico e o disjuntor residual sejam ligados. A bancada dispões de três botoeiras, uma verde, que deve ser acionada para ligar o circuito trifásico, uma vermelha que quando acionada desliga o circuito trifásico e uma de emergência, conforme a Figura 2.7. Além disso, um varivolt trifásico está ligado a bancada, permitindo que se trabalhe com diferentes níveis de tensão. Tem-se acesso a tensão do varivolt por meio dos terminais mostrados na Figura ??.

Figura 2.7 – Botoeiras de Energização

Figura 2.8 – Terminais de acesso a tensão do varivolt

#### 2.3 Bloco B: Módulos - Conversores

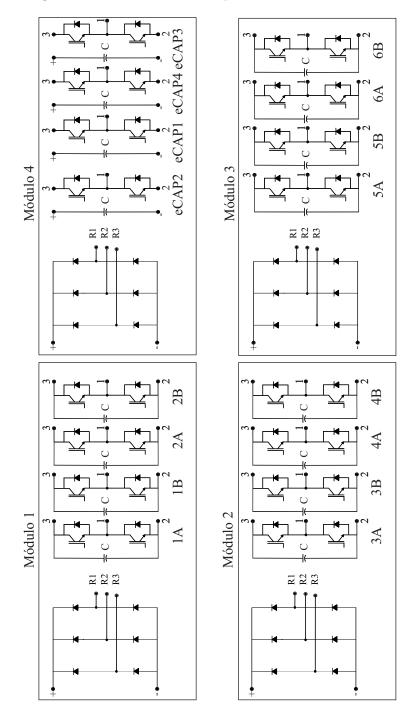

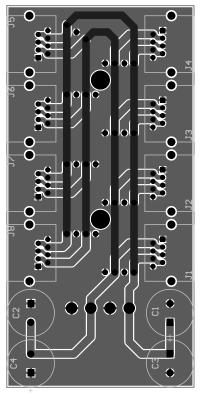

O Bloco B é formado por quatro módulos de conversores da *Semikron*, cada um com quatro braços, *drivers* de acionamento de cada braço do conversor, uma ponte retificadora trifásica e outros itens de proteção e segurança do conversor, como dissipador de calor e estrutura mecânica para montagem e fixação.

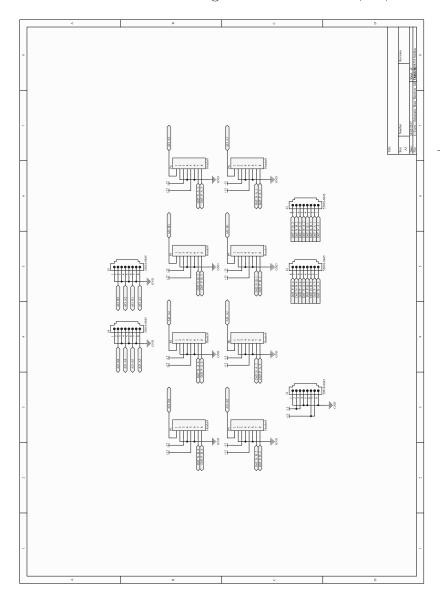

A Figura 2.9 apresenta o mapeamento de todas as conexões ao Bloco B. Por meio desse bloco pode-se entender como as chaves IGBTs e os sensores estão conectados ao DSP, já que as conexões dos sensores e *drivers* estão nomeados conforme o código base para programação do DSP. E os bornes de ligação dos braços dos conversores são enumerados 1 (ponto central), 2 (ponto -DC) e 3 (ponto DC). Os bornes de ligação dos braços retificadores são nomeados R1, R2 e R3.

Sensores Sensores de Corrente de Tensão R) (+) (-) Retificadores 23 R3 N4 21 32 1A eCP1 321 23 N1 21 1B N1\_12 eCP4 Módulos 32 1023 **IGBTs** 2A eCP3 N1 22 321 2B N1\_14 -  $\mathbb{R}$ ® ⊕ ⊙ 23 (C) N3\_11 5A 123 32 5B N3 12 N3 21 3A M2321 23 N2\_21 N2\_12 N3\_13 N3\_22 6A 3B 32 1003 N2\_13 N3\_14 6B 4A N2 22 321 N2 14 4B  $\bigcirc \oplus \mathbb{R}$ N1\_11 N1\_12 N1\_13 N1\_14 N2\_11 N2\_12 N2\_13 N2\_14 N3\_11 N3\_12 N3\_13 N3\_14 N4\_11 N4\_12 N4\_13 N4\_14 N1\_21 N1\_22 N1\_23 N1\_24 N2\_21 N2\_22 N2\_23 N2\_24 N3\_21 N3\_22 N3\_23 N3\_24 N4\_21 N4\_22 N4\_23 N4\_24 1A 1B 2A 2B 3A 3B 4A 4B 5A 5B 6A 6B eCP2 eCP1 eCP4 eCP3 N1\_23 N1 24 N2\_23 N2 24 N3\_23 N4\_23 N3 24 N4 24

Figura 2.9 – Conexões do Bloco B

O circuito correspondente a cada módulo é mostrado na Figura 2.10.

Figura 2.10 – Circuito correspondente a cada módulo

Cada braço que compõe os módulos possuem dois IGBTs do tipo SKM50GB123D, e os retificadores em cada módulo são constituídos por diodos do tipo SKKD 46/12, ambos da Semikron e ilustrados na Figura 2.11. Cada braço está ligado em paralelo com um capacitor eletrolítico (C) de 4700  $\mu$ F. Além disso, a bancada disponibiliza dois capacitores eletrolíticos extras de 2200  $\mu$ F que podem funcionar como barramentos auxiliares.

Figura 2.11 – IGBTs e Diodos

Na Figura 2.10 nota-se também que o Módulo 4 apresenta algumas alterações em relação aos demais, pois nele os braços não estão conectadas aos capacitores, permitindo assim uma melhor flexibilidade no seu uso e, além disso, os sinais enviados do DSP para os drivers das chaves são os sinais eCAP, limitando o tipo de portadoras que podem ser usadas na geração dos sinais para os IGBTs. Nesse caso, podem ser usadas apenas portadoras do tipo dente de serra.

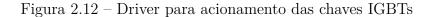

O chaveamento em cada braço é controlado por meio de drivers do tipo SKI22B(R) da SEMIKRON que transmite tanto o sinal direto como o sinal complementar para os IGBTs. Na bancada, eles já estão inseridos em uma placa de circuito impresso em que são realizadas todas as conexões necessárias conforme a Figura 2.12. Essa placa é denominada SKPC 22/2 e possui muitas funcionalidades interessantes. Uma delas é permitir o acesso mais prático ao sinal PWM que é enviado às chaves por meio dos pinos indicados na Figura 2.12 e também possibilitar a configuração do dead-time dos sinais transmitidos aos IGBTs, que funciona como uma proteção já que, se os mesmos sinais fossem enviados para os IGBTs ao mesmo tempo e o driver permitisse isso, o barramento capacitivo seria curto-circuitado, o que não é desejável. Todos os drivers da bancada estão configurados com um dead-time de 1,5  $\mu$ s.

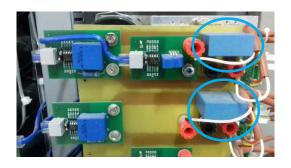

A cada um dos braços estão associados snubbers capacitivos conectados em paralelo com as chaves IGBTs, conforme a Figura 2.13. Os snubbers são circuitos amortecedores, inseridos em conversores estáticos de potência, cuja função é controlar os efeitos produzidos pelas reatâncias intrínsecas do circuito. Assim, nesses circuitos altas correntes são chaveadas, ocorrendo overshoots de tensão que, se não forem amenizados, podem destruir as chaves semicondutoras. Então, os snubbers desempenham um papel importante neste sentido podendo ser usados para amortecer essas oscilações e controlar a taxa de variação de tensão e/ou corrente sobre as chaves, fazendo com que os semicondutores apresentem uma menor dissipação de potência média e picos menores de tensão, corrente e potência dissipada. Dessa forma, resultando em maior confiabilidade, maior eficiência, e menor interferência eletromagnética (EMI). A Figura 2.14 mostra uma comparação da tensão sobre um IGBT no seu bloqueio com e sem o capacitor snubber e o circuito equivalente com as reatâncias parasitas e o capacitor snubber.

Figura 2.13 - Snubber

Figura 2.14 – Vantagem de se usar *snubbers*

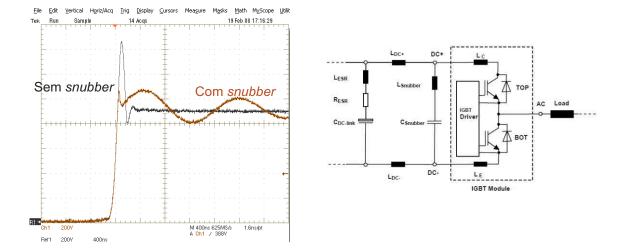

Cada módulo possui também quatro sensores de tensão, um em cada barramento capacitivo, e dois sensores de corrente, na entrada dos dois braços centrais do módulo. Os sensores de tensão são do tipo LV 20-P da LEM Components conforme mostrado na Figura 2.15, que é um sensor de efeito *hall* adequado para medir tensões de 10 a 500V. Os sensores enviam sinais de 0 a 3,3V para o DSP e são alimentados por +15V e -15V. Esse sensor possui boas características no que diz respeito a precisão, linearidade, e alta imunidade a fontes externas de interferência.

Figura 2.15 – Sensor de tensão LV-20P

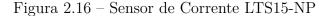

Os sensores de corrente usados são do tipo LTS15-NP da LEM Components conforme ilustrado na Figura 2.16. O sensor de corrente também é do tipo hall e tem como principais características: excelente precisão, boa linearidade, pequenas perdas (resistência série inferior a 1,62 m $\Omega$ ), imunidade a interferências externas e elevada capacidade de corrente. A alimentação desse sensor é +5V, para tanto, nas placas do Bloco E existe um

regulador de tensão LM1086 da Texas Instruments conforme Figura 2.17 que recebe uma tensão de 15V e faz a regulação em 5V.

Figura 2.17 – Regulador de tensão LM1086

#### 2.4 Bloco C: Alimentação dos sensores e drivers

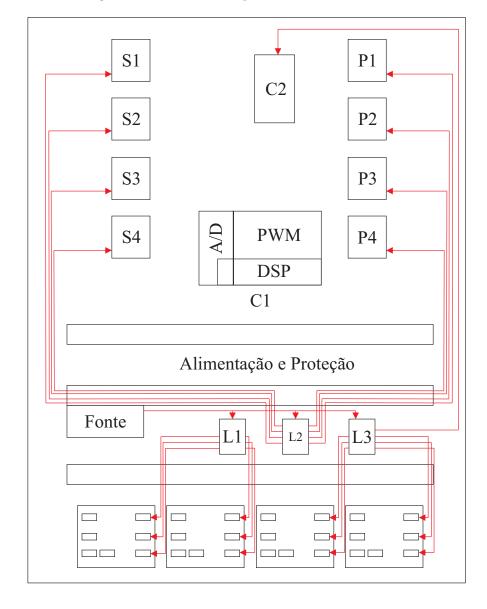

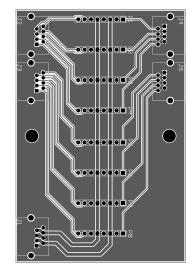

O Bloco C mostrado na Figura 2.18 é formado por uma fonte RT 125C da *Mean Well (MW)* com saídas -15V, GND e 15V. Essas saídas são distribuídas para as placas L1, L2 e L3, que por sua vez vão distribuir essas tensões para alimentar os sensores e os *drivers*. A Figura 2.19 apresenta um mapeamento das conexões entre as placas L1, L2 e L3 aos circuitos alimentados com 15V e -15V.

Figura 2.18 – Foto do circuito de alimentação dos sensores e drivers

Figura 2.19 – Alimentação de sensores e drivers

#### 2.5 Bloco D: Sinais dos sensores e sinais PWM drivers

As conexões no Bloco D são apresentadas na Figura 2.20.

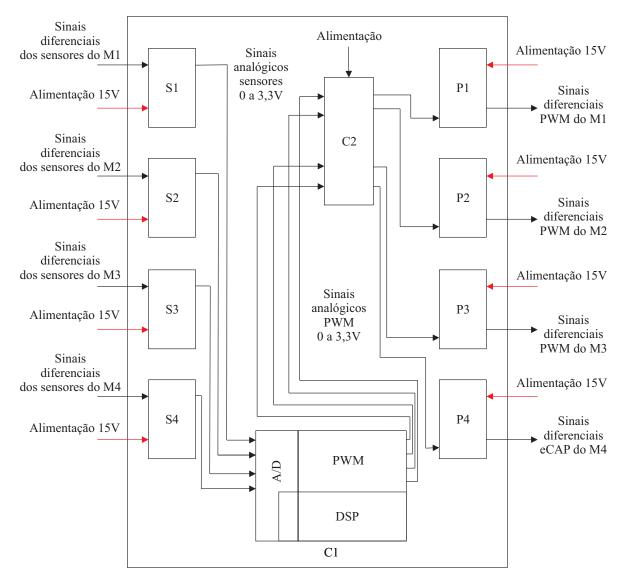

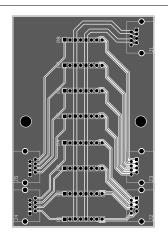

As placas S1, S2, S3 e S4 recebem os sinais diferenciais dos sensores, que passarão por uma interface que vai somar os sinais com fases opostas de cada sensor, tornando-os um único sinal. Assim, os dados lidos em cada sensor são enviados para o sub-bloco C1, onde encontra-se também o DSP.

O sub-bloco C1 é dividido fisicamente. A placa que contém as trilhas por onde são enviados os sinais para os drivers que acionarão as chaves é separada da placa que contém as trilhas por onde são recebidos os dados dos sensores. No caso dos sensores existe uma interface entre os pinos dos conectores e os pinos A/D (Analógico/Digital) do

Figura 2.20 – Conexões no Bloco D

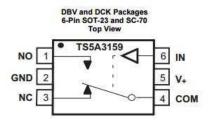

DSP. Isso se dá porque a bancada possui 32 entradas de sensores e o DSP possui apenas 16 entradas A/D. Então, para solucionar o problema viu-se que era necessário usar oito chaves analógicas do tipo TS5A3159 da *Texas Instruments* como mostra a Figura 2.21, cada uma com duas entradas, uma saída e um pino de seleção. Essa chaves funcionam basicamente como um MUX 32:16 já que para todas elas é enviado o mesmo sinal de seleção. Logo, em metade do período são lidas 16 entradas de sensores simultaneamente e na outra metade as 16 restantes. O sinal para o pino de seleção é enviado pelo DSP.

Figura 2.21 – Características da chave analógica TS5A3159

| D1  | -  |     |     | -  |

|-----|----|-----|-----|----|

| Pin | τu | ınc | LIO | n. |

|     |    |     |     |    |

| PIN |      | 1/0     | DESCRIPTION                                                           |  |

|-----|------|---------|-----------------------------------------------------------------------|--|

| NO. | NAME | 100     | DESCRIPTION                                                           |  |

| 1   | NO   | 1/0     | Normally open switch port                                             |  |

| 2   | GND  | ( HE-5) | Ground                                                                |  |

| 3   | NC   | 1/0     | Normally closed switch port                                           |  |

| 4   | СОМ  | I/O     | Common switch port                                                    |  |

| 5   | V+   | ** ==:  | Power supply                                                          |  |

| 6   | IN   | 1       | Switch select. High = COM connected to NO; Low = COM connected to NC: |  |

Além disso, a parte de sensoriamento (A/D) está separada da parte dos drivers contribui para que não haja interferência entre os dois planos de terra, já que o plano de terra digital é separado do plano de terra analógico. Existe a necessidade de rotear as trilhas em caminhos separados até a fonte para os circuitos analógicos em relação aos digitais devido às grandezas envolvidas (tensão, corrente e frequência), pois os chaveamentos digitais provocam mudanças abruptas no comportamento da tensão e corrente da fonte, e, esse comportamento é refletido nas trilhas de alimentação. Assim, as correntes de chaveamento dos circuitos digitais podem induzir ruídos nos circuitos analógicos e prejudicar a medição das grandezas nos sensores.

No que diz respeito a conexão dos drivers ao DSP têm-se que os pinos do DSP estão conectados diretamente aos pinos dos conectores. O DSP TMS320F28335 possui 12 saídas PWM e 6 saídas eCAP (na bancada, são usadas quatro). Como cada módulo possui quatro braços, e cada braço possui dois IGBTs que são complementares entre si, os sinais PWM gerados pelo DSP são enviados primeiramente para a placa C2 que contém CI's SN74HC541N e SN74HC540N da Texas Instrumentos (ver Figura 2.22). O primeiro, com entradas e saídas de lados opostos, funciona apenas como um buffer, ou seja, o que está na entrada é enviado diretamente para a saída, e o segundo, também com entradas e saídas de lados opostos, inverte o sinal da entrada e o coloca na saída. Esse sinal invertido será enviado para a chave complementar correspondente de cada braço. Os 12 sinais PWM e 4 sinais eCAP, com seus complementares, são enviados para as placas P1, P2, P3 e P4 que tornarão esses sinais diferenciais e por sua vez esses sinais são enviados aos drivers dos módulos M1, M2, M3 e M4, respectivamente. Antes de chegarem nas chaves existe uma interface que vai somar os sinais diferenciais com fases opostas, tonando-os um único sinal que vai ser enviado para o gate dos IGBTs.

SN54HC541 . . . J OR W PACKAGE SN74HC541 . . . DB, DW, N, NS, OR PW PACKAGE (TOP VIEW) OE1 A1 OE2 19 18 A2 Y1 18 A3 Y2 A4 A5 To Seven Other Channels A6 A7 8 A8 9 12 Y7 GND 10 SN54HC540 . . . J OR W PACKAGE SN74HC540 . . . DB, DW, N, NS, OR PW PACKAGE (TOP VIEW) OE1 A1 OE2 A2 [ A3 4 18 A4 [ 1 Y3 A5 A6 Y5 A7 To Seven Other Channels A8 [] GND [

Figura 2.22 – CI's SN74HC541N e SN74HC540N

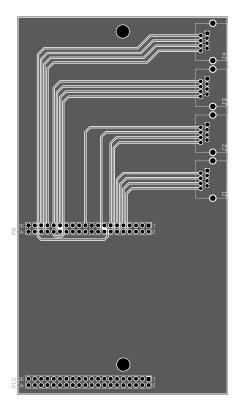

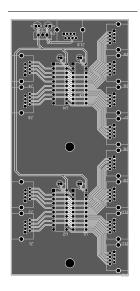

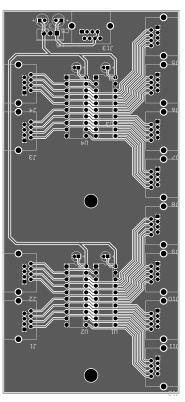

#### 2.6 Bloco E: Roteamento

No Bloco E apresentado na Figura 2.23 estão as placas com trilhas que servirão como rota física para organizar os sinais provindos da parte posterior da bancada para a parte frontal. Na parte posterior chegam os sinais PWM e os sinais dos sensores separados da alimentação, então, nas placas os sinais são reorganizados e na parte frontal os cabos que são conectados a cada sensor e a cada driver contêm tanto o sinal correspondente como a sua alimentação.

Figura 2.23 – Conexões no Bloco E. (a) Vista traseira. (b) Vista frontal

(a)

N1\_11 N1\_12 N1\_13 N1\_14 N2\_11 N2\_12 N2\_13 N2\_14 N3\_11 N3\_12 N3\_13 N3\_14 N4\_11 N4\_12 N4\_13 N4\_14 N1\_21 N1\_22 N1\_23 N1\_24 N2\_21 N2\_22 N2\_23 N2\_24 N3\_21 N3\_22 N3\_23 N3\_24 N4\_21 N4\_22 N4\_23 N4\_24 1A 1B 2A 2B 3A 3B 4A 4B eCP2 eCP1 eCP4 eCP3 N1 23 N1 24 N2 23 N2 24 N3 23 N3 24 N4 23 N4 24

(b)

#### 2.7 Microprocessador

Para o processamento dos sinais digitais é utilizado um DPS, que é um microprocessador de sinais digitais que tem velocidade operacional superior quando comparado a outros microcontroladores, além de ser otimizado em relação ao cancelamento de ruídos. Na bancada utiliza-se o kit eZdsp TMS 320F28335, fabricado pela *Texas Instruments*, mostrado na Figura 2.24.

Figura 2.24 – Kit eZdsp TMS 320F28335

O DSP comunica-se com o computador por meio da interface USB. O software utilizado para a programação do DSP é o CCS (Code COmposer Studio) v3.3, que permite escrever, compilar e carregar o código no DSP em C/C++ e em Assembler. O modelo utilizado TMS320F28335 é um dispositivo de alta performance baseado na tecnologia CMOS, podendo operar a 1,8V ou a 1,9V, além de gerar em suas portas I/O um sinal máximo de 3,3V. Pode trabalhar até uma frequência de 150MHz, o que corresponde a um tempo de ciclo de 6,67ns. Possui uma CPU de 32 bits, barramentos com arquitetura Harvard, um controlador DMA de seis canais, interface externa de 16 ou 32 bits, memória interna (Flash 256K x 16, SARAM 34K x 16 e OTP-ROM 1K x 16) e uma memória ROM 8K x 16 para boot. Possui também diversos recursos como 3 temporizadores integrados à CPU, 88 pinos configuráveis de entrada e saída de uso geral (GPIO), 12 saídas EPWM, um módulo ADC de 16 canais de 12-bits, com taxa de conversão de 80ns, dentre outras características que podem ser consultadas no manual do fabricante. Assim, para aproveitar as diversas funcionalidades do DSP é importante antes configurá-lo e programá-lo adequadamente.

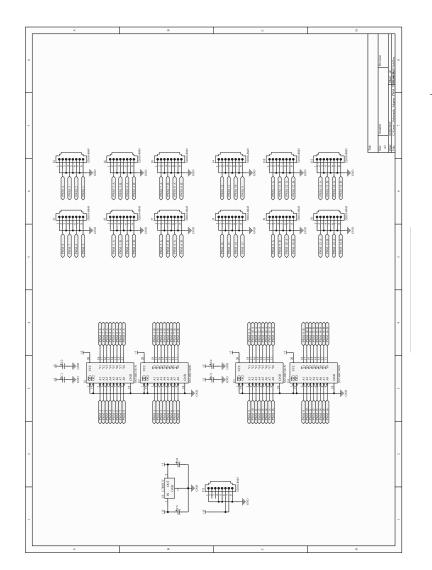

#### 2.8 Diagramas Técnicos

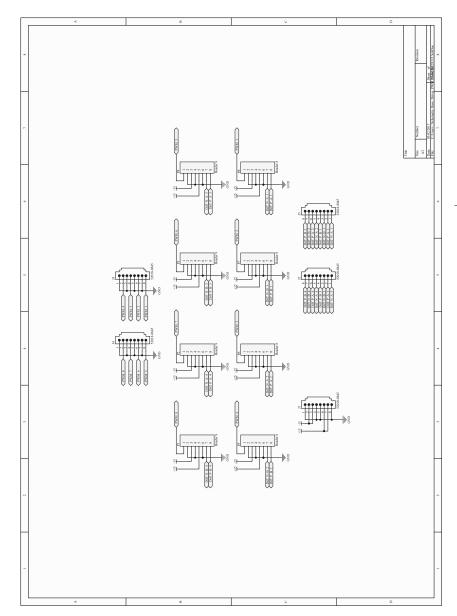

Nesta seção serão apresentados os diagramas técnicos apresentando todas as ligações realizadas entre os componentes da bancada e o DSP. Os diagramas aqui mostrados foram produzidos por alunos do mestrado e doutorado que participaram na elaboração do projeto e montagem da bancada.

Figura 2.25 – Ligações do sensor de corrente LTS15-NP

Figura 2.26 – Ligações do sensor de tensão LV-20P

Figura 2.27 – Alimentação dos sensores

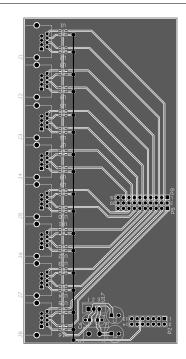

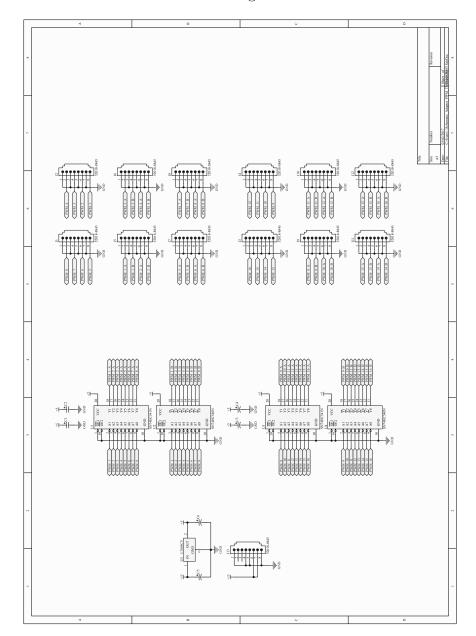

Figura 2.28 – Placas S1, S2, S3 e S4

Resil Resil

Figura 2.29 – Junção dos sinais diferenciais dos sensores

Figura 2.30 – Conexões dos sensores ao DSP

Figura 2.31 – Conexões dos drivers ao DSP

Figura 2.32 – Alimentação

Figura 2.33 – Sinais PWM

Figura 2.34 – Sinais PWM e seus complementares

Figura 2.35 – Sinais PWM diferenciais

Figura 2.36 – Interface - Sinais PWM

Figura 2.37 – Sinais PWM para os drivers

Resi Resi IK

Figura 2.38 – Sinais dos  $\mathit{drivers}$  para os IGBTs

## 3 Resultados Experimentais

A bancada descrita nesse relatório é usada por muitos alunos do mestrado e doutorado para coletar resultados experimentais. Então, durante o estágio realizou-se testes para averiguar o funcionamento dos dispositivos que compõem a bancada.

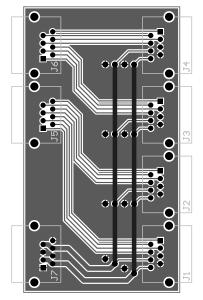

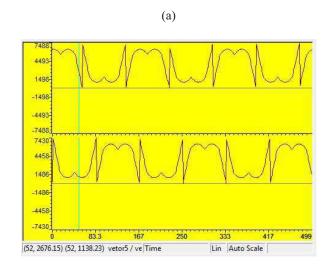

Primeiramente, foram testados o funcionamento do DSP e dos *drivers*. Para tanto, foi usada uma rotina que emitisse sinais PWM para todas as chaves e foi verificado os sinais e seus complementares por meio dos pinos P(sinal) e N(referência) do *driver*. A Figura 3.1 mostra o sinal de gatilho dos IGBTs. É interessante que esse procedimento seja realizado antes da realização de qualquer experimento para atestar o funcionamento adequado do DSP e das chaves.

Figura 3.1 – Teste dos *drivers* e IGBTs

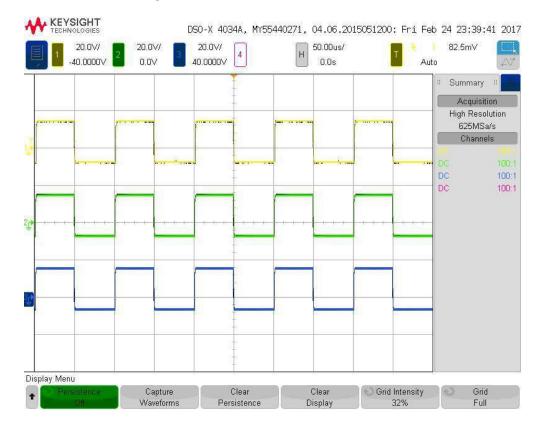

Em seguida montou-se uma topologia de conversor multinível proposta em [1] funcionando como um inversor. Essa topologia é formada por três conversores de três braços em cascata, conforme a Figura 3.2. Usou-se uma carga equilibrada que consistiu em uma carga indutiva L=7mH em série com uma carga resistiva  $R=38,6\Omega$  (conjunto de lâmpadas incandescentes) e a tensão aplicada nos barramentos foi de aproximadamente

$V_c=270V$ . E a técnica de PWM usada foi a Level-Shifted usando as portadores mostradas na Figura 3.3. A Figura 3.4 apresenta a montagem realizada.

Figura 3.2 – Esquema de ligação da topologia testada

Figura 3.3 – Portadoras utilizadas na estratégia Level-Shifted PWM

No osciloscópio observaram-se as formas de onda da tensão sobre a carga e a corrente na carga conforme a Figura 3.5. Observou-se também os sinais PWM enviados a três braços de um módulo e a média desses sinais, conforme Figura 3.6.

KEYSIGHT DSO-X 4034A, MY55440271, 04.06.2015051200: Tue Feb 21 23:56:20 2017 5.00A/ 5.000ms/ 10.0000A -200.000V 0.0s Auto Reactive(1→2): Incomplete DC RMS - Cyc(1): 199V Freq(1): 60.500Hz AC RMS - Cyc(2): 5.1437A AC RMS - Cyc(3): No signal AC RMS - Cyc(1): 198.82V AC RMS - Cyc(4): No signal Display Menu Persistence

Figura 3.5 – Resultado Experimental

Figura 3.6 – Sinais PWM enviados aos *drivers*. (a) Sinal no *gate* dos IGBTs. (b) Valor médio dos sinais PWM

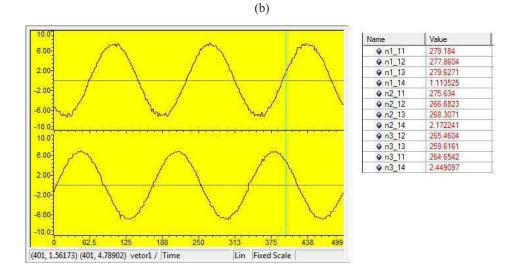

Já a Figura 3.7 apresenta os resultados observados no CCS v3.3. A Figura 3.7(a) mostra as referências geradas e a Figura 3.7(b) mostra os valores lidos nos sensores de corrente dos braços 2A e 4A (correntes da carga) e nos sensores de tensão nos barramentos

utilizados.

Figura 3.7 – Resultado obtidos no CCS v3.3. (a) Referências geradas. (b) Leitura nos sensores de corrente e tensão.

Os valores lidos pelos sensores foram satisfatórios, apesar de algumas imprecisões nos valores de tensão no barramento. Isso ocorre devido a serem usados retificadores não-controlados no experimento e transformadores não ideias para isolar os barramentos. Como os sensores estavam funcionando adequadamente não houve necessidade de calibrá-los, assim como havia sido proposto no início do estágio.

## 4 Conclusões

Por meio das atividades realizadas durante o Estágio Supervisionado foi possível entender o funcionamento de uma bancada de testes para conversores estáticos disponível no LEIAM. Explorou-se o entendimento do sistema elétrico que faz parte da estrutura da bancada, os circuitos eletrônicos que envolvem toda a montagem e as características do DSP (TMS320F28335) que é utilizado para implementar as estratégias de controle, processar os dados lidos nos sensores e enviar os sinais de gatilho para os IGBTs.

Por meio dos conhecimentos adquiridos foi possível iniciar e progredir significativamente na produção de um guia técnico que descreve as principais características construtivas e as funcionalidades da bancada, faz o mapeamento de todas as suas conexões e exemplifica por meio de testes experimentais como podem ser realizadas as ligações na bancada. Esse guia foi apresentado na forma deste relatório. Porém, alguns detalhamentos ainda poderão ser acrescentados, como por exemplo, mais informações sobre o uso do DSP e sua programação.

Esse guia ficará disponível na bancada para que outros alunos tenham acesso, o que será de ajuda principalmente para os novos alunos que estão sendo inseridos nas atividades práticas do Laboratório. Além disso, ter disponível o mapeamento das conexões poderá auxiliar na identificação de falhas ocorridas durante os experimentos. Sendo assim, a partir dessas considerações, pode-se concluir que o estágio atingiu o objetivo proposto.

## Referências

[1] Edgard Luiz Lopes Fabrício. Sistemas de compensação em derivação baseados em conversores paralelos e interconectados. Tese(doutorado), Universidade Federal de Campina Grande, Campina Grande, 2015. Citado na página 47.