## Universidade Federal de Campina Grande Centro de Engenharia Elétrica e Informática Programa de Pós-graduação em Engenharia Elétrica

## Avanços em Conversores Fonte de Corrente

Louelson Afranio Leugirdes de Azevedo Cavalcanti Costa

## Universidade Federal de Campina Grande Centro de Engenharia Elétrica e Informática Programa de Pós-graduação em Engenharia Elétrica

## Avanços em Conversores Fonte de Corrente

### Louelson Afranio Leugirdes de Azevedo Cavalcanti Costa

Tese de Doutorado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Campina Grande, como parte dos requisitos necessários para obtenção do grau de Doutor em Ciências, no domínio da Engenharia Elétrica.

Área de Concentração: Processamento de Energia

Prof. Maurício Beltrão de Rossiter Corrêa Prof. Montiê Alves Vitorino Orientador(es)

> Campina Grande – PB, Brasil Março de 2020

C837a Costa, Louelson Afranio Leugirdes de Azevedo Cavalcanti.

Avanços em conversores fonte de corrente / Louelson Afranio Leugirdes de Azevedo Cavalcanti Costa. – Campina Grande, 2020. 140 f.: il. color.

Tese (Doutorado em Engenharia Elétrica) — Universidade Federal de Campina Grande, Centro de Engenharia Elétrica e Informática, 2020.

"Orientação: Prof. Dr. Maurício Beltrão de Rossiter Corrêa, Prof. Dr. Montiê Alves Vitorino".

Referências.

1. Processamento de Energia. 2. Assimétrico. 3. Conversor Fonte de Corrente. 4. Número Reduzido de Chaves Ativas. 5. Tipo-X. I. Corrêa, Maurício Beltrão de Rossiter. II. Vitorino, Montiê Alves. III. Título.

CDU 621.31(043)

FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECÁRIA SEVERINA SUELI DA SILVA OLIVEIRA CRB-15/225

## AVANÇOS EM CONVERSORES FONTE DE CORRENTE

## LOUELSON AFRANIO LEUGIRDES DE AZEVEDO CAVALCANTI COSTA

TESE APROVADA EM 02/03/2020

MAURÍCIO BELTRÃO DE ROSSITER CORRÊA, D.Sc., UFCG

Orientador(a)

MONTIFALVES VITORINO, D.Sc., UFCG

Orientador(a)

ALEXANDRE CUNHA OLIVEIRA, D.Sc., UFCG

Examinador(a)

CURSINO BRANDÃO JACOBINA, Dr.Ing., UFCG

Examinador(a)

DEMERCIL DE SOUZA OLIVEIRA JÚNIOR, Dr. UFC Examinador(a)

MARCELO LOBO HELDWEIN, Dr., UFSC Examinador(a)

CAMPINA GRANDE - PB

## Agradecimentos

À minha companheira Nayara Brandão, que me ajudou de diversas formas em minha jornada acadêmica, e também fora dela.

Aos meus pais, Lourdes e Nelson, e ao meu irmão Sedru, por terem provido uma boa educação dentro e fora de casa, e pelo apoio aos meus estudos.

Aos meus orientadores, Professor Maurício e Professor Montiê, pela confiança, orientação e ensinamentos que ma passaram ao longo desta etapa da minha vida.

Aos Professores Dushan Boroyevich e Rolando Burgos, pela sua aceitação no período da minha estada nas instalações da Virginia Tech (EUA). Ao colega Boran Fan, que foi fundamental para os trabalhos desenvolvidos na Virginia Tech.

Aos amigos André Wild, Nayara Ingrid e Ruan Gomes pelo auxílio técnico dado ao desenvolvimento desta pesquisa. Aos amigos Eduardo Pereira, Fancisco Revson, Jõao Paulo, Phelipe Leal e Reuben Palmer pelos momentos de descontração dentro e fora do laboratório. Aos amigos Vinícius Fagundes, Rajiv Albino e Raul Felipe pelo apoio (não-técnico) ao meus estudos.

Aos técnicos do LEIAM, Wellington Lima e Paulo Miranda, que foram essenciais para a etapa prática/experimental deste trabalho. Ao CNPq e CAPES, por terem fornecido suporte financeiro para a realização desta pesquisa.

À coordenação, professores e funcionários da Universidade Federal de Campina Grande e da Virginia Polytechnic Institute and State University que contribuíram, de forma direta ou indireta, com a realização deste trabalho.

$\label{eq:consequences.} \textit{"Prepare for unforeseen consequences."} \\ \textit{G-Man, Half-life}$

## Resumo

Este trabalho tem os conversores fonte de corrente como objetos de estudo e é dividido em duas partes: Parte I - conversores fonte de corrente ponte-H monofásicos; e Parte II conversores fonte de corrente tipo-X. O objetivo final deste trabalho é desenvolver novas topologias de modo a tornar os conversores fonte de corrente mais competitivos. Visa-se encontrar soluções de eletrônica de potência que aumentem a eficiência e/ou densidade de potência do conversor sem que haja prejuízo para o funcionamento e qualidade da energia elétrica processada. A Parte I busca soluções de conversores ponte-H monofásicos com número reduzido de chaves controladas (assimétricos). Além de apresentar a topologia ponte-H monofásica convencional, abordando aspectos comuns às topologias fonte de corrente monofásicas, estuda-se topologias assimétricas com três níveis e multiníveis. Apesar de ter os objetivos alcançados na Parte I, a baixa densidade de potência dos conversores monofásicos motiva o estudo dessas topologias em suas versões multifásicas. A Parte II aborda soluções multifásicas visando a redução do número de chaves e de perdas por condução dos conversores. A exemplo da Parte I, as discussões específicas sobre as novas topologias foram estruturadas por considerações inerentes a topologias fonte de corrente convencionais. Revisa-se a topologia tipo-X bifásica, apresenta-se sua generalização e suas versões assimétricas com substituição de chaves ativas por diodos. Também é feito um estudo de uma técnica de sincronismo que objetiva reduzir a oscilação da corrente do barramento CC de conversores fonte de corrente CA-CC-CA monofásicos. Todas proposições são validadas via resultados de simulações e/ou experimentais, mostrando a sua exequibilidade e melhorias quando comparadas com as soluções convencionais.

Palavras-chave: assimétrico, conversor fonte de corrente, monofásico, multifásico, multinível, número reduzido de chaves ativas, tipo-X.

## Abstract

This work aims to study the current source converters being divided in two parts: Part I - Hbridge single-phase current source converters; and Part II - X-type current source converters. The main objective of this work is to develop new topologies that can increase the current source converter competitiveness. The research is guided towards the development of new power electronics solutions that can increase the efficiency and/or power density without compromising the power quality or the operation of the converter. Part I studies H-bridge single-phase converters solutions with reduced active switch count (asymmetric topologies). Besides the conventional single-phase topology, three-level and multilevel topologies are studied. Besides the achievement of the proposed objectives in Part I, the low power density of single-phase converters motivated the study of the multiphase version of the topologies studied in Part I. Part II regards multiphase solutions, aiming the reduction of active switch count and power losses. As done in Part I, the presentation of the new topologies is structured by inherent characteristics of the conventional multiphase current source converters. The two-phase X-type current source converter is reviewed, being followed by the proposal of its generalized solution (multiphase), after that, the assymetrical technique presented on Part I is applied to the X-type current source converters, resulting in the asymmetrical X-type topologies. Also a synchronization technique for single-phase AC-DC-AC converters is presented, aiming to reduce the DC-link current oscillation. The presented topologies are validated via simulation and/or experimental results, showing their feasibility and improvements when compared to the conventional converters.

**Keywords**: asymmetric, current source converter, multilevel, multiphase, reduced active switch count, single-phase, X-type.

# Sumário

| Re           | esum  | 10                                                     | X1           |  |  |  |  |

|--------------|-------|--------------------------------------------------------|--------------|--|--|--|--|

| $\mathbf{A}$ | bstra | nct                                                    | ii           |  |  |  |  |

| Sυ           | ımár  | io                                                     | $\mathbf{v}$ |  |  |  |  |

| Li           | sta d | le ilustrações                                         | ix           |  |  |  |  |

| Li           | sta d | le tabelas                                             | iii          |  |  |  |  |

| Li           | sta d | le abreviaturas e siglas                               | $\mathbf{v}$ |  |  |  |  |

| Li           | sta d | le símbolos                                            | vii          |  |  |  |  |

| 1            | Intr  | rodução geral                                          | 1            |  |  |  |  |

|              | 1.1   | Conversores fonte de corrente                          | 1            |  |  |  |  |

|              | 1.2   | Objetivos                                              | 5            |  |  |  |  |

|              | 1.3   | Justificativas                                         | 6            |  |  |  |  |

|              | 1.4   | Contribuições do trabalho                              | 6            |  |  |  |  |

|              | 1.5   | Revisão bibliográfica                                  | 7            |  |  |  |  |

|              | 1.6   | Organização do trabalho                                | 10           |  |  |  |  |

|              |       |                                                        |              |  |  |  |  |

| Ι            | Co    | nversores fonte de corrente ponte-H monofásicos 13     |              |  |  |  |  |

| <b>2</b>     |       | -                                                      | .5           |  |  |  |  |

|              | 2.1   |                                                        | 15           |  |  |  |  |

|              | 2.2   |                                                        | 16           |  |  |  |  |

|              | 2.3   |                                                        | 17           |  |  |  |  |

|              |       | 2.3.1 Indutor do barramento CC                         | 18           |  |  |  |  |

|              |       | 2.3.2 Capacitor do barramento CA                       | 19           |  |  |  |  |

|              | 2.4   |                                                        | 22           |  |  |  |  |

|              |       | 2.4.1 Inversor fonte de corrente                       | 23           |  |  |  |  |

|              |       | 2.4.1.1 Controle da corrente do barramento CC          | 23           |  |  |  |  |

|              |       | 2.4.1.2 Controle do barramento CA                      | 24           |  |  |  |  |

|              |       | 2.4.2 Retificador fonte de corrente                    | 24           |  |  |  |  |

|              | 2.5   | Resultados de simulações e experimentais               | 25           |  |  |  |  |

|              | 2.6   | Conclusão                                              | 27           |  |  |  |  |

| 3            | Ret   | dificadores fonte de corrente monofásicos assimétricos | 29           |  |  |  |  |

|              | 3.1   | Introdução                                             | 29           |  |  |  |  |

|              | 3.2   | Operação e modulação                                   | 31           |  |  |  |  |

|              |       | 3.2.1 Leg-asymmetric (LA)                              | 34           |  |  |  |  |

|              |       |                                                        | 35           |  |  |  |  |

|              |       | 3.2.3 Single-switch (BAC, BDC e OS)                    | 37           |  |  |  |  |

|    | 3.3 | Resultados de simulações e experimentais                      | 38         |

|----|-----|---------------------------------------------------------------|------------|

|    | 3.4 | Conclusão                                                     | 44         |

| 4  |     | ificador fonte de corrente monofásico assimétrico multinível  | 47         |

|    | 4.1 | Introdução                                                    | 47         |

|    | 4.2 | Operação e modulação                                          | 48         |

|    |     | 4.2.1 CSC ponte-H monofásico multinível                       | 48         |

|    |     | 4.2.2 CSR ponte-H monofásico multinível assimétrico           | 51         |

|    | 4.3 | Resultados de simulações e experimentais                      | 55         |

|    | 4.4 | Conclusão                                                     | 58         |

| II | Co  | nversores fonte de corrente tipo-X                            | 61         |

| 5  | Con | aversores fonte de corrente tipo-X totalmente controláveis    | 63         |

|    | 5.1 | Introdução                                                    | 63         |

|    | 5.2 | Operação e modulação                                          | 64         |

|    | 5.3 | Dimensionamento dos elementos reativos                        | 69         |

|    |     | 5.3.1 Indutor do barramento CC                                | 70         |

|    |     | 5.3.2 Capacitor do barramento CA                              | 71         |

|    | 5.4 | Estratégias de controle                                       | 71         |

|    |     | 5.4.1 Inversor fonte de corrente                              | 72         |

|    |     | 5.4.1.1 Controle da corrente do barramento CC                 | 72         |

|    |     | 5.4.1.2 Controle do barramento CA                             | 73         |

|    |     | 5.4.2 Retificador fonte de corrente                           | 73         |

|    | 5.5 | Resultados de simulações e experimentais                      | 74         |

|    | 5.6 | Conclusão                                                     | 77         |

| 6  | Con | versor fonte de corrente CA-CC-CA com redução da oscilação do |            |

|    | bar | ramento CC                                                    | <b>7</b> 9 |

|    | 6.1 | Introdução                                                    | 79         |

|    | 6.2 | Operação e modulação                                          | 80         |

|    | 6.3 | Técnica de sincronização                                      | 82         |

|    | 6.4 | Resultados de simulações e experimentais                      | 89         |

|    | 6.5 | Conclusão                                                     | 94         |

| 7  |     | ificadores fonte de corrente tipo-X assimétricos              | 97         |

|    | 7.1 | Introdução                                                    | 97         |

|    | 7.2 | Operação e modulação                                          | 99         |

|    |     | 7.2.1 Retificador tipo-X multifásico                          | 99         |

|    |     | 7.2.2 Tipo-X bifásico assimétrico                             | 104        |

|    |     | 7.2.3 Tipo-X trifásico assimétrico                            | 108        |

|    | 7.3 | Resultados de simulações e experimentais                      | 111        |

|    |     | 7.3.1 Tipo-X bifásico assimétrico                             | 112        |

|              |        | 7.3.2        | Tipo-X trifásico assimétrico                          | 114       |

|--------------|--------|--------------|-------------------------------------------------------|-----------|

|              | 7.4    | Conc         | lusão                                                 | l15       |

| 8            | Cond   | clusã        | o geral                                               | 21        |

|              | 8.1    | Traba        | alhos futuros                                         | 123       |

| Re           | eferên | cias         |                                                       | 25        |

|              |        |              |                                                       |           |

|              |        |              |                                                       |           |

| •            |        |              |                                                       | 00        |

| A            | nexo   | $\mathbf{S}$ | 17                                                    | <b>29</b> |

| $\mathbf{A}$ | NEXC   | ) A          | Protótipo CSC ponte-H monofásico                      | 131       |

| $\mathbf{A}$ | NEXC   | ) В          | Protótipo CSC ponte-H monofásico assimétrico de cinco |           |

|              |        |              | níveis                                                | .33       |

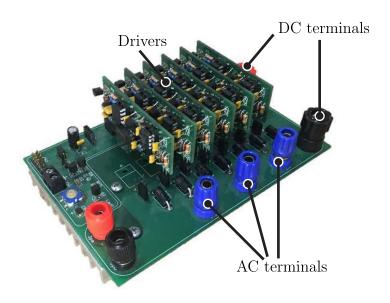

| $\mathbf{A}$ | NEXC   | <b>C</b>     | Protótipo XCSC bifásico                               | .35       |

| $\mathbf{A}$ | NEXC   | D            | Protótipo XCSC trifásico                              | .37       |

# Lista de ilustrações

| Figura 1.1 – Símbolos das chaves utilizadas em CSCs, que necessitam de capacidade       |

|-----------------------------------------------------------------------------------------|

| de bloqueio reverso de corrente                                                         |

| Figura 2.1 – Cenário de aplicação do CSC monofásico como inversor ou retificador.       |

| Figura $2.2$ – Retificador fonte de corrente ponte-H monofásico convencional            |

| Figura 2.3 – Diagrama de blocos PWM do CSC monofásico                                   |

| Figura $2.4$ – Representação simplificada do filtro CA de um retificador fonte de       |

| corrente monofásico convencional                                                        |

| Figura $2.5$ – Comportamento dos ângulos de entrada de um CSR monofásico em             |

| função da potência CA $P_{\text{ca}}$ , para diferentes valores de capacitância $C_f$ . |

| Figura $2.6$ – Diagrama de blocos de controle da corrente do barramento CC dos CSIs     |

| monofásicos                                                                             |

| Figura 2.7 – Diagrama de blocos de controle do CSC monofásico                           |

| Figura $2.8$ – Diagrama de blocos de controle da corrente do barramento CC do CSR       |

| monofásico                                                                              |

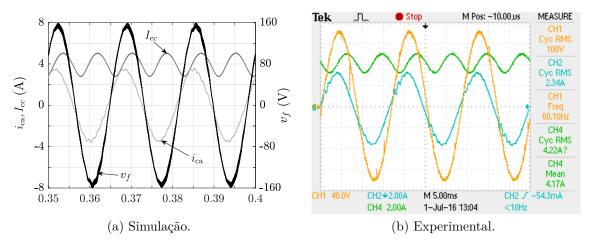

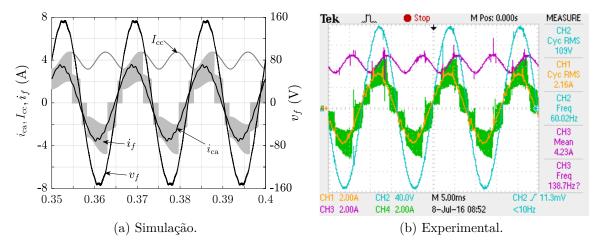

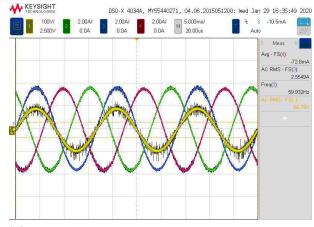

| Figura $2.9$ – Resultado de simulação e experimental do CSC monofásico                  |

| Figura $3.1$ – Cenário de aplicação dos retificadores fonte de corrente monofásicos     |

| assimétricos                                                                            |

| Figura 3.2 – Retificadores fonte de corrente assimétricos monofásicos                   |

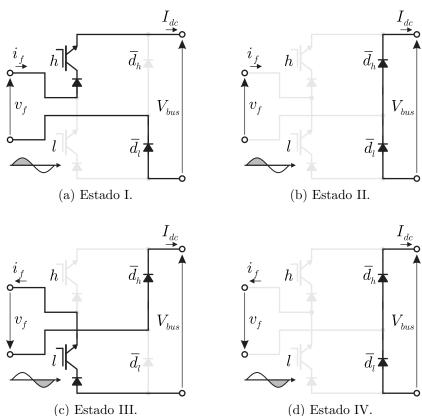

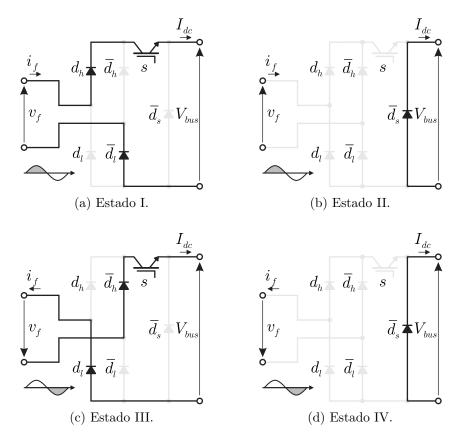

| Figura 3.3 – Estados do LA de acordo com a Tabela 3.1                                   |

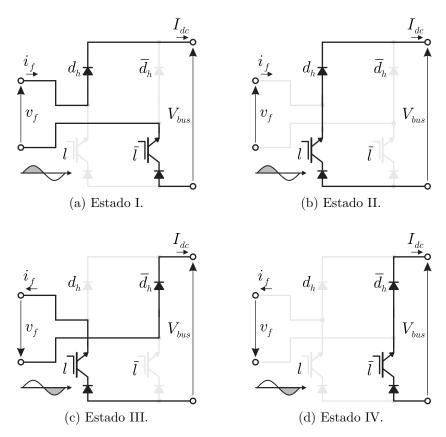

| Figura 3.4 – Estados do NA de acordo com a Tabela 3.1                                   |

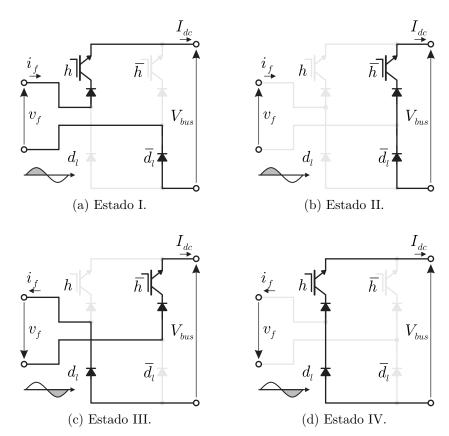

| Figura 3.5 – Estados do PA de acordo com a Tabela 3.1                                   |

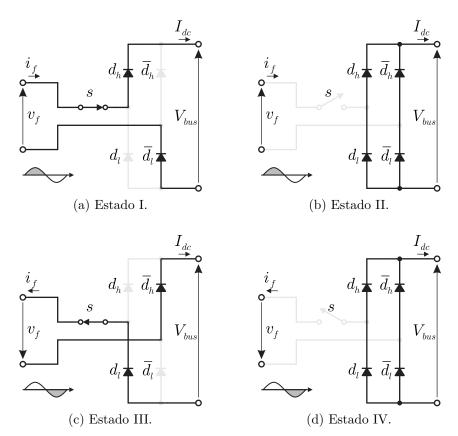

| Figura 3.6 – Estados do BAC de acordo com a Tabela 3.1                                  |

| Figura 3.7 – Estados do BDC de acordo com a Tabela 3.1                                  |

| Figura 3.8 – Estados do OS de acordo com a Tabela 3.1                                   |

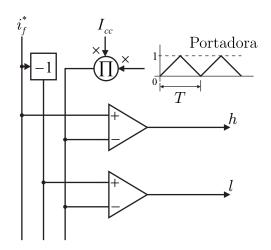

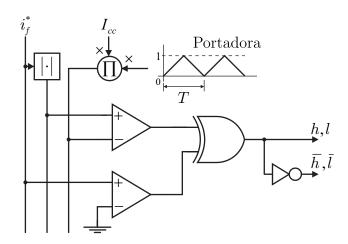

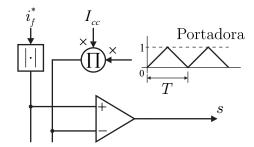

| Figura 3.9 – Diagrama de blocos PWM para o conversor LA                                 |

| Figura 3.10–Diagrama de blocos PWM para os conversores NA e PA                          |

| Figura 3.11–Diagrama de blocos PWM para a família SS                                    |

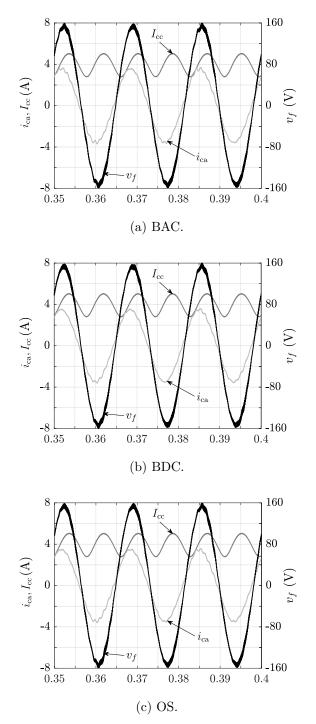

| Figura 3.12–Resultados de simulações da família SS                                      |

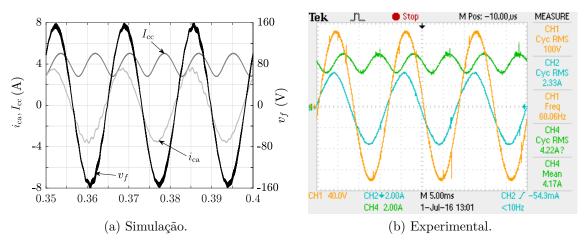

| Figura 3.13–Resultado de simulação e experimental do LA                                 |

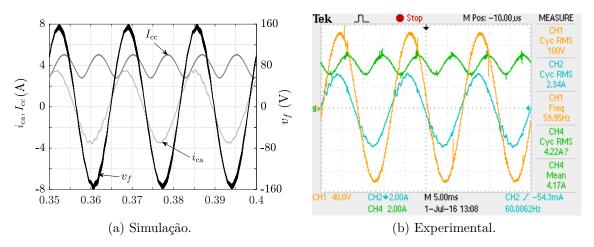

| Figura 3.14–Resultado de simulação e experimental do NA                                 |

| Figura 3.15–Resultado de simulação e experimental do PA                                 |

| Figura 3.16–Gráficos comparativos de simulações da eficiência e THD para a família      |

| DS                                                                                      |

| Figura 3.17–Gráficos comparativos de simulações da eficiência e THD para a família      |

| SS                                                                                      |

| Figura 4.1 – Cenário de aplicação dos CSRs monofásicos de cinco níveis                  |

| Figura 4.2 – Conversor fonte de corrente monofásico multinível convencion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nal 49        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

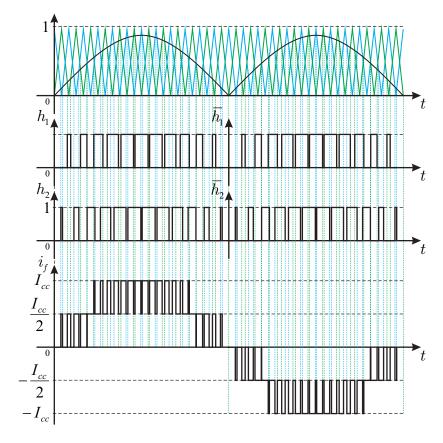

| Figura $4.3-$ Formas de onda do PSPWM, comandos das chaves e a cor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | rrente de     |

| entrada $i_f$ do CSC monofásico de cinco níveis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51            |

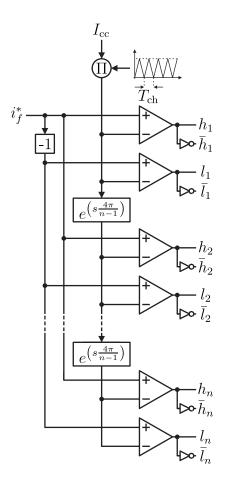

| Figura $4.4$ – Diagrama de blocos PSPWM para o CSC monofásico multiní                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ível 52       |

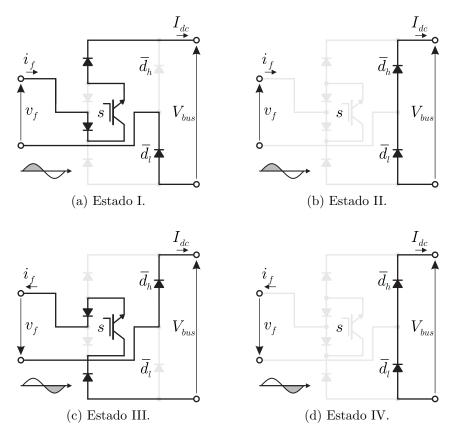

| Figura $4.5$ – Retificador fonte de corrente monofásico multinível assimétric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | eo 53         |

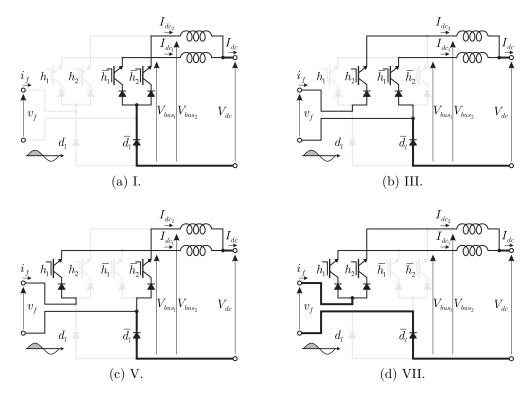

| Figura $4.6$ – Estados do semiciclo positivo CSR monofásico de 5 níveis ass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | simétrico     |

| de acordo com a Tabela 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54            |

| Figura $4.7$ – Diagrama de blocos do PSPWM para o CSR monofásico m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nultinível    |

| assimétrico                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55            |

| Figura $4.8 - {\rm Resultado}$ de simulação e experimental do retificador fonte de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | corrente      |

| monofásico assimétrico de cinco níveis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56            |

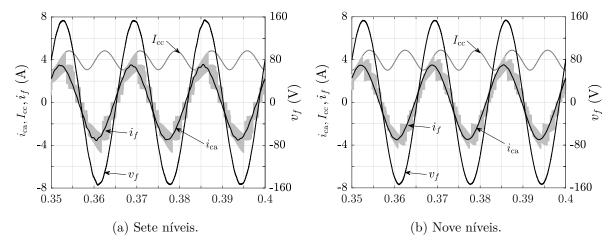

| Figura $4.9$ – Resultado de simulação dos retificadores monofásicos assimétr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | cicos com     |

| 7 e 9 níveis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57            |

| Figura 4.10–Gráficos comparativos de simulações da eficiência e THD ent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | re o con-     |

| versor convencional e o assimétrico                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 58            |

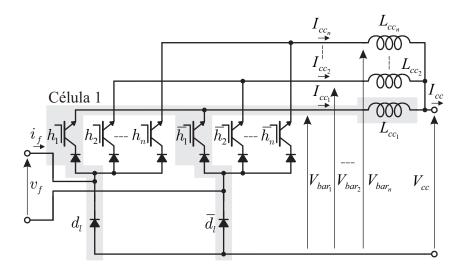

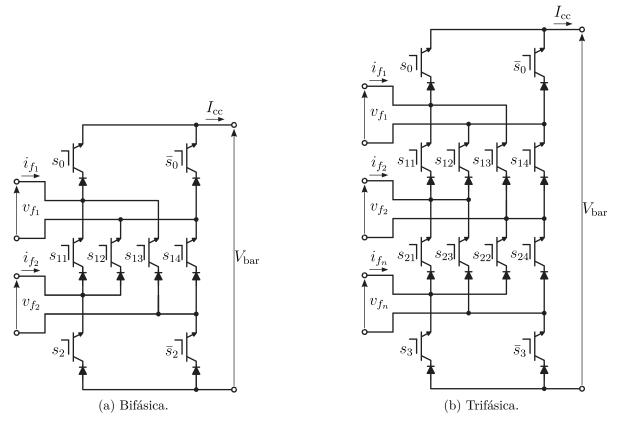

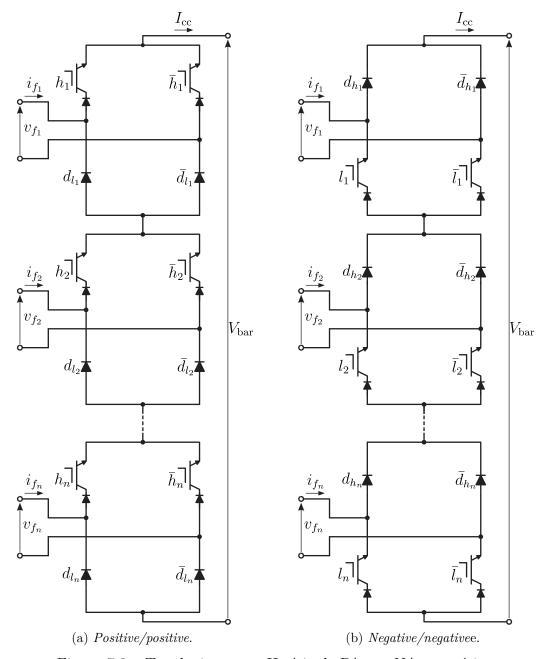

| ${\bf Figura}~5.1-{\bf Conversores~fonte~de~corrente~com~terminais~abertos~multifás:}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | icos 64       |

| Figura $5.2$ – Associação série de CSCs monofásicos e seus sub-estados equ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ivalentes     |

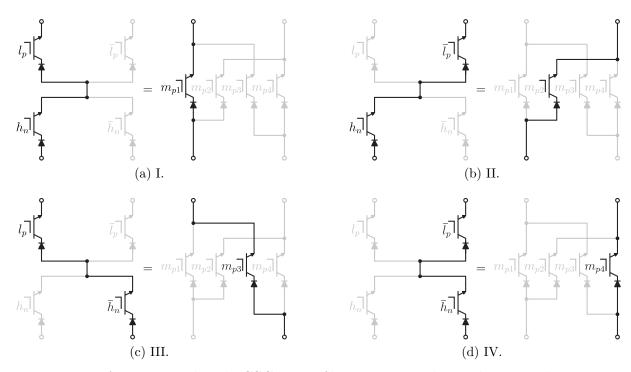

| para os XCSCs, de acordo com a Tabela 5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65            |

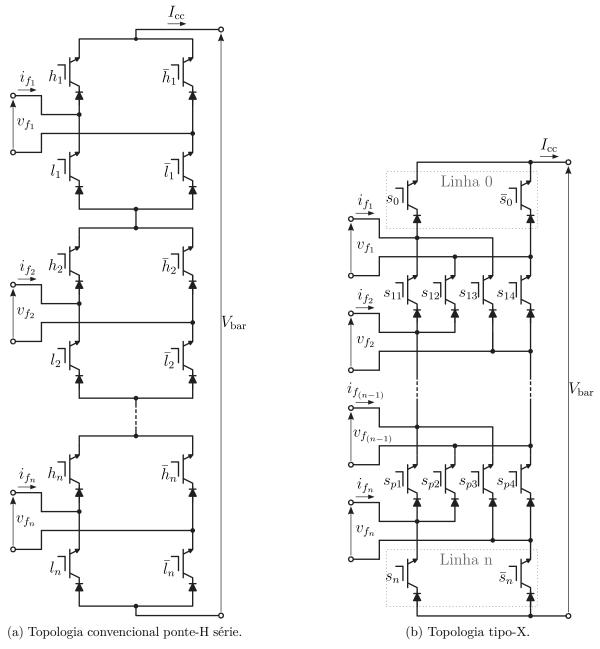

| Figura 5.3 – Topologias tipo-X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66            |

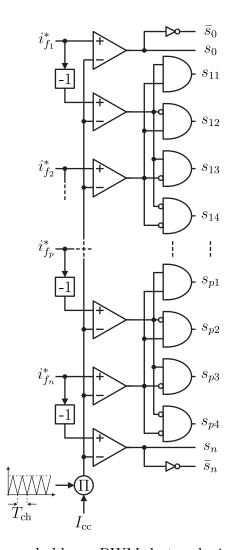

| Figura $5.4$ – Diagrama de blocos PWM da topologia tipo-X multifásica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70            |

| Figura $5.5$ – Redução das perda por condução dos XCSCs, normalizado pelo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ponte-H       |

| em série                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 71            |

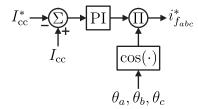

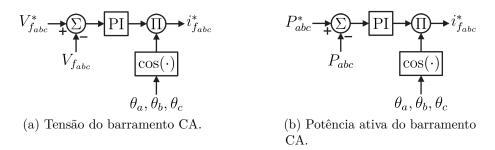

| Figura $5.6$ – Diagrama de blocos de controle da corrente do barramento $\mathrm{CC}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | do XCSI       |

| trifásico                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 72            |

| Figura $5.7$ – Diagrama de blocos de controle do barramento CA do XCSI $^{\circ}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | trifásico. 73 |

| Figura $5.8$ – Diagrama de blocos de controle da corrente do barramento CC $\alpha$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | do XCSR       |

| trifásico                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 74            |

| Figura 5.9 – Cenário de aplicação dos XCSCs multifásicos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74            |

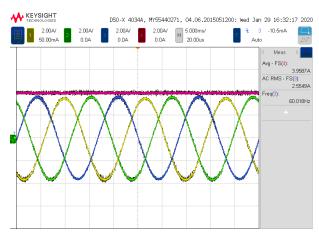

| Figura 5.10–Resultados de simulações dos XCSCs multifásicos, operandos de simulações do se simulações do se simulações do se | do como       |

| retificadores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75            |

| Figura 5.11–Resultados experimentais do XCSC trifásico, operando como                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | inversor. 76  |

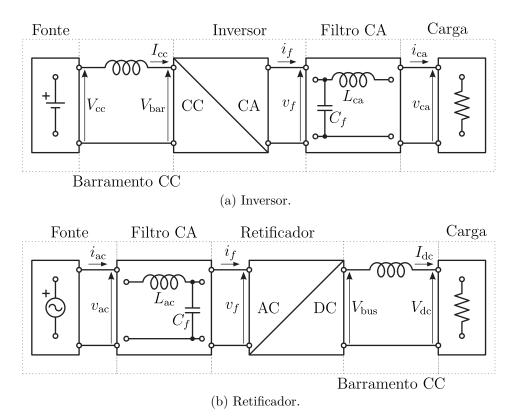

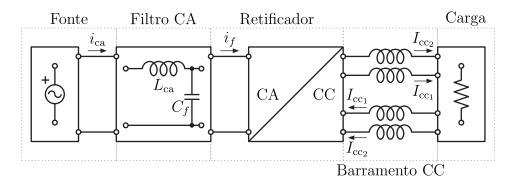

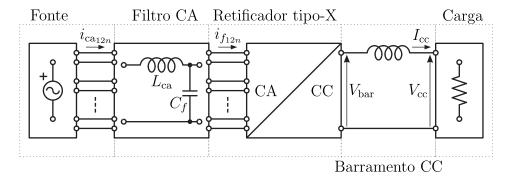

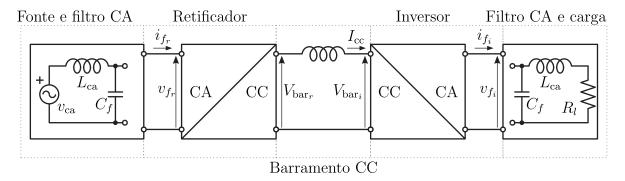

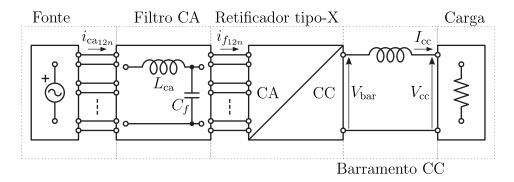

| Figura $6.1$ – Cenário de aplicação do CSC CA-CC-CA monofásico                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80            |

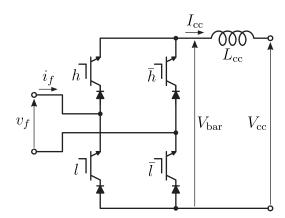

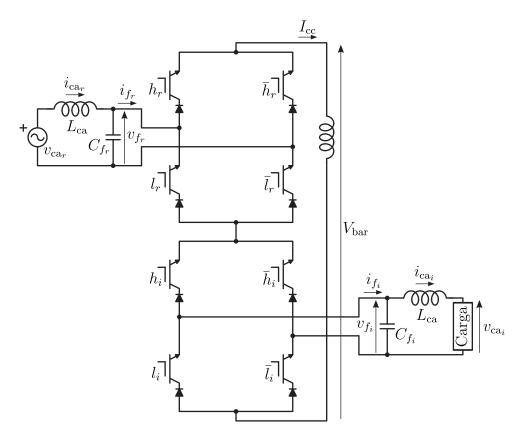

| Figura 6.2 – CSC CA-CC-CA monofásico                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 81            |

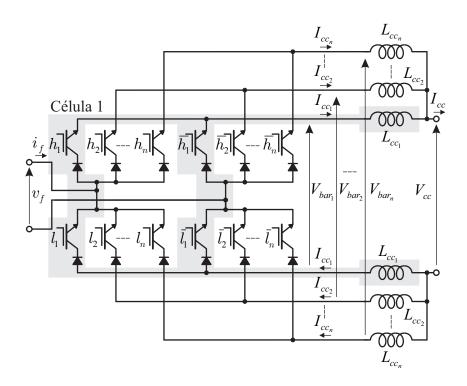

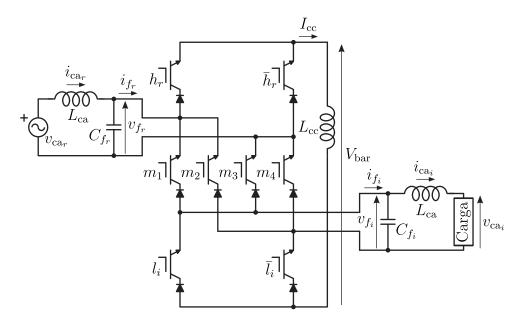

| Figura 6.3 – XCSC CA-CC-CA monofásico                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 82            |

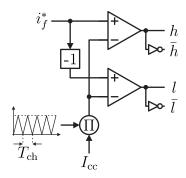

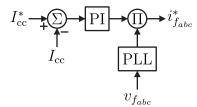

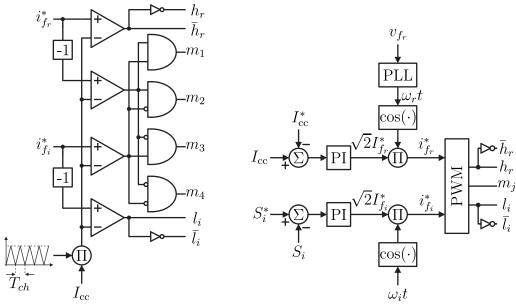

| Figura $6.4$ – Diagrama de blocos PWM e de controle do XCSC CA-CC-CA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | monofá-       |

| sico                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 82            |

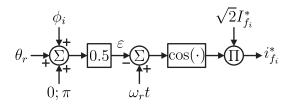

| Figura $6.5$ – Diagrama de blocos do controle de sincronização a ser adicio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | onado ao      |

| controle convencional do CSC CA-CC-CA monofásico                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 88            |

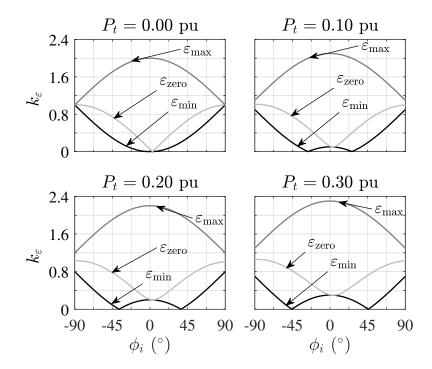

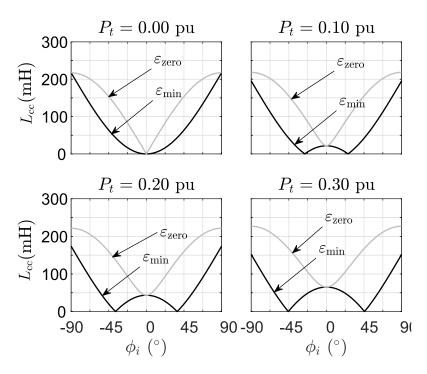

| Figura 6.6 – Variação de $k_{\varepsilon}$ em função do fator de potência da carga $\phi_i$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 88            |

| Figura 6.7 – Resultado teórico da oscilação do barramento CC para $L_{\rm cc}=100$ mH $$ 8      | 39         |

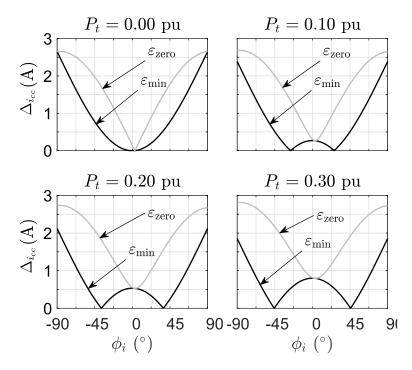

|-------------------------------------------------------------------------------------------------|------------|

| Figura 6.8 – Resultado teórico do indutor do barramento CC para $\Delta i_{ m cc}=1,22$ A 9     | 90         |

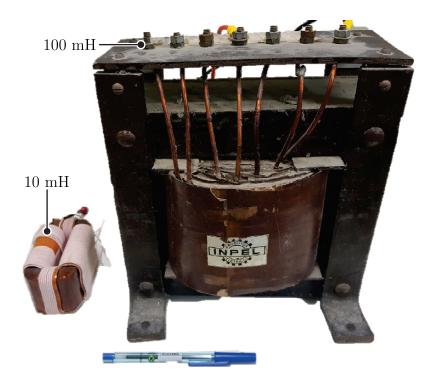

| Figura 6.9 – Análise comparativa do tamanho de dois indutores: 10 mH (à esquerda)               |            |

| e 100 mH (à direita)                                                                            | 91         |

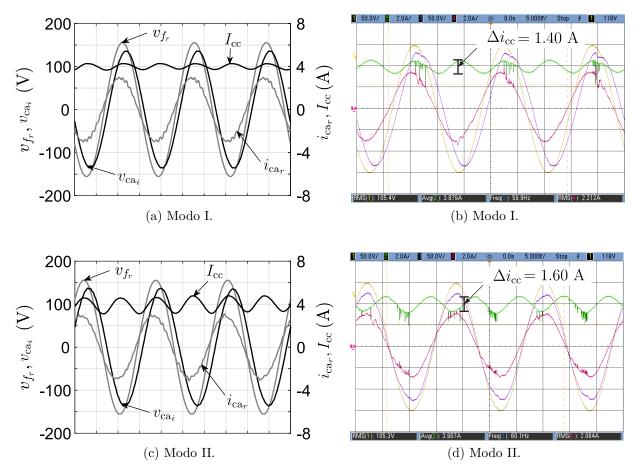

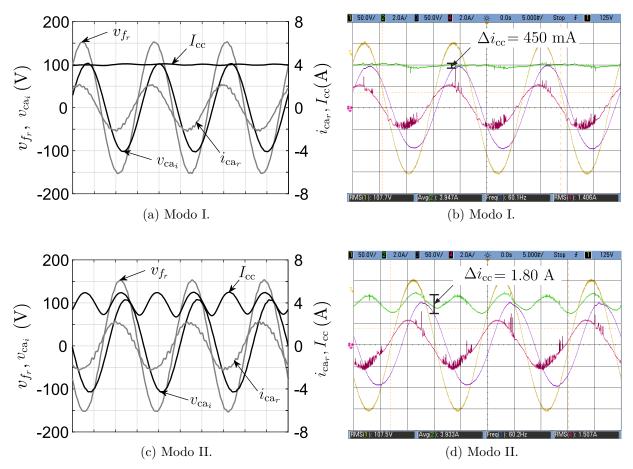

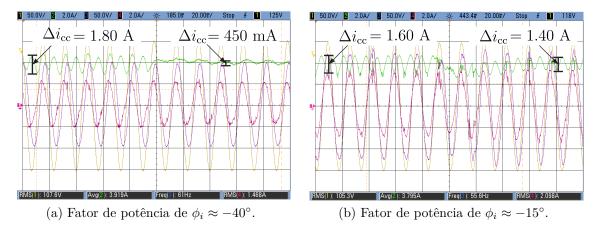

| Figura 6.10–Resultado de simulação e experimental alimentando uma carga indutiva                |            |

| $(\phi_i \approx 15^\circ)$ , com as abscissas como o eixo do tempo                             | 92         |

| Figura 6.11–Resultado de simulação e experimental alimentando uma carga capaci-                 |            |

| tiva $(\phi_i \approx -40^\circ)$ , com as abscissas como o eixo do tempo                       | 93         |

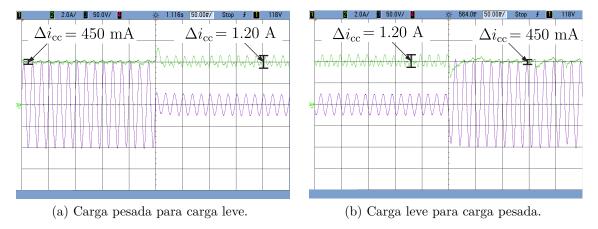

| Figura 6.12–Transitório no controle de fase do Modo II para o Modo I 9                          | )4         |

| Figura 6.13–Transitório entre carga pesada (150 W, $\phi_i \approx -40^{\circ}$ ) e leve (50 W, |            |

| $\phi_i \approx -15^\circ$ )                                                                    | )4         |

| Figura 7.1 – Cenário de aplicação dos XCSRs assimétricos                                        | <b>)</b> 8 |

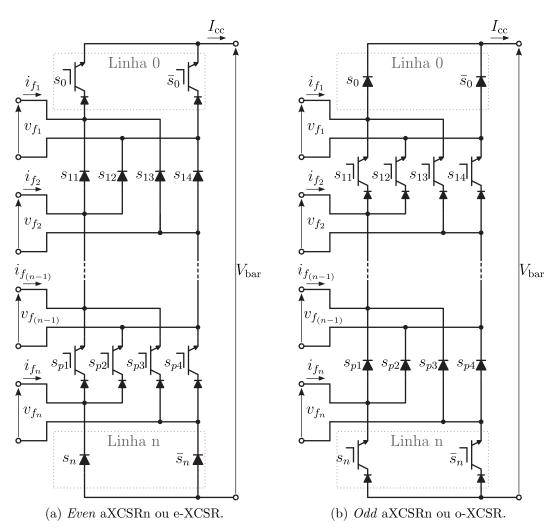

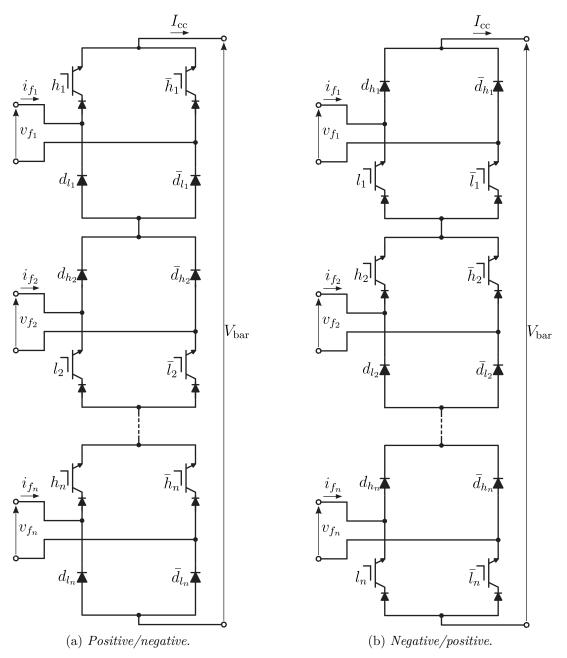

| Figura 7.2 – Topologias XCSRs multifásicas assimétricas.                                        | <b>)</b> 8 |

| Figura 7.3 – Topologias ponte-H série de PAs ou NAs em série                                    | 0(         |

| Figura 7.4 – Topologias ponte-H<br>série de PAs e NAs ou NAs e PAs em série 10                  | )1         |

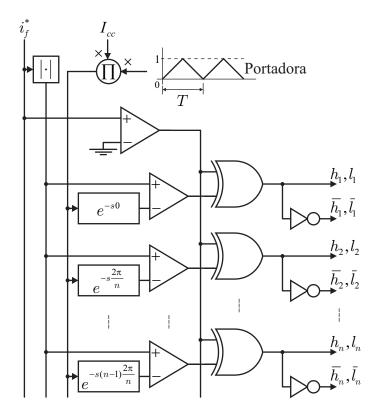

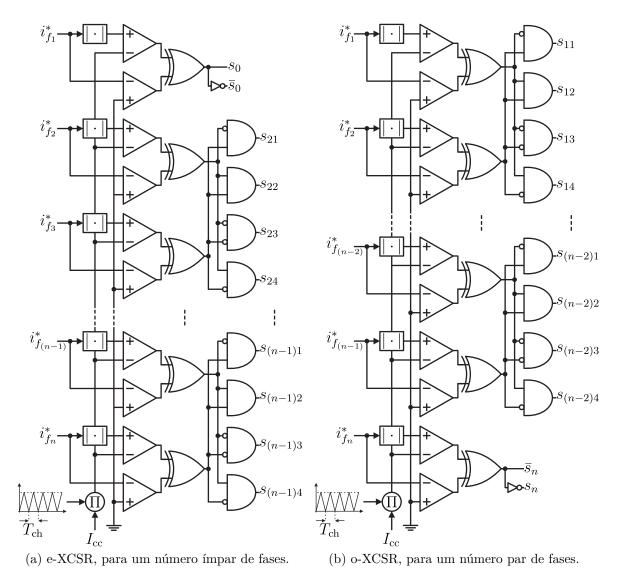

| Figura 7.5 – Diagrama de blocos PWM para os XCSRs assimétricos                                  | )5         |

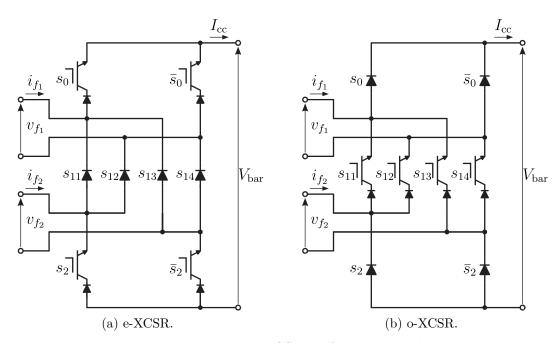

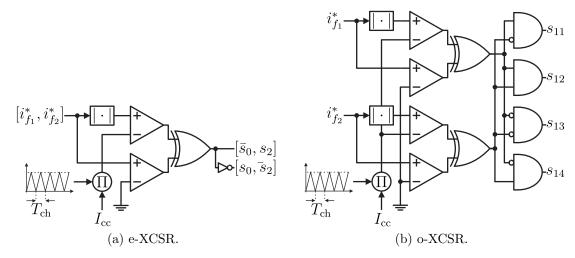

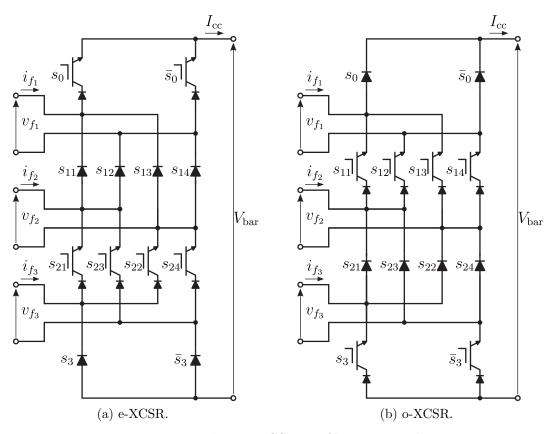

| Figura 7.6 – Topologias XCSRs bifásicas assimétricas                                            | )6         |

| Figura 7.7 – Diagrama de blocos PWM dos XCSRs bifásicos assimétricos 10                         | )7         |

| Figura 7.8 – Topologias XCSRs trifásicas assimétricas                                           | )9         |

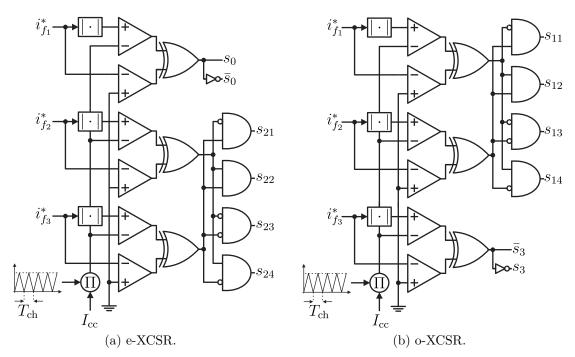

| Figura 7.9 – Diagrama de blocos PWM dos XCSRs trifásicos assimétricos 11                        | 1          |

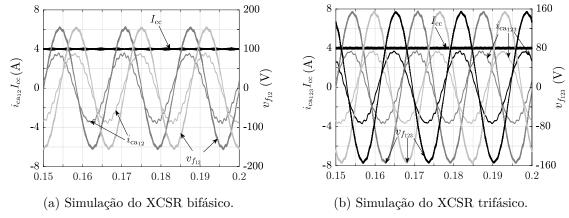

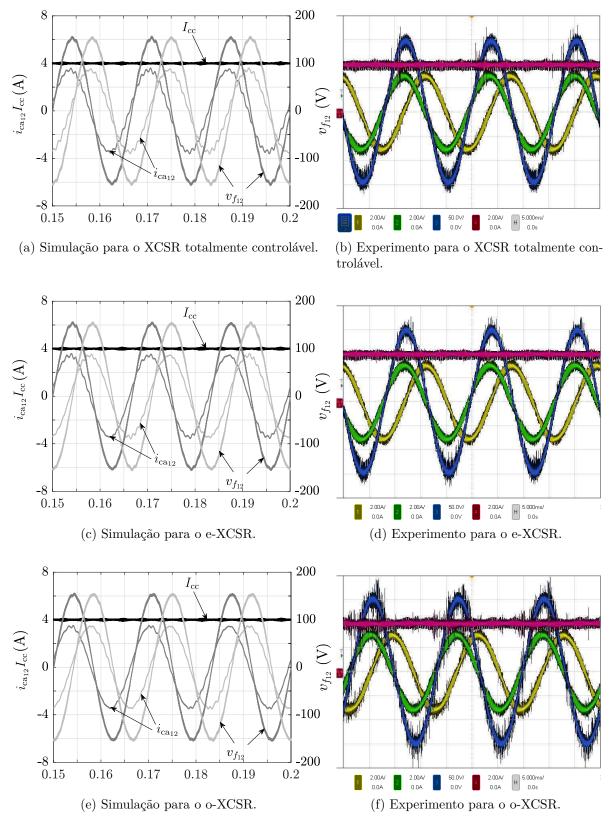

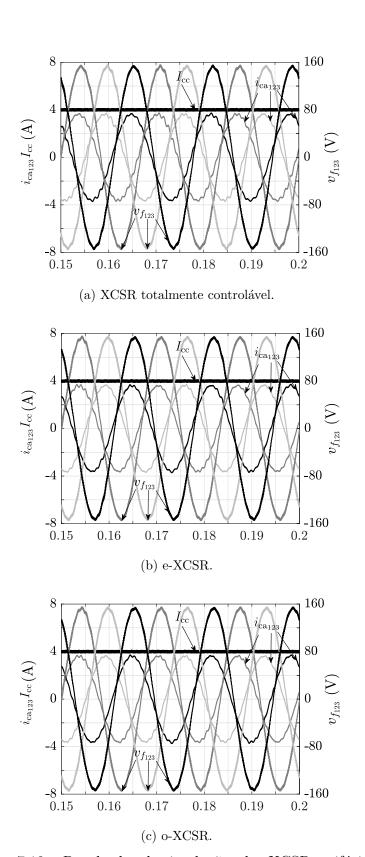

| Figura 7.10–Resultados de simulações e experimentais dos XCSRs bifásicos 11                     | 7          |

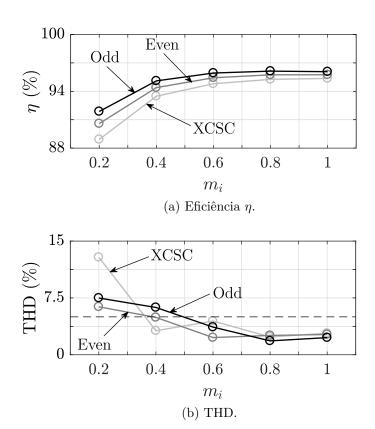

| Figura 7.11–Gráficos comparativos de simulações da eficiência e THD entre os XCSRs              |            |

| bifásicos                                                                                       | .8         |

| Figura 7.12–Resultados de simulações dos XCSRs trifásicos                                       | .9         |

| Figura 7.13–Gráficos comparativos de simulações da eficiência e THD entre os XCSRs              |            |

| trifásicos                                                                                      | 20         |

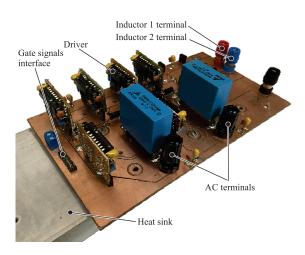

| Figura A.1 – Fotografia do protótipo CSC ponte-H monofásico                                     | 32         |

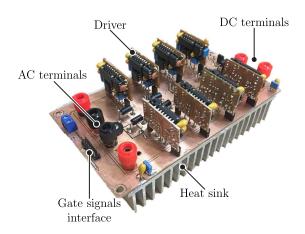

| Figura B.1 – Fotografia do protótipo CSC ponte-H monofásico assimétrico de cinco                |            |

| níveis                                                                                          | 34         |

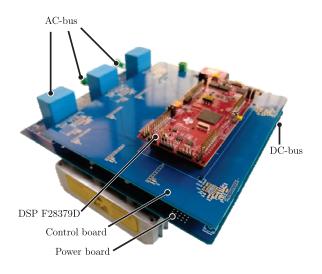

| Figura C.1 – Fotografia do protótipo XCSC bifásico                                              | 36         |

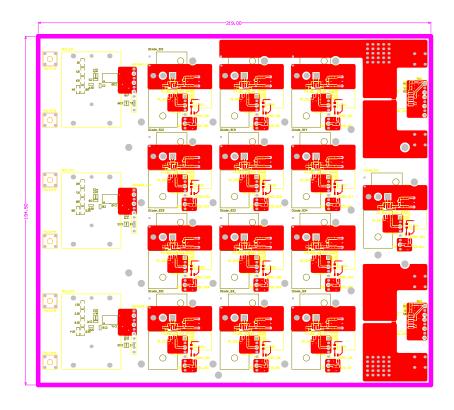

| Figura D.1-Fotografia do protótipo XCSC trifásico                                               | 37         |

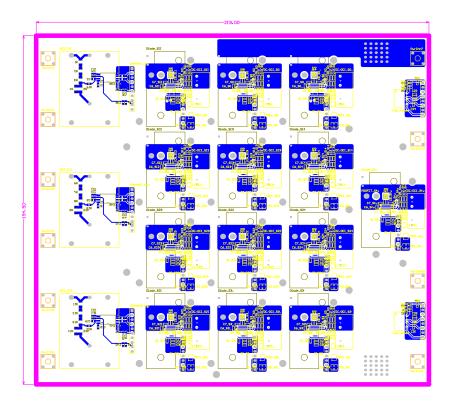

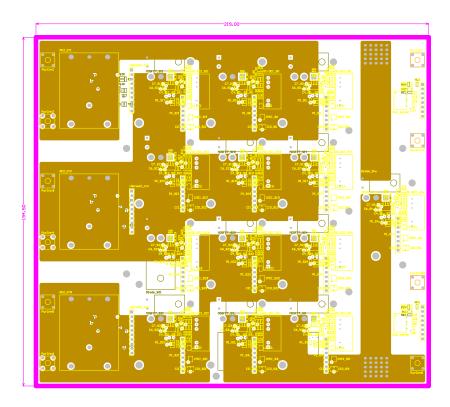

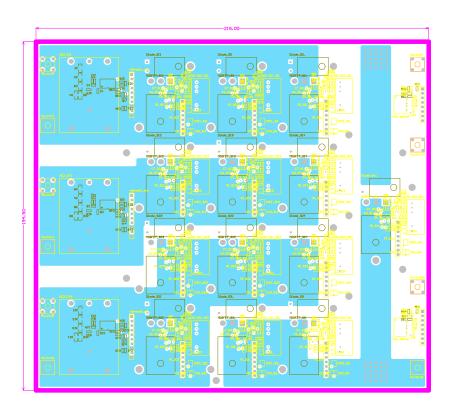

| Figura D.2–Camadas superior e inferior da placa de potência do XCSC trifásico.    . 13          | }9         |

| Figura D.3-Camadas internas da placa de potência do XCSC trifásico                              | 10         |

# Lista de tabelas

| Tabela 2.1 – Estados do CSC monofásico                                                                                         | 17  |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Tabela 2.2 – Parâmetros do cenário de teste do conversor                                                                       | 26  |

| Tabela 3.1 – Estados dos CSR monofásicos assimétricos                                                                          | 33  |

| Tabela 3.2 – Parâmetros do cenário de teste dos conversores                                                                    | 39  |

| Tabela $3.3$ – Comparação do número total de chaves e número de chaves conduzindo                                              | 40  |

| Tabela 3.4 – Dados comparativos de simulações dos CSRs monofásicos assimétricos                                                |     |

| para $m_i = 1 \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                                           | 42  |

| Tabela 3.5 – Dados comparativos de simulações dos CSRs monofásicos assimétricos                                                |     |

| para $m_i = 0, 8 \dots $ | 43  |

| Tabela 3.6 – Dados comparativos de simulações dos CSRs monofásicos assimétricos                                                |     |

| para $m_i = 0.6$                                                                                                               | 43  |

| Tabela 3.7 – Dados comparativos de simulações dos CSRs monofásicos assimétricos                                                |     |

| para $m_i = 0, 4 \dots $ | 44  |

| Tabela 3.8 – Dados comparativos de simulações dos CSRs monofásicos assimétricos                                                |     |

| para $m_i = 0, 2 \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                                  | 44  |

| Tabela $4.1$ – Estados do conversor fonte de corrente monofásico de cinco níveis                                               | 50  |

| Tabela $4.2$ – Estados do CSR monofásico de 5 níveis assimétrico                                                               | 53  |

| Tabela 4.3 – Parâmetros do cenário de teste dos conversores                                                                    | 56  |

| Tabela 4.4 – Dados comparativos de simulações do conversor convencional em função                                              |     |

| de $m_i$                                                                                                                       | 57  |

| Tabela $4.5$ – Dados comparativos de simulações do conversor assimétrico em função                                             |     |

| de $m_i$                                                                                                                       | 58  |

| Tabela 5.1 – Associação série de CSCs monofásicos e seus sub-estados equivalentes                                              |     |

| para os XCSCs                                                                                                                  | 65  |

| Tabela 5.2 – Estados do XCSC bifásico                                                                                          | 68  |

| Tabela 5.3 – Estados I ao XVI do XCSC trifásico                                                                                | 69  |

| Tabela 5.4 – Parâmetros do cenário de teste dos conversores                                                                    | 75  |

| Tabela 6.1 – Parâmetros do cenário de teste do conversor                                                                       | 90  |

| Tabela 7.1 – Diodo a conduzir em função das polaridades das tensões de entrada dos                                             |     |

| XCSRs assimétricos bifásicos                                                                                                   | 107 |

| Tabela 7.2 – Estados dos XCSRs bifásicos assimétricos                                                                          | 108 |

| Tabela 7.3 – Diodo a conduzir em função das polaridades das tensões de entrada dos                                             |     |

| XCSRs trifásicos assimétricos                                                                                                  | 110 |

| Tabela 7.4 – Parâmetros do cenário de teste dos conversores                                                                    | 112 |

| Tabela 7.5 – Dados comparativos de simulações dos XCSRs bifásicos para $m_i=1$ .                                               | 112 |

| Tabela 7.6 – Dados comparativos de simulações dos XCSRs bifásicos para $m_i = 0, 8$                                            | 113 |

Tabela 7.7 – Dados comparativos de simulações dos XCSRs bifásicos para  $m_i=0,6$  113 Tabela 7.8 – Dados comparativos de simulações dos XCSRs bifásicos para  $m_i=0,4$  113 Tabela 7.9 – Dados comparativos de simulações dos XCSRs bifásicos para  $m_i=0,2$  114 Tabela 7.10–Dados comparativos de simulações dos XCSRs trifásicos para  $m_i=1$  . 114 Tabela 7.11–Dados comparativos de simulações dos XCSRs trifásicos para  $m_i=0,8$  114 Tabela 7.12–Dados comparativos de simulações dos XCSRs trifásicos para  $m_i=0,6$  115 Tabela 7.13–Dados comparativos de simulações dos XCSRs trifásicos para  $m_i=0,4$  115 Tabela 7.14–Dados comparativos de simulações dos XCSRs trifásicos para  $m_i=0,4$  115 Tabela 7.14–Dados comparativos de simulações dos XCSRs trifásicos para  $m_i=0,2$  115

# Lista de abreviaturas e siglas

CA Corrente alternada.

CC Corrente contínua.

CEEI Centro de Engenharia Elétrica e Informática.

CSI Current source inverter (Inversor fonte de corrente).

CSC Current source converter (Conversor fonte de corrente).

CSR Current source rectifier (Retificador fonte de corrente).

DEE Departamento de Engenharia Elétrica.

GaN Gallium nitrate ou nitrato de gálio.

IGBT Insulated-gate bipolar transistor.

LEIAM Laboratório de Eletrônica Industrial e Acionamento de Máquinas.

MOSFET Metal oxide semiconductor field effect transistor.

PFC Power factor correction.

PLL phase-locked loop.

PMSG permanent magnet synchronous generator.

PWM pulse-width modulation (modulação por largura de pulso).

RBIGBT Reverse-blocking IGBT.

SiC Silicon carbide ou carbeto de silício.

SVM Space vector modulation.

THD Total harmonic distortion.

UFCG Universidade Federal de Campina Grande.

UPS Uninterruptible power supply (fonte de alimentação ininterrupta).

VR Voltage regulator (regulador de tensão).

VSI Voltage source inverter (inversor fonte de tensão).

VSC Voltage source converter (conversor fonte de tensão).

VSR Voltage source rectifier (retificador fonte de tensão).

## Lista de símbolos

$\varepsilon$  Ângulo da corrente da carga de um conversor CA-CC-CA monofásico.

$\omega_{\rm ca}$  Frequência angular de um barramento CA.

$C_{\rm cc}$  Capacitância de um barramento CC.

$C_f$  Capacitância de um filtro CA.

$f_{\rm ca}$  Frequência de um barramento CA.

$f_{\rm ch}$  Frequência de chaveamento de um PWM ou SVM.

$i_{ca}(t)$  Corrente de uma fonte CA.

$i_{cc}(t)$  Corrente de um barramento CC.

$i_f(t)$  Corrente de um filtro CA.

$L_{\rm ca}$  Indutância de um barramento CA.

$L_{\rm cc}$  Indutância de um barramento CC.

$L_f$  Indutância de um filtro CA.

$m_i$  Índice de modulação de corrente.

$m_v$  Índice de modulação de tensão.

$P_{abc}$  Potência de um conversor trifásico.

$P_{\rm ca}$  Potência de um barramento CA.

$P_{\rm cc}$  Potência de um barramento CC.

$P_l$  Potência de uma carga monofásica.

$T_{\rm ch}$  Período de chaveamento de um PWM ou SVM.

$v_{\rm ca}(t)$  Tensão de de uma fonte CA.

- $v_{\rm cc}(t)$  Tensão de um barramento CC.

- $v_f(t)$  Tensão de um filtro CA.

# 1

# Introdução geral

#### 1.1 Conversores fonte de corrente

Os conversores CA-CC e/ou CC-CA são denominados de acordo com o elemento reativo de seu barramento CC, logo, os conversores fonte de corrente (current source converters - CSCs) apresentam indutores, os conversores fonte de tensão (voltage source converters - VSCs) apresentam capacitores e os conversores fonte de impedância (z-source converters - ZSCs) apresentam um conjunto de indutores e capacitores. Especificamente para os conversores fonte de corrente, sua configuração apresenta algumas desvantagens.

O indutor do barramento CC é o elemento principal dos CSCs, o que resulta em alguns problemas quando comparados aos capacitores dos conversores fonte de tensão. De modo geral, os CSCs são menos densos que os VSCs quando comparados nas mesmas especificações de potência e frequência de operação [1]. Não só a densidade de potência é menor como também apresentam maiores perdas por condução: a medida que se aumenta a potência, aumenta-se a indutância e o tamanho do indutor (construtivamente falando, em termos de dimensões e volume), essa taxa de crescimento, por sua vez, é maior do que a taxa de crescimento dos capacitores utilizados nos VSCs, por exemplo. Logo, a medida que se aumenta a potência processada por um CSC, sua densidade de potência e eficiência diminuem numa taxa superior ao de um VSC [2].

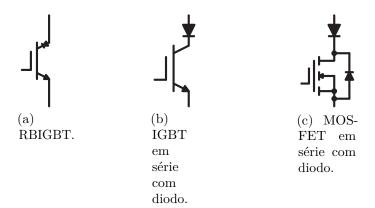

Outro ponto negativo dos CSCs são as suas chaves semicondutoras. Os CSCs precisam de chaves unidirecionais em corrente, função que as chaves semicondutoras convencionais (IGBTs e MOSFETs) não possuem. De modo a se obter a capacidade de bloqueio reverso de corrente, conecta-se um diodo em série com a chave. A junção série do diodo com um IGBT ou MOSFET concede a capacidade de bloqueio reverso de corrente necessária para os CSCs, e quando essa associação é encapsulada em um único componente

Figura 1.1 – Símbolos das chaves utilizadas em CSCs, que necessitam de capacidade de bloqueio reverso de corrente.

resulta em um reverse blocking IGBT (RBIGBT). Nas ilustrações, de forma geral, utiliza-se a representação IGBT + diodo, mas em alguns experimentos utilizou-se, na verdade, a combinação MOSFET + diodo. Os símbolos de cada solução são mostrados na Figura 1.1.

Além disso, vale notar que, em casos de surto de corrente do lado da carga, eventualmente, a corrente pode apresentar um fluxo de potência reverso: do carga/rede para o conversor fonte de corrente. Numa ocasião dessas, por possuir um indutor no barramento CC, os conversores fonte de corrente tornam-se susceptíveis a falhas nesses casos. Nos conversores de tensão, por sua vez, o capacitor do barramento CC absorveria essa energia sem problemas, protegendo os semicondutores do conversor.

Então observa-se que, de fato, os CSCs apresentam algumas desvantagens que os tornariam pouco atrativos, ainda mais quando se busca obter o máximo de eficiência em todas as etapas de conversão de energia. Mesmo que na teoria um CSC pudesse ser uma solução melhor que um VSC com menor complexidade e menor custo (em casos de conversores de estágio único), ao se analisar um cenário prático, a eficiência e densidade de potência dos CSC acaba os tornando inferiores aos VSCs. Porém, o desenvolvimento de novas chaves semicondutoras e algumas características intrínsecas dos CSCs vem mudando esse cenário.

O desenvolvimento de chaves semicondutoras com capacidade de bloqueio reverso de alta eficiência e de alta frequência permite que, mesmo com a associação série de chaves e diodos, obtenha-se níveis de perdas competitivos [3, 4]. Operar em frequências maiores é um ponto de operação favorável aos CSCs, visto que suas perdas por chaveamento são menores que as perdas de chaveamento nos VSCs [5]. Além disso, o aumento da frequência de operação dos CSCs permite trabalhar com indutores e capacitores cada vez menores, um avanço também observado nos VSCs. Essas novas soluções em termos construtivos, ao operar em alta frequência, pode-se considerar utilizar os CSCs no lugar dos VSCs em algumas aplicações. Mas ainda talvez não seria o suficiente utilizar um CSC em algo cujo

um VSC já é consolidado. Entram então as características intrínsecas dos CSCs, que os tornam superior aos VSCs em algumas aplicações.

Os VSCs são, devido sua modulação, inversores abaixadores ou retificadores elevadores, ou seja, o barramento CC tem sempre uma tensão maior ou igual à tensão do barramento CA. Os conversores fonte de corrente apresentarão a relação contrária: a tensão do barramento CC sempre será menor ou igual que a tensão do barramento CA. Por sua vez, a corrente do barramento CC dos CSCs sempre será maior ou igual à corrente do barramento CA. Isso pode ser uma grande vantagem em aplicações cuja tensão do barramento CC é menor que a do barramento CA, por exemplo retificadores carregadores de baterias [6] ou inversores para geração distribuída (células de hidrogênio [7] ou fotovoltaico [8, 9]).

Em aplicações cuja tensão do barramento CC é menor que a do barramento CA, normalmente, utiliza-se um VSC associado a um conversor CC-CC, para abaixar ou elevar a tensão ao nível da carga ou da fonte. Essa associação de um conversor CC-CC com um CC-CA ou CA-CC é uma configuração de dois estágios, que resultará em maiores perdas, maiores custos e menor densidade de potência. Daí, ao se utilizar um CSC, pode-se operar o mesmo sistema mas com apenas um conversor, resultando em um conversor de estágio único [7]. Isso reduz custos, perdas e a complexidade do sistema.

Outro ponto que se destaca é a durabilidade dos indutores quando comparados aos capacitores dos VSCs. Os indutores são mais confiáveis que os capacitores, sendo resistentes em uma faixa de temperatura maior e menos propensos a falhas. Apesar da densidade de potência inferior, o ganho em confiabilidade pode compensar a redução da densidade de potência do conversor [10].

Além disso, os CSCs apresentam uma proteção natural ao curto-circuito. Caso um braço de um CSC venha a queimar, ou caso se forme um curto entre os terminais do barramento CC, no caso dos VSCs o capacitor do barramento CC entraria em curto e pararia de funcionar. A queima do capacitor poderia, inclusive, danificar outros elementos do próprio conversor durante o momento de falha. No caso dos CSCs, caso aconteça um curto em um dos braços do conversor, o conversor irá parar de funcionar, mas a corrente do barramento CC irá fluir pelo circuito formado pelo indutor, braço curto-circuitado e carga ou fonte de alimentação. Deve haver um circuito de proteção, pois esta seria uma condição atípica de operação, mas o barramento CC não queimaria de imediato como ocorre nos VSCs. Todavia, circuitos de proteção podem ser adicionados aos VSCs para evitar esse tipo de problema, mas os VSCs não possuem esse tipo de proteção intrínseca. Porém, valor notar que nos CSCs não pode haver abertura do circuito, uma vez que seria uma interrupção abruta na corrente do indutor, causando picos de tensão.

Por fim avalia-se também a grande quantidade de cargas indutivas presentes nos mais diversos sistemas de eletrônica de potência atualmente. Pode-se argumentar que uma

carga indutiva sendo alimentada por uma fonte de corrente não é recomendado, visto que o chaveamento da corrente em alta frequência causaria picos de tensão que danificariam a carga e/ou fonte de alimentação. Mas a conexão de uma carga indutiva com uma fonte indutiva pode ser desacoplada por um capacitor no barramento CA. Esse capacitor será responsável por filtrar as harmônicas de alta frequência presentes em conversores CC-CA ou CA-CC chaveados. Ao se, obrigatoriamente, adicionar um capacitor no filtro CA, melhora-se substancialmente a qualidade da corrente presente na carga ou na fonte de alimentação. Tal solução é mais custosa, de fato, se comparado a um VSC que pode ser conectado diretamente a cargas indutivas, mas ao se utilizar a indutância da carga ou a indutância interna da fonte como filtro, a corrente circulando por esses elementos será de baixa qualidade. Por outro lado, para se garantir uma boa corrente circulando pelo barramento CA nos VSCs, faz-se necessário a utilização de um filtro LCL, esse sim mais custoso que um simples capacitor.

Percebe-se então que os CSCs ainda possuem muitos desafios a serem vencidos, mas apresentam diversas vantagens, a depender da aplicação em que estão sendo estudados, que podem e devem ser exploradas. O principal ponto negativo dos CSCs vem sendo atenuado com a crescente melhoria das chaves semicondutoras, principalmente as de alta frequência como Sic e GaN unidirecionais e dispositivos GaN bidirecionais. Aliando isso às vantagens intrínsecas dos CSCs, encontram-se aplicações em que esta família de conversores apresentará resultados melhores que as soluções convencionais [7, 11, 10].

Visando contribuir com um campo tão rico mas pouco explorado, este trabalho debruça-se sobre os CSCs desenvolvendo novas topologias que, objetiva-se, apresentem resultados tão bons quanto as topologias CSCs clássicas. Outra alternativa seria buscar aprimorar as topologias já existentes, mas este trabalho busca contribuir com novas topologias que contornem os principais aspectos negativos dos CSCs. Muito do desenvolvimento dos CSCs atualmente vem de soluções consolidadas para VSCs, mas agora aplicadas a CSCs. Tal adaptação é conhecida como princípio da dualidade. Partindo deste princípio, diversos pesquisadores estudam o desenvolvimento de técnicas comumente utilizadas em VSCs aplicadas aos CSCs.

Neste sentido, este trabalho parte de topologias convencionais de CSCs e estuda estratégias e técnicas já consolidadas para os VSCs aplicadas aos CSCs. Objetiva-se desenvolver novas topologias que tornem os CSCs cada vez mais competitivos, de modo que, em um dado momento, faça-se a ponderação entre um CSC e um VSC para determinada aplicação sem que os CSCs se apresentem, sem questionamento, inferiores.

1.2. Objetivos 5

## 1.2 Objetivos

Este trabalho objetiva um aprofundamento no estudo de conversores fonte de corrente monofásicos, bifásicos e trifásicos, com algumas generalizações para sistemas multifásicos. O trabalho é dividido em duas partes: Parte I - Conversores fonte de corrente ponte-H monofásicos; e Parte II - Conversores fonte de corrente tipo-X.

O objetivo principal é desenvolver novas topologias de conversores fonte de corrente que aumentem a sua eficiência e densidade de potência. Como as novas topologias consistem de novas configurações de dispositivos semicondutores, novas estratégias de modulações são necessárias. Todas as topologias e suas respectivas estratégias de modulação são deduzidas e validadas.

As modificações a serem feitas em topologias convencionais são apresentadas em três tipos de abordagens: substituição de chaves ativas por passivas; eliminação de chaves; e recombinação de chaves. Vale notar que todas essas abordagens devem garantir que o conversor opere normalmente com resultados minimamente semelhantes aos da topologia original (em termos de eficiência e distorção harmônica total), e que suas novas limitações se encaixem em cenários de aplicação factíveis.

A substituição ou eliminação de chaves ativas visa reduzir o custo, visto que a não utilização de chaves ativas implica em utilizar chaves passivas (mais baratas) e dispensam drivers, e reduzir perdas, visto que um diodo é mais eficiente que um IGBT ou RBIGBT com as mesmas especificações de projeto. Em alguns casos há também a eliminação de elementos reativos em conversores multiníveis, reduzindo os custos e perdas.

Já a recombinação de chaves consiste em utilizar o mesmo número de chaves (ativas ou passivas) mas com uma associação que reduza o número de chaves conduzindo por ciclo de chaveamento, logo, reduzindo as perdas por condução.

As modificações de controle, especificamente, partem de soluções consolidadas para conversores fonte de tensão e as adapta para os conversores fonte de corrente. Mais especificamente, tal abordagem é feita em CSCs CA-CC-CA monofásicos. Já as modificações de modulação/chaveamento em alguns casos são necessárias devido à nova configuração da topologia.

Vale lembrar que outros avanços relativos aos CSCs não são estudados neste trabalho mas apenas referenciados, como o desenvolvimento de novos materiais magnéticos e dispositivos semicondutores. Enquanto que esses avanços são de impacto positivo para os CSCs, este trabalho foca somente no desenvolvimento de novas topologias para essa família de conversores.

#### 1.3 Justificativas

O processamento da energia elétrica está praticamente em todos os meios onde se encontra energia elétrica, que por sua vez é quase unânime na sociedade moderna. A função de garantir que as diversas fontes de potência e as diversas cargas trabalhem em cooperação, cabe a eletrônica de potência. Logo os conversores de potência são equipamentos também de fundamental importância no mundo moderno. Daí ao se desenvolver um estudo avançado sobre os conversores fonte de corrente, visa-se contribuir com o crescimento dessa área de pesquisa, hoje em uma posição coadjuvante, mas de grande potencial pouco explorado.

Apesar de pouco estudados quando comparados aos VSCs, os conversores fonte de corrente apresentam algumas características que os colocariam em vantagem se comparados aos VSCs e ZSCs. Todavia alguns aspectos, do ponto de vista do desenvolvimento de materiais e chaves semicondutoras, ainda os mantém em desvantagem na indústria. Os CSCs apresentam alguma relevância em altas potências utilizando tiristores, mas são pouco utilizados em baixas e médias potências. Apesar da viabilidade de CSCs com modulação em alta frequência, pouco se investiga essa família dado a praticidade e consolidação dos VSCs.

Então busca-se o desenvolvimento de novos conversores desta família de modo a expandir o leque de topologias fonte de corrente. O potencial inexplorado dos fonte de corrente se mostra um campo de pesquisa fértil capaz de produzir resultados relevantes para a eletrônica de potência como um todo.

Sendo assim, a investigação dos CSCs para baixas e medias potências demonstra-se promissora. Busca-se explorar um campo relativamente pouco explorado, cujo investimento em pesquisas vem mudando recentemente, com novas topologias e soluções de CSCs aplicados a situações específicas surgindo a cada ano.

## 1.4 Contribuições do trabalho

O trabalho desenvolvido tem como principal contribuição o avanço do estudos de conversores fonte de corrente. Tal família de conversores atualmente é mais utilizada em sistemas de alta potência e pouco explorada em sistemas de baixa e média potencia. A investigação de soluções de engenharia de eletrônica de potência mostram que há um campo muito rico a ser explorado, aliando o desenvolvimento de novos conversores com os recentes avanços no desenvolvimento de chaves (IGBTs, MOSFETs, RBIGBTs e diodos) e indutores. Com exceção da topologia ponte-H monofásica, todas as outras topologias são propostas pelo autor deste trabalho e os orientadores da tese.

A pesquisa apresentada neste trabalho na Parte I produziu os artigos científicos

[12, 13]. Já a Parte II produziu os artigos científico [14, 15, 16, 17].

#### 1.5 Revisão bibliográfica

Apesar de serem assuntos correlatos e de certa forma subsequentes, divide-se o trabalho em duas partes. A Parte I aborda os CSCs ponte-H monofásicos e a Parte II aborda os CSCs tipo-X. Daí a revisão bibliográfica ser também dividida em duas partes.

#### Parte I - Conversores fonte de corrente ponte-H monofásicos

São estudadas duas aplicações com CSCs monofásicos: retificadores assimétricos com três níveis e multiníveis. Os retificadores assimétricos visam especificamente o aumento da eficiência das topologias em que eles são baseados.

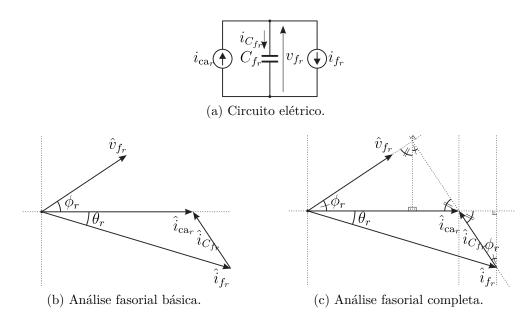

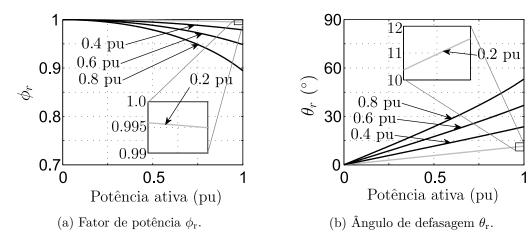

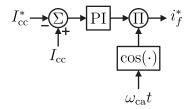

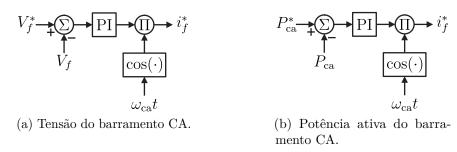

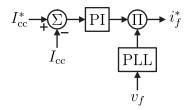

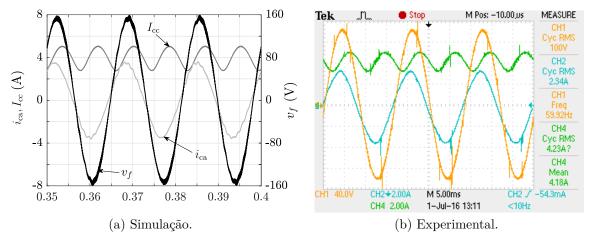

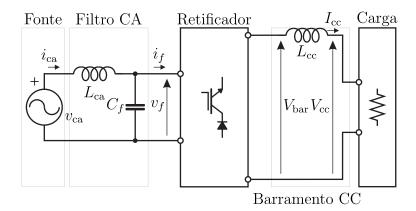

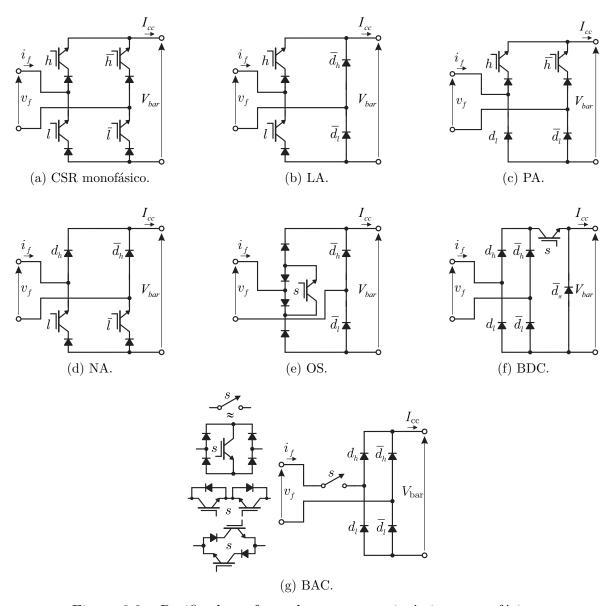

Apesar de existirem topologias totalmente controláveis (bidirecionais) compostas de chaves ativas (IGBTs, MOSFETs, RBIGBTs), em algumas aplicações os conversores operam exclusivamente como retificadores. Tal situação é observada no carregamento de baterias de veículos elétricos, alimentação de computadores, servidores, etc. [18]. Quando se sabe que o uso de um conversor será exclusivamente como retificador, pode-se adotar uma topologia unidirecional sem prejuízo ao sistema em que o conversor esteja inserido.