#### UNIVERSIDADE FEDERAL DE CAMPINA GRANDE

Centro de Engenharia Elétrica e Informática Programa de Pós-Graduação em Engenharia Elétrica

# Contribuições para Algoritmos de Sincronização de Conversores Estáticos Conectados à Rede Elétrica

Nicolau Kellyano Leite Dantas

Campina Grande, Brasil 25 de setembro de 2018

# Contribuições para Algoritmos de Sincronização de Conversores Estáticos Conectados à Rede Elétrica

#### Nicolau Kellyano Leite Dantas

Dissertação de Mestrado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Campina Grande como parte dos requisitos necessários para obtenção do grau de Mestre em Engenharia Elétrica.

Área de Concentração: Processamento da Energia

Maurício B. R. Correa Antonio M. N. Lima Orientadores

Campina Grande, Brasil 25 de setembro de 2018 D192c Dantas, Nicolau Kellyano Leite.

Contribuições para algoritmos de sincronização de conversores estáticos conectados à rede elétrica / Nicolau Kellyano Leite Dantas. — Campina Grande, 2018.

89 f.: il. color.

Dissertação (Mestrado em Engenharia Elétrica) — Universidade Federal de Campina Grande, Centro de Engenharia Elétrica e Informática, 2018.

"Orientação: Prof. Dr. Maurício B. R. Correa, Prof. Dr. Antonio M. N. Lima".

Referências.

1. Conversores Estáticos – Energia Elétrica. 2. Sincronização. 3. *Phase Locked Loop* (PLL). 4. Controlador Proporcional Integral (PI). 5. Controlador Proporcional Ressonante (PR). 6. Banco de Filtros Adptativos de Atraso (Filtro ADB). 7. Eliminação de Harmônicos. I. Correa, Maurício B. R. II. Lima, Antonio M. N. III.Título.

CDU 621.314.57(043)

FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECÁRIA DILENE DE FÁTIMA DE LIMA PAULO (CRB - 15/48)

## "CONTRIBUIÇÕES PARA ALGORITMOS DE SINCRONIZAÇÃO DE CONVERSORES ESTÁTICOS CONECTADOS À REDE ELÉTRICA"

#### NICOLAU KELLYANO LEITE DANTAS

DISSERTAÇÃO APROVADA EM 03/09/2018

MAURÍCIO BELTRÃO DE ROSSITER CORRÊA, D.Sc., UFCG Orientador(a)

ANTONIO MARCUS NOGUEIRA LIMA, Dr., UFCG Orientador(a)

ALEXANDRE CUNHA OLIVEIRA, D.Sc., UFCG Examinador(a)

GUTEMBERG GONCALVES DOS SANTOS JÚNIOR, Dr., UFCG Examinador(a)

- 1

CAMPINA GRANDE - PB

### Agradecimentos

Primeiramente agradeço a Deus por todas as coisas boas que Ele tem me proporcionado, pela minha saúde e pelas oportunidades que me surgiram.

A meus pais Francisco Gomes Dantas e Maria Aparecida Leite, por serem os melhores pais que um filho pode ter. Proporcionaram-me tudo do melhor, educação, saúde, carinho, amor, acompanharam-me em minha trajetória de estudos e em todas as minhas conquistas, a cada minuto, com muita força, torcida e carinho. Posso não ser o melhor filho todos os dias, mas tenho os melhores pais sempre.

Ao meu avô Domingos Viana Maia por sua amizade, companheirismo e por sempre ajudar nos momentos em que mais precisei.

A minha família, pelo apoio em tudo que fiz e em todas as decisões importantes da minha vida.

Agradeço aos meus orientadores Antonio Marcus Nogueira Lima e Maurício Beltrão Rossiter Corrêa pelos diversos conselhos e suportes, tanto em âmbito profissional e acadêmico quanto pessoal.

Aos amigos João, Phelipe Leal, Rayan, Louelson, Revson, Reuben e Kinas pelos momentos de descontração e estudos compartilhados. Em especial ao meu amigo Eduardo Gomes, por toda ajuda oferecida no decorrer deste trabalho.

A todos os professores, coordenador e funcionários do Departamento de Engenharia Elétrica da UFCG.

### Resumo

Normalmente, para equipamentos conectados à rede como conversores de energia, filtros ativos, retificadores controlados e outros, os algoritmos phase locked loop (PLL) são usados para obter a sincronização entre à rede elétrica e o equipamento. No entanto, muitas vezes esses algoritmos de PLLs apresentam resposta dinâmica insatisfatória quando a rede elétrica apresenta distorções como harmônicos e degrau de fase. Neste trabalho, são discutidas melhorias de desempenhos no rastreamento de fase e frequência para algoritmos de PLLs. Inicialmente é proposto a utilização de um banco de filtros adaptativos de atraso (filtro ADB) para resolver o problema do erro de fase do PLL de onda quadrada (PLLOQ), quando a rede apresenta componentes harmônicas. Através dos testes de simulações e experimentais, foi verificado que o erro de fase causado por harmônicos pode ser eliminado. No entanto, a correção do erro introduziu um atraso de 10ms na dinâmica do PLLOQ. Ainda assim, esse PLL foi competitivo se comparado a outras estruturas, por exemplo, as que usam filtro notch adaptativo. Em seguida, é proposta a utilização do controlador proporcional ressonante (PR) ideal nas estruturas de PLLs. É apresentado um método sistemático para projetar os parâmetros de controle de um PLL utilizando o controlador PR. Comparações de desempenho do PLL clássico utilizando o controlador proporcional integral (PI) frente ao controlador PR são apresentadas através de simulações e resultados experimentais, e foi constatado que o PLL com controlador PR obteve uma resposta mais rápida na detecção da fase e frequência. Também foi verificada uma boa precisão (erro nulo em estado estacionário) na detecção dos parâmetros de interesse, além de obter resultados satisfatórios (conseguiu rastrear a fase e frequência) quando a rede apresentou distorções. Posteriormente, é comparado o desempenho dos seguintes PLLs: (1) PLL baseado na Transformação Inversa de Park (Park-PLL) utilizando os controladores PI e PR, (2) PLL baseado no Integrador Generalizado de Segunda Ordem (SOGI-PLL) utilizando o controlador PI e (3) Enhanced Phase Locked Loop (EPLL) com controlador PI. Através das análises, para diferentes cenários de rede, foi verificado que o melhor desempenho entre esses algoritmos ficou com o SOGI-PLL com controlador PI. O Park-PLL com controlador PR obteve o detector de fase mais rápido, enquanto que o EPLL com controlador PI obteve o detector de fase mais lento. Além disso, foi visto que esses algoritmos obtiveram erro nulo em estado estacionário, exceto quando a rede apresentou harmônicos. Por fim, foi realizada uma análise geral dos principais resultados obtidos neste trabalho, onde foram indicadas as melhores escolhas de PLLs para aplicações específicas.

Palavras-chave: Phase locked loop (PLL), controlador proporcional integral (PI), controlador proporcional ressonante (PR), banco de filtros adaptativos de atraso (filtro ADB), sincronização, eliminação de harmônicos.

### **Abstract**

Normally, for equipments connected to the grid such as power converters, active filters, controlled rectifiers and others, phase locked loop (PLL) algorithms are used to obtain synchronization between the electric grid and equipment. However, these PLL algorithms often present unsatisfactory dynamic response when the electrical grid presents distortions such as harmonics and phase steps. In this work, it is discussed performance improvements in phase and frequency tracking for PLL algorithms. It is proposed the use of an adaptive delay bank filter (ADB filter) to solve the problem of square wave PLL (PLLOQ) phase error, when the grid presents harmonic components. Through simulation and experimental tests, it was verified that the phase error caused by harmonics can be eliminated. However, the error correction introduced a delay of 10ms in PLLOQ dynamics. Nevertheless, this PLL was competitive when compared to other structures, for example, those that use adaptive notch filter. Next, it is proposed to use the ideal resonant proportional (PR) controller in PLL structures. A systematic method for designing the control parameters of a PLL using the PR controller is presented. Performance comparisons of the classical PLL using the proportional integral (PI) controller versus PR controller are presented by means of simulation and experimental results, where it was verified that the PLL with the PR controller obtained a faster response in the phase and frequency detection. It was also verified, a good precision (null error in steady state) in the detection of the parameters of interest, besides obtaining satisfactory results (it tracked phase and frequency) when the grid presented distortions. Subsequently, the performances of the following PLLs are compared: (1) PLL based on the Park Inverse Transformation (Park-PLL) using the PI and PR controllers, (2) PLL based on the Generalized Second Order Integrator (SOGI-PLL) using the PI controller and (3) Enhanced Phase Locked Loop (EPLL) with PI controller. Through the analyzes, for different grid scenarios, it was verified that the best performance among these algorithms was that of the SOGI-PLL with PI controller. The Park-PLL with PR controller obtained the fastest phase detection, while the EPLL with PI controller obtained the slowest phase detector. Furthermore, it was observed that these algorithms obtained null error in steady state, except when the grid presented harmonics. Finally, a general analysis of the main results obtained in this work was carried out, where the best PLL choices for specific applications were indicated.

**Keywords**: Phase locked loop (PLL), proportional integral (PI) control, proportional resonant (PR) control, adaptive delay bank filter (ADB filter), synchronization, harmonics elimination.

# Lista de ilustrações

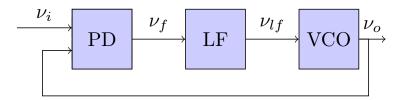

| Figura | 2.1 - | Estrutura básica de um PLL                                              | 5  |

|--------|-------|-------------------------------------------------------------------------|----|

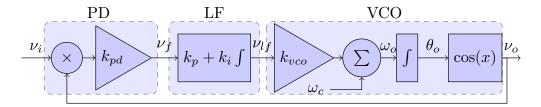

| Figura | 2.2 – | Diagrama de blocos do PLL clássico                                      | 6  |

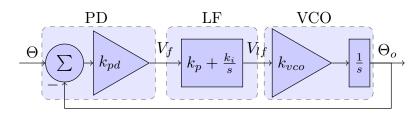

| Figura | 2.3 – | Modelo para pequenos sinais do PLL clássico                             | 7  |

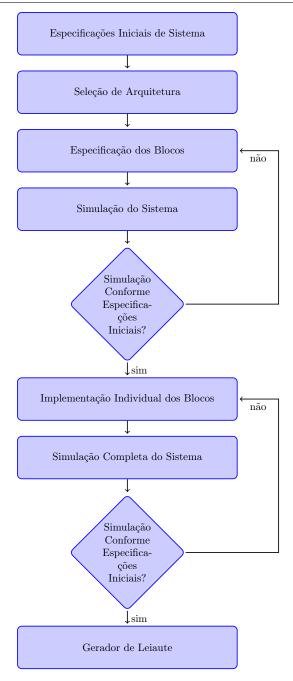

| Figura | 2.4 – | Fluxograma de projeto de um PLL [1]                                     | 10 |

| Figura | 2.5 – | PLL baseado na geração de sinais em quadratura                          | 11 |

| Figura | 2.6 - | PLL com bloco PD em quadratura e transformação de Park                  | 12 |

| Figura | 2.7 – | PLL baseado na transformação inversa de Park                            | 13 |

| Figura | 2.8 – | Estrutura do sistema ortogonal                                          | 14 |

| Figura | 2.9 – | Diagrama de Bode da função de transferência $H_d(s)$ para diferentes    |    |

|        |       | valores de $k$                                                          | 14 |

| Figura | 2.10- | -Diagrama de Bode da função de transferência $H_q(s)$ para diferentes   |    |

|        |       | valores de $k$                                                          | 14 |

| Figura | 2.11- | -Resposta ao degrau da função de transferência $H_d(s)$ para diferentes |    |

|        |       | valores de $k$                                                          | 14 |

| Figura | 2.12  | -Estrutura do SOGI-PLL                                                  | 15 |

| Figura | 2.13- | -Diagrama de blocos básico da estrutura EPLL                            | 16 |

| Figura | 2.14  | -Diagrama de blocos básico para o PLL de onda quadrada                  | 17 |

| Figura | 2.15  | -Onda quadrada e tensão de saída $\nu_o$ do PLL                         | 17 |

| Figura | 3.1 – | Diagrama de blocos básico para o PLL de onda quadrada com filtro        |    |

|        |       | ADB                                                                     | 20 |

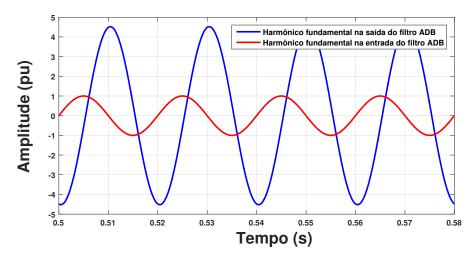

| Figura | 3.2 – | Diagrama de blocos básico do filtro ADB para eliminação seletiva de     |    |

|        |       | harmônicos                                                              | 21 |

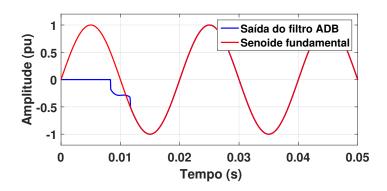

| Figura | 3.3 – | Harmônico fundamental do sinal da rede na entrada e na saída do filtro  |    |

|        |       | ADB                                                                     | 23 |

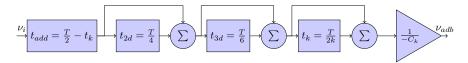

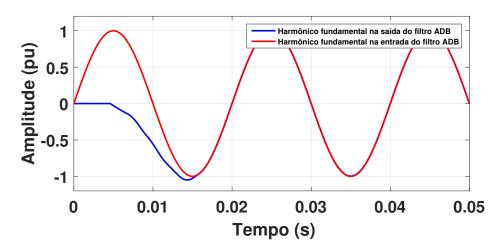

| Figura | 3.4 – | Diagrama de blocos básico do filtro ADB modificado                      | 24 |

| Figura | 3.5 – | Gráfico do harmônico fundamental do sinal da rede na entrada e na       |    |

|        |       | saída do filtro ADB modificado                                          | 24 |

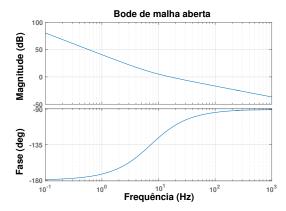

| Figura | 3.6 – | Diagrama de Bode dos sistemas em malha aberta pelo método canônico      |    |

|        |       | com $t_s = 100 \text{ms e } \xi = 0,707$                                | 25 |

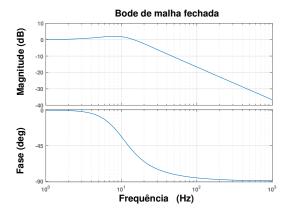

| Figura | 3.7 – | Diagrama de Bode dos sistemas em malha fechada pelo método canô-        |    |

|        |       | nico com $t_s = 100 \text{ms e } \xi = 0,707. \dots$                    | 25 |

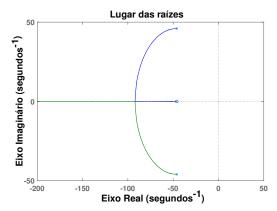

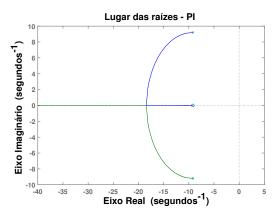

| Figura | 3.8 – | Lugar das Raízes dos sistemas em malha fechada pelo método canônico     |    |

|        |       | com $t_s = 100 \text{ms e } \xi = 0,707$                                | 26 |

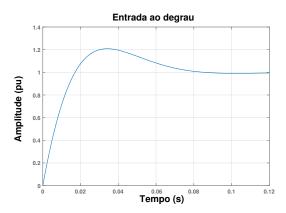

| Figura | 3.9 – | Resposta ao degrau dos sistemas em malha fechada pelo método canô-      |    |

|        |       | nico com $t_s = 100 \text{ms e } \xi = 0,707. \dots$                    | 26 |

| Figura | 3.10- | -Saída do filtro ADB projetado para eliminação do terceiro harmônico    | 27 |

| Figura 3.11–Resultados de simulações para o caso de uma entrada senoida distorções |        |

|------------------------------------------------------------------------------------|--------|

| Figura 3.12–Resultados de simulações para o caso de uma entrada senoida            |        |

| injeção de 30% da terceira harmônica                                               |        |

| Figura 3.13–Resultados de simulações para o caso de uma entrada senoida            |        |

| injeção de 30% da terceira harmônica defasada de 90° da compo                      |        |

| fundamental                                                                        |        |

| Figura 3.14–Foto da placa utilizada nos testes experimentais                       |        |

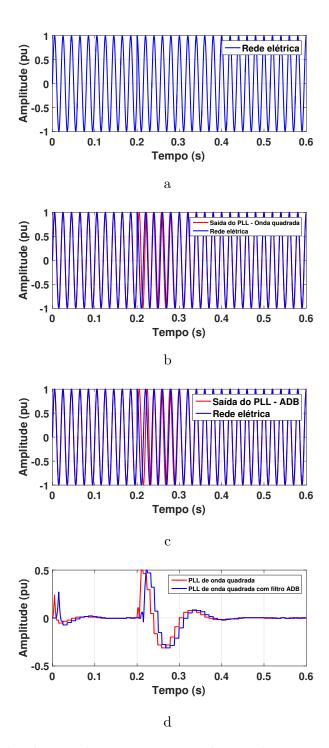

| Figura 3.15–Resultados das simulações para uma rede com distorções. (a) T          |        |

| de entrada com um degrau de fase de 90°. (b) Sinal de saída do                     |        |

| de onda quadrada. (c) Sinal de saída do PLL de onda quadrada                       |        |

| filtro ADB. (d) Sinal de erro dos PLLs                                             |        |

| Figura 3.16–Resultados das simulações para uma rede com afundamento de 30          | 0% na  |

| tensão. (a) Tensão de entrada com um afundamento de 30%. (b)                       | Sinal  |

| de saída do PLL de onda quadrada. (c) Sinal de saída do PLL de                     | e onda |

| quadrada com filtro ADB. (d) Sinal de erro dos PLLs                                | 33     |

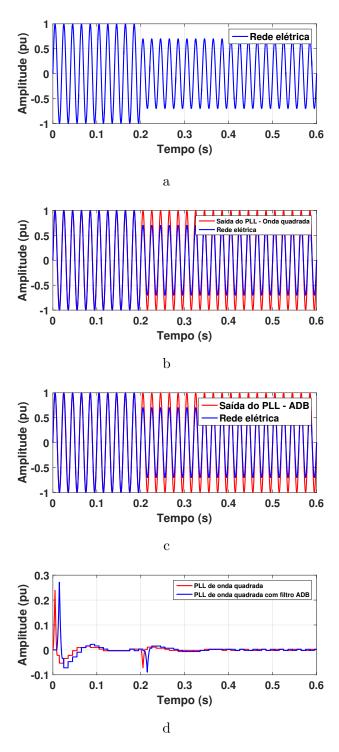

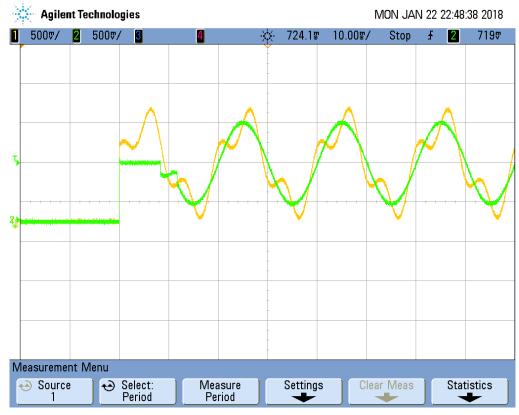

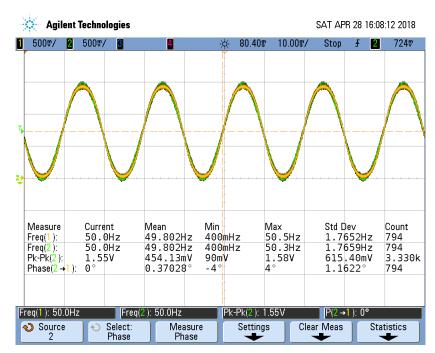

| Figura 3.17–Resultados experimentais do PLL de onda quadrada. Tensão de en         | ntrada |

| (amarelo) e saída do PLL de onda quadrada (verde)                                  | 34     |

| Figura 3.18–Resultados experimentais do PLL de onda quadrada. Referência           | senoi- |

| dal de 50Hz (amarelo) e saída do PLL de onda quadrada (verde)                      | ) 34   |

| Figura 3.19–Resultados experimentais do PLL de onda quadrada com filtro            | ADB.   |

| Sinal de entrada (amarelo) e saída do filtro ADB (verde)                           | 35     |

| Figura 3.20–Resultados experimentais do PLL de onda quadrada com filtro            | ADB.   |

| Sinal de saída do PLL de onda quadrada com filtro ADB (ven                         | rde) e |

| referência senoidal de 50Hz (amarelo)                                              | 35     |

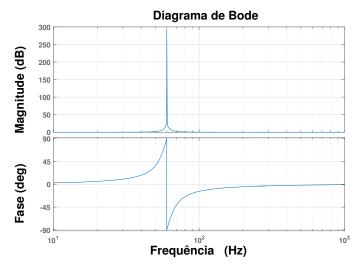

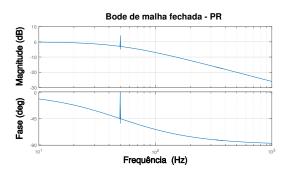

| Figura 4.1 – Diagrama de Bode do controlador PR                                    | 37     |

| Figura $4.2$ – Diagrama de blocos básico do PLL clássico com filtro MAF. $$        | 38     |

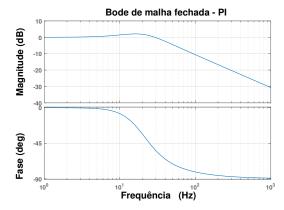

| Figura $4.3$ – Diagrama de Bode do sistema em malha fechada pelo método car        | nônico |

| com $t_s = 50 \text{ms e } \xi = 0,707.$                                           | 39     |

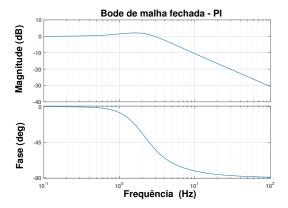

| Figura 4.4 – Diagrama de Bode dos sistemas em malha fechada pelo método            | canô-  |

| nico com $t_s = 500 \text{ms e } \xi = 0,707. \dots \dots \dots \dots \dots$       |        |

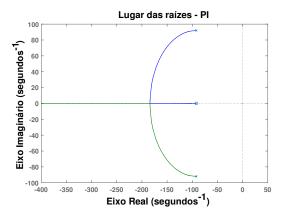

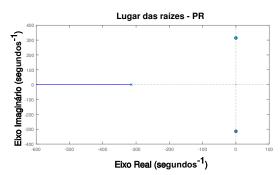

| Figura 4.5 – Lugar das Raízes do sistema em malha fechada pelo método car          | nônico |

| com $t_s = 50 \text{ms e } \xi = 0,707. \dots$                                     |        |

| Figura 4.6 – Lugar das Raízes do sistema em malha fechada pelo método car          | nônico |

| com $t_s = 500 \text{ms e } \xi = 0,707$                                           |        |

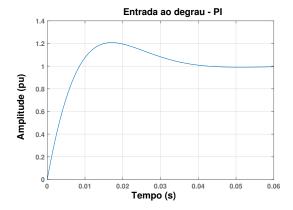

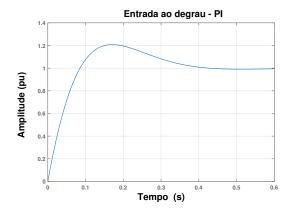

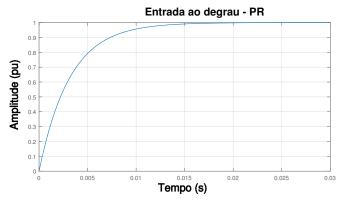

| Figura 4.7 – Resposta ao degrau do sistema em malha fechada pelo método car        |        |

| com $t_s = 50 \text{ms e } \xi = 0,707. \dots$                                     |        |

| Figura 4.8 – Resposta ao degrau do sistema em malha fechada pelo método car        |        |

| com $t_s = 500 \text{ms e } \xi = 0,707$                                           | 40     |

| rigura 4.9 - | - Diagrama de Bode do sistema em malha fechada pelo método de Naslin               | 4-1 |

|--------------|------------------------------------------------------------------------------------|-----|

| D: 4.10      | polinomial com $\alpha = 1,000001$                                                 | 41  |

| Figura 4.10  | -Lugar das raízes do sistema em malha fechada pelo método de Naslin                | 4.1 |

| D. 444       | polinomial com $\alpha = 1,000001$                                                 | 41  |

| Figura 4.11  | Resposta ao degrau do sistema em malha fechada pelo método de Naslin               |     |

|              | polinomial com $\alpha = 1,000001$                                                 | 41  |

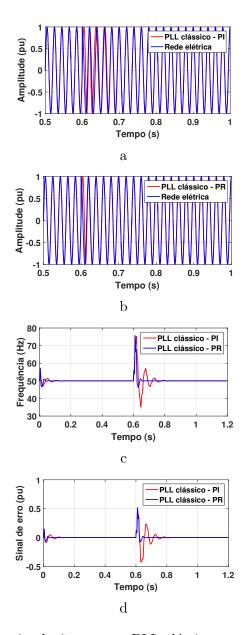

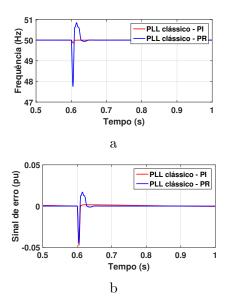

| Figura 4.12  | Resultados das simulações para o PLL clássico quando a rede sofre um               |     |

|              | salto de fase. (a) Saída do PLL clássico com controlador PI ajustado               |     |

|              | para $t_s = 50 \text{ms.}$ (b) Saída do PLL clássico com controlador PR. (c)       |     |

|              | Frequência rastreada pelo PLL clássico com controlador PI e PR. (d)                |     |

|              | Sinal de erro do PLL clássico com controlador PI e PR                              | 43  |

| Figura 4.13  | –Resultados das simulações para o PLL clássico quando a rede sofre um              |     |

|              | salto de fase. (a) Saída do PLL clássico com controlador PI ajustado               |     |

|              | para $t_s = 500 \text{ms.}$ (b) Frequência rastreada pelo PLL clássico com con-    |     |

|              | trolador PI e PR. (c) Sinal de erro do PLL clássico, com controlador               |     |

|              | PI e PR, antes da ocorrência do salto de fase. (d) Sinal de erro do PLL            |     |

|              | clássico, com controlador PI e PR, após o salto de fase                            | 48  |

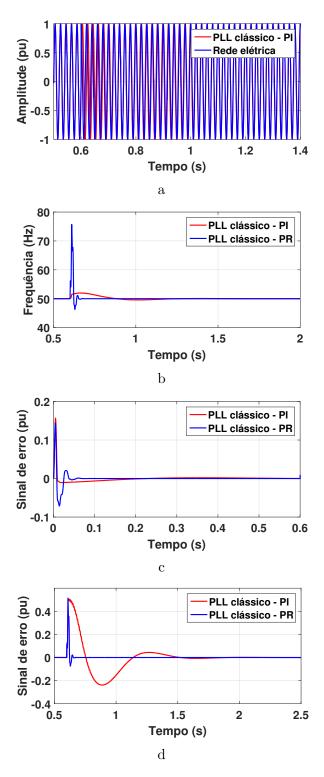

| Figura 4.14  | –Resultados das simulações para o PLL clássico quando a rede sofre                 |     |

|              | um afundamento de tensão de 30%. (a) Saída do PLL clássico com                     |     |

|              | controlador PI ajustado para $t_s=50\mathrm{ms}.$ (b) Saída do PLL clássico        |     |

|              | com controlador PR. (c) Frequência rastreada pelo PLL clássico com                 |     |

|              | controlador PI e PR. (d) Sinal de erro do PLL clássico com controlador             |     |

|              | PI e PR                                                                            | 49  |

| Figura 4.15  | Resultados das simulações para o PLL clássico quando a rede sofre                  |     |

|              | um afundamento de tensão de 30%. (a) Frequência rastreada pelo PLL                 |     |

|              | clássico com controlador PI (projetado para $t_s=500\mathrm{ms}$ ) e PR. (b) Sinal |     |

|              | de erro do PLL clássico com controlador PI (projetado para $t_s=500 \mathrm{ms}$ ) |     |

|              | e PR                                                                               | 50  |

| Figura 4.16  | Resultados das simulações para o PLL clássico quando a rede contém                 |     |

|              | harmônicos. (a) Rede elétrica com presença da componente de terceiro               |     |

|              | harmônico. (b) Frequência rastreada pelo PLL clássico com controlador              |     |

|              | PI e PR. (c) Sinal de erro do PLL clássico com controlador PI e PR.   .            | 50  |

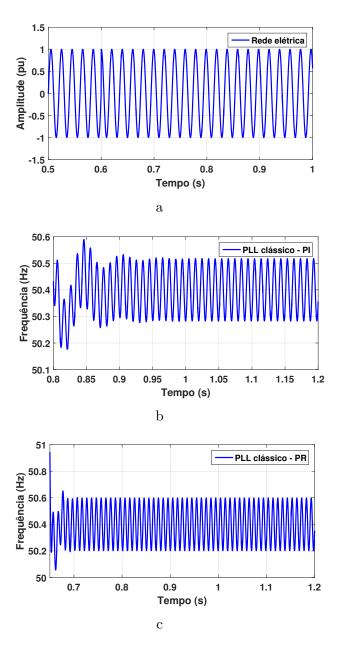

| Figura 4.17  | -Resultados das simulações para o PLL clássico quando a rede contém                |     |

|              | uma variação na frequência de 50 a 50,4Hz. (a) Sinal da rede elétrica.             |     |

|              | (b) Frequência rastreada pelo PLL clássico com controlador PI. (c)                 |     |

|              | Frequência rastreada pelo PLL clássico com controlador PR                          | 51  |

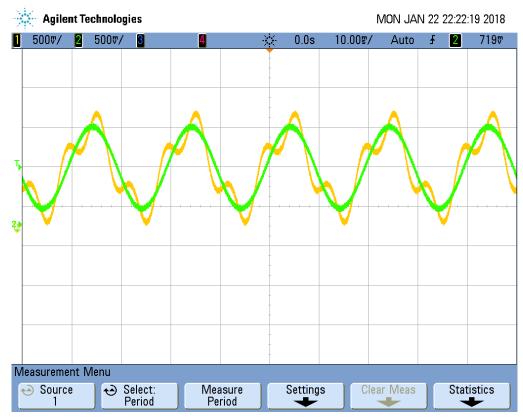

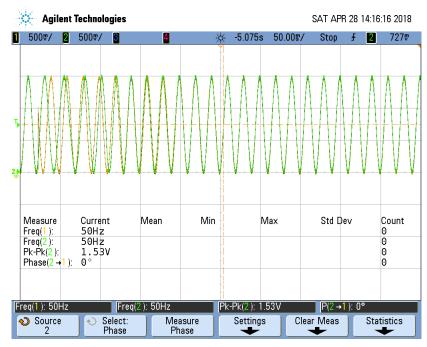

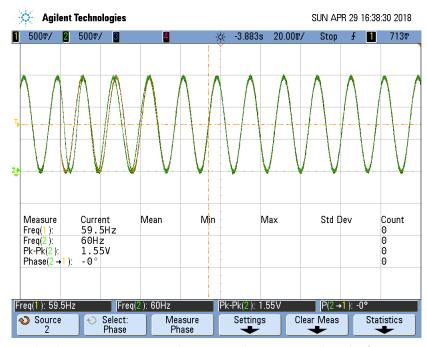

| Figura 4.18  | -Resultado experimental do PLL clássico com controlador PI durante                 |     |

|              | o salto de fase. Tensão de entrada (amarelo) e sinal de saída do PLL               |     |

|              | (verde)                                                                            | 52  |

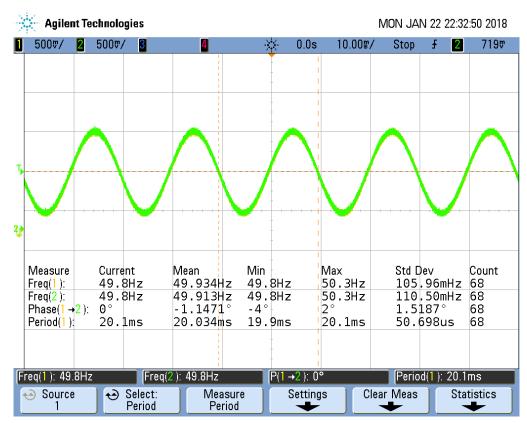

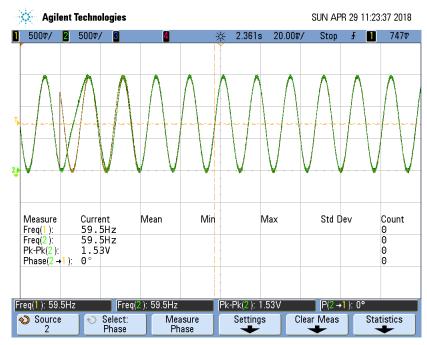

| Figura 4.19- | Resultado experimental do PLL clássico com controlador PR durante        |    |

|--------------|--------------------------------------------------------------------------|----|

|              | o salto de fase. Tensão de entrada (amarelo) e sinal de saída do PLL     |    |

|              | (verde)                                                                  | 52 |

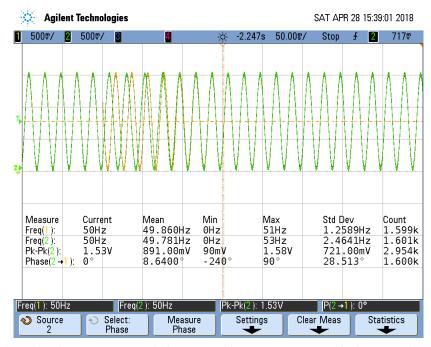

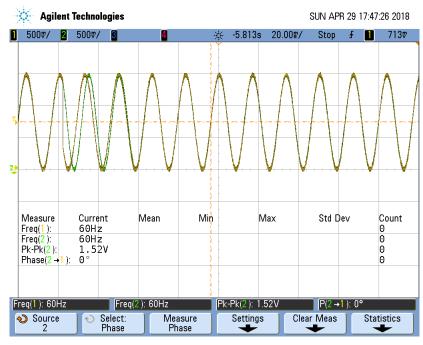

| Figura 4.20- | -Resultado experimental do PLL clássico com controlador PR para uma      |    |

|              | rede com a presença da componente de terceiro harmônico. Tensão de       |    |

|              | entrada (amarelo) e sinal de saída do PLL (verde)                        | 53 |

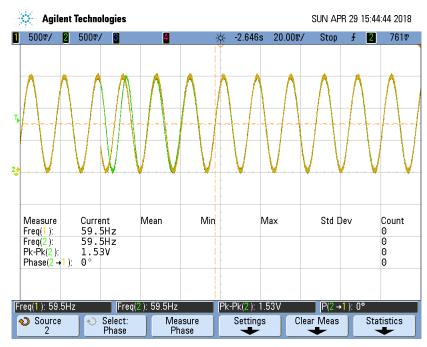

| Figura 4.21- | -Resultado experimental do PLL clássico com controlador PR para uma      |    |

|              | rede com a presença da componente de terceiro harmônico. Sinal de        |    |

|              | referência senoidal (amarelo) e sinal de saída do PLL (verde)            | 53 |

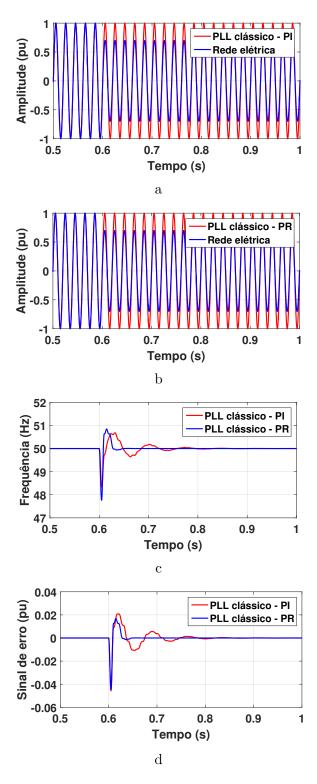

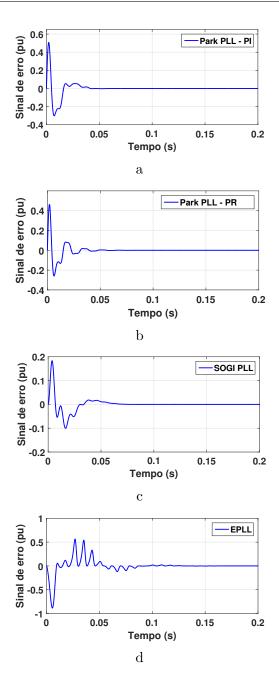

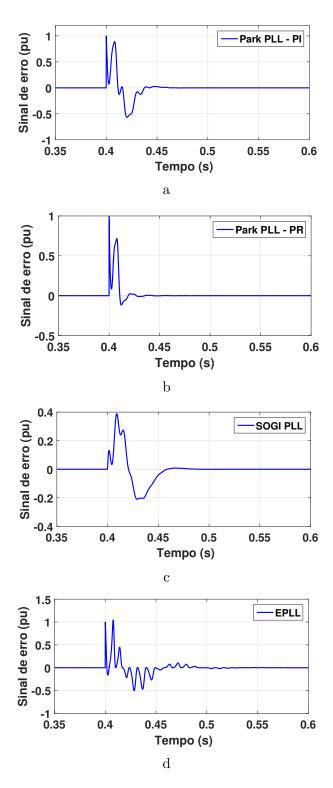

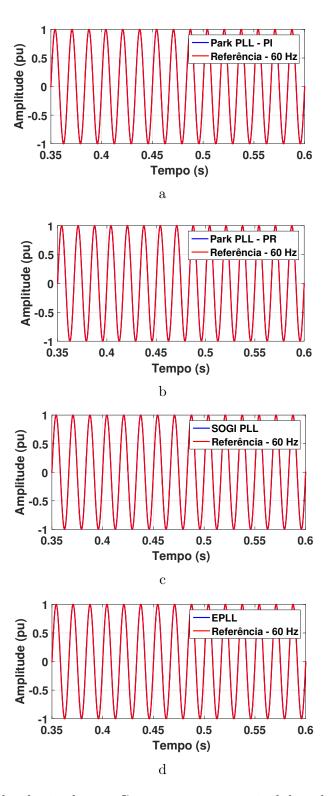

| Figura 5.1 – | Resultados de simulações. Comparação entre os sinais de erros dos al-    |    |

|              | goritmos para uma rede sem distorções. (a) Sinal de erro do Park PLL     |    |

|              | - PI. (b) Sinal de erro do Park PLL - PR. (c) Sinal de erro do SOGI      |    |

|              | PLL. (d) Sinal de erro do EPLL                                           | 57 |

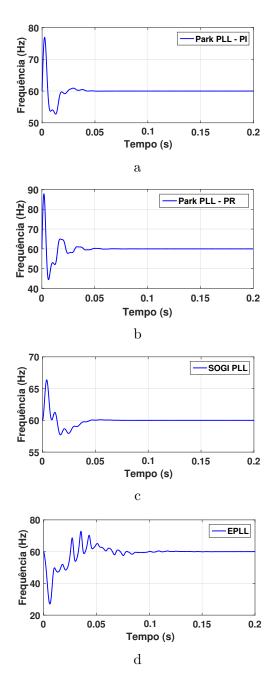

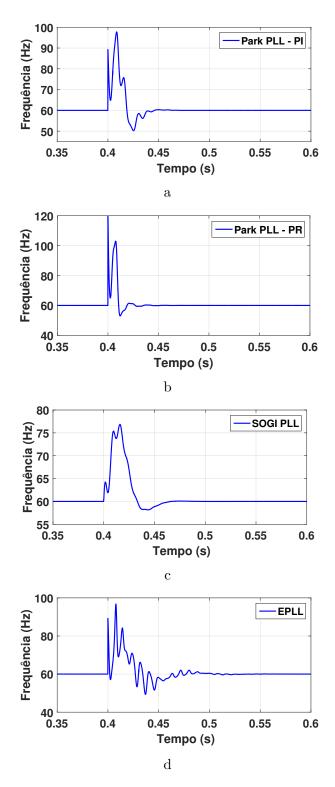

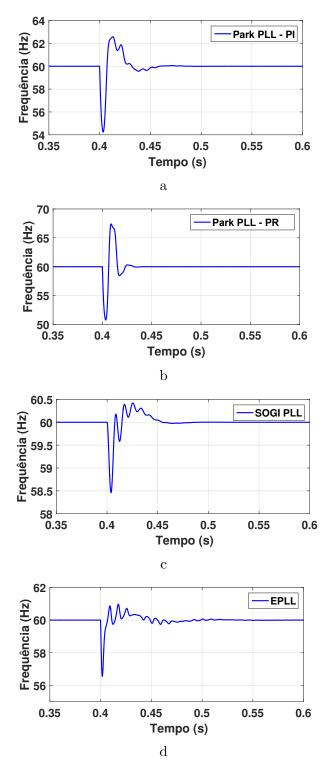

| Figura 5.2 – | Resultados de simulações. Frequência rastreada pelos algoritmos para     |    |

|              | uma rede sem distorções. (a) Frequência rastreada pelo Park PLL - PI.    |    |

|              | (b) Frequência rastreada pelo Park PLL - PR. (c) Frequência rastreada    |    |

|              | pelo SOGI PLL. (d) Frequência rastreada pelo EPLL                        | 58 |

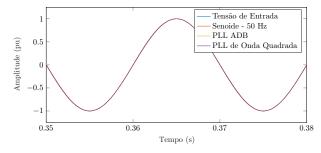

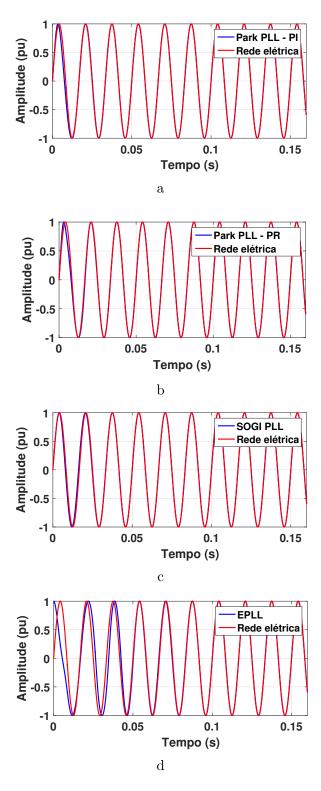

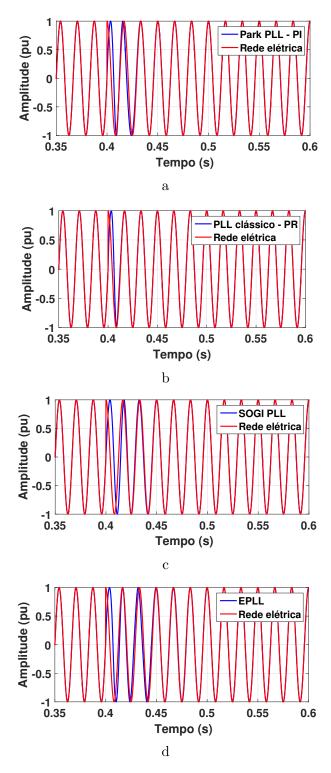

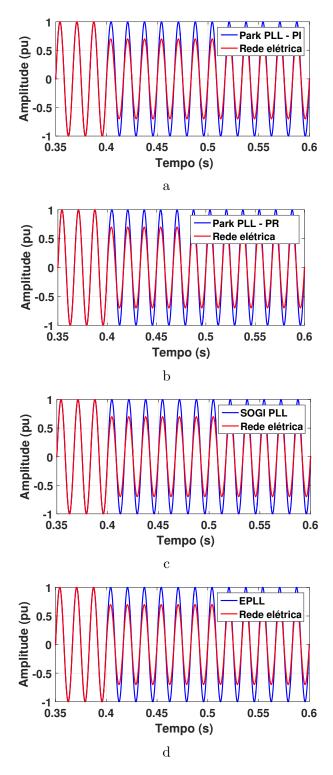

| Figura 5.3 – | Resultados de simulações. Comparação entre o sinal da rede (referência)  |    |

|              | e o sinal estimado pelos algoritmos para teste de rede sem distorções.   |    |

|              | (a) Sinal de saída do Park PLL - PI e referência. (b) Sinal de saída     |    |

|              | do Park PLL - PR e referência. (c) Sinal de saída do SOGI PLL e          |    |

|              | referência. (d) Sinal de saída do EPLL e referência                      | 63 |

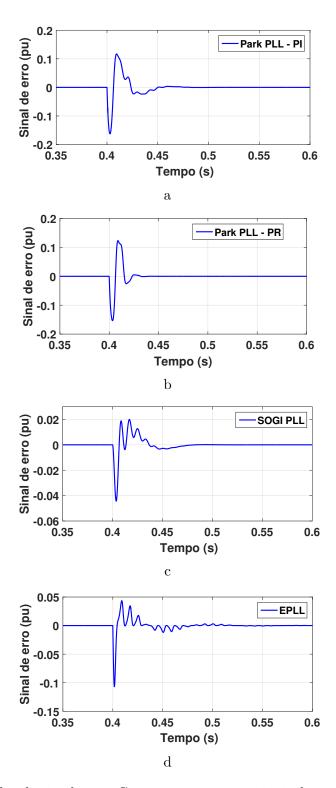

| Figura 5.4 – | Resultados de simulações. Comparação entre os sinais de erros dos al-    |    |

|              | goritmos durante o salto de fase. (a) Sinal de erro do Park PLL - PI.    |    |

|              | (b) Sinal de erro do Park PLL - PR. (c) Sinal de erro do SOGI PLL.       |    |

|              |                                                                          | 64 |

| Figura 5.5 – | Resultados de simulações. Frequência rastreada pelos algoritmos du-      |    |

|              | rante o salto de fase. (a) Frequência rastreada pelo Park PLL - PI. (b)  |    |

|              | Frequência rastreada pelo Park PLL - PR. (c) Frequência rastreada        |    |

|              |                                                                          | 65 |

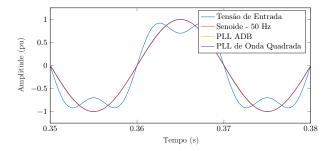

| Figura 5.6 – | Resultados de simulações. Comparação entre o sinal da rede (referência)  |    |

|              | e o sinal estimado pelos algoritmos para o teste de salto de fase. (a)   |    |

|              | Sinal de saída do Park PLL - PI e referência. (b) Sinal de saída do Park |    |

|              | PLL - PR e referência. (c) Sinal de saída do SOGI PLL e referência.      |    |

|              |                                                                          | 66 |

| Figura 5.7 – | Resultados de simulações. Comparação entre os sinais de erros dos al-    |    |

|              | goritmos durante o afundamento de tensão. (a) Sinal de erro do Park      |    |

|              | PLL - PI. (b) Sinal de erro do Park PLL - PR. (c) Sinal de erro do       | c- |

|              | SOGI PLL. (d) Sinal de erro do EPLL                                      | 67 |

| Figura 5.8 – | Resultados de simulações. Frequência rastreada pelos algoritmos du-      |    |

|--------------|--------------------------------------------------------------------------|----|

|              | rante o afundamento de tensão. (a) Frequência rastreada pelo Park        |    |

|              | PLL - PI. (b) Frequência rastreada pelo Park PLL - PR. (c) Frequên-      |    |

|              | cia rastreada pelo SOGI PLL. (d) Frequência rastreada pelo EPLL          | 68 |

| Figura 5.9 – | Resultados de simulações. Comparação entre o sinal da rede (referência)  |    |

|              | e o sinal estimado pelos algoritmos para o teste de afundamento de       |    |

|              | tensão. (a) Sinal de saída do Park PLL - PI e referência. (b) Sinal de   |    |

|              | saída do Park PLL - PR e referência. (c) Sinal de saída do SOGI PLL      |    |

|              | e referência. (d) Sinal de saída do EPLL e referência                    | 69 |

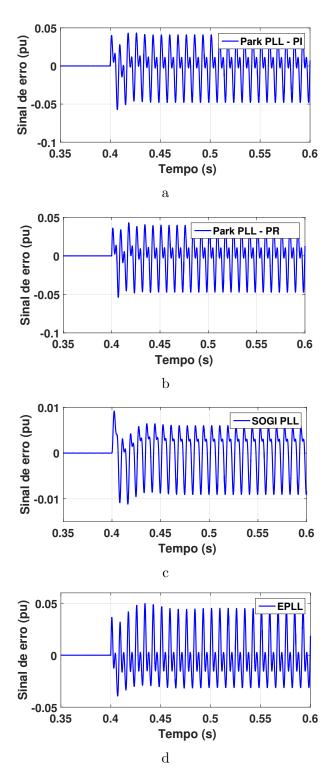

| Figura 5.10- | Resultados de simulações. Comparação entre os sinais de erros dos al-    |    |

|              | goritmos durante a distorção harmônica. (a) Sinal de erro do Park PLL    |    |

|              | - PI. (b) Sinal de erro do Park PLL - PR. (c) Sinal de erro do SOGI      |    |

|              | PLL. (d) Sinal de erro do EPLL                                           | 70 |

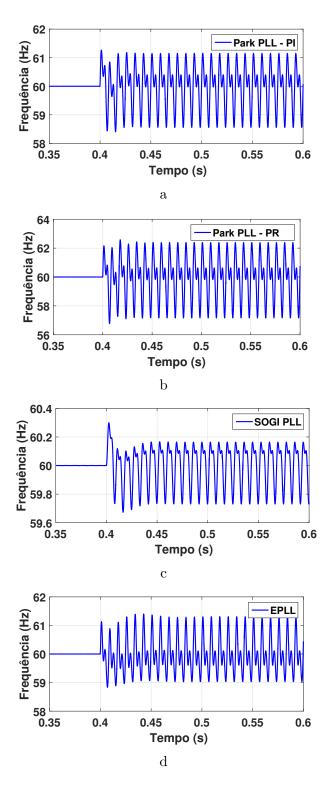

| Figura 5.11- | Resultados de simulações. Frequência rastreada pelos algoritmos du-      |    |

|              | rante a distorção harmônica. (a) Frequência rastreada pelo Park PLL      |    |

|              | - PI. (b) Frequência rastreada pelo Park PLL - PR. (c) Frequência        |    |

|              | . , , , , , , , , , , , , , , , , , , ,                                  | 71 |

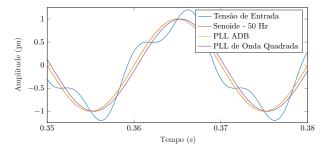

| Figura 5.12- | -Resultados de simulações. Comparação entre o sinal da rede (referência) |    |

|              | e o sinal estimado pelos algoritmos para o teste de distorção harmônica. |    |

|              | (a) Sinal de saída do Park PLL - PI e referência. (b) Sinal de saída     |    |

|              | do Park PLL - PR e referência. (c) Sinal de saída do SOGI PLL e          |    |

|              | referência. (d) Sinal de saída do EPLL e referência                      | 72 |

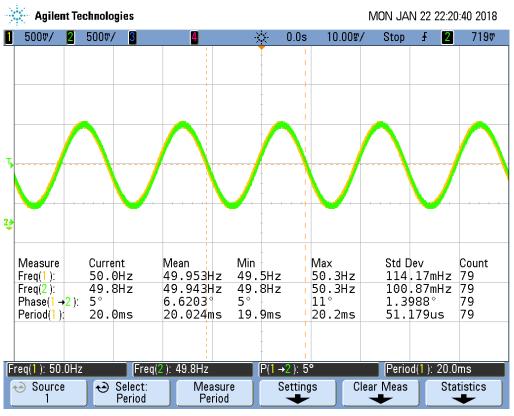

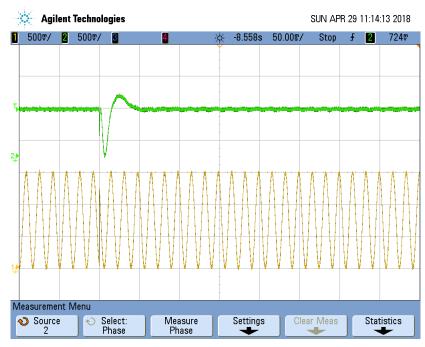

| Figura 5.13- | -Resultados experimentais do Park-PLL com controlador PI durante o       |    |

|              | salto de fase. Tensão de entrada (amarelo) e sinal de erro (verde)       | 73 |

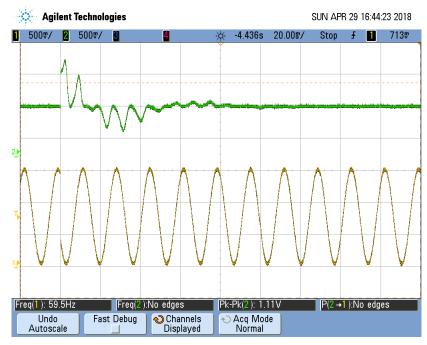

| Figura 5.14- | -Resultados experimentais do Park-PLL com controlador PR durante o       |    |

|              | salto de fase. Tensão de entrada (amarelo) e sinal de erro (verde)       | 73 |

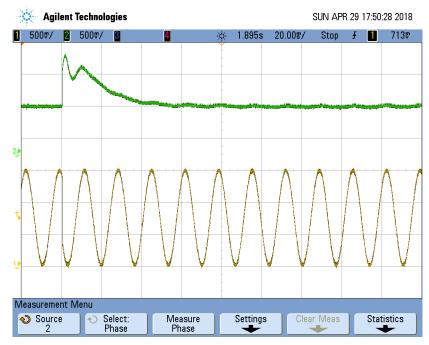

| Figura 5.15- | -Resultados experimentais do SOGI-PLL durante o salto de fase. Tensão    |    |

|              | de entrada (amarelo) e sinal de erro (verde)                             | 74 |

| Figura 5.16- | -Resultados experimentais do EPLL durante o salto de fase. Tensão de     |    |

|              | entrada (amarelo) e sinal de erro (verde)                                | 74 |

| Figura 5.17- | -Resultados experimentais do Park-PLL com controlador PI durante o       |    |

|              | salto de fase. Tensão de entrada (amarelo) e sinal de saída do Park-PLL  |    |

|              | PI (verde)                                                               | 75 |

| Figura 5.18- | -Resultados experimentais do Park-PLL com controlador PR durante o       |    |

|              | salto de fase. Tensão de entrada (amarelo) e sinal de saída do Park-PLL  |    |

|              | com controlador PR (verde)                                               | 75 |

| Figura 5.19- | -Resultados experimentais do SOGI-PLL durante o salto de fase. Tensão    |    |

| J - 0        | de entrada (amarelo) e sinal de saída do SOGI-PLL (verde)                | 76 |

|              |                                                                          | -  |

| Figura 5.20–Resultados experimentais do EPLL durante o salto de fase. Tensão de      |    |

|--------------------------------------------------------------------------------------|----|

| entrada (amarelo) e sinal de saída do EPLL (verde)                                   | 76 |

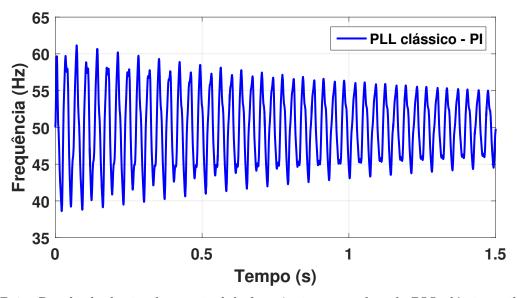

| Figura B.1 – Resultado da simulação: sinal de frequência rastreado pelo PLL clássico |    |

| utilizando um controlador PI projetado para $t_s=30 \mathrm{ms.}$                    | 89 |

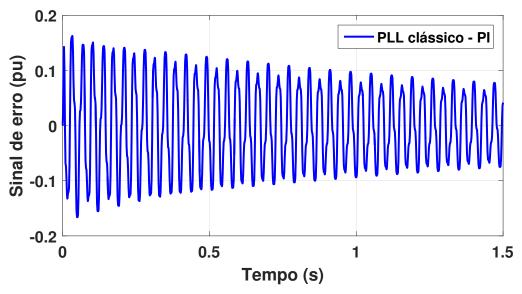

| Figura B.2 – Resultado da simulação: sinal de erro do pelo PLL clássico utilizando   |    |

| um controlador PI projetado para $t_s = 30 \text{ms.}$                               | 89 |

|                                                                                      |    |

## Lista de tabelas

| Tabela 3.1 – Mudanças nos parâmetros do harmônico fundamental                                  | 22 |

|------------------------------------------------------------------------------------------------|----|

| Tabela 3.2 – Parâmetros calculados para projeto do filtro ADB                                  | 26 |

| Tabela 5.1 – Ganhos utilizados nos testes.                                                     | 55 |

| Tabela 5.2 – Resultados de simulações. $t_s, V_p$ e $M_p$ para o teste da rede sem distorções. | 60 |

| Tabela 5.3 – Resultados de simulações. $t_s,\ V_p$ e $M_p$ para o teste da rede com um         |    |

| salto de fase.                                                                                 | 60 |

| Tabela 5.4 – Resultados de simulações. $t_s,\ V_p$ e $M_p$ para o teste da rede com um         |    |

| afundamento de tensão                                                                          | 61 |

| Tabela 5.5 – Resultados de simulações. Erros de pico a pico em estado estacionário             |    |

| para uma rede com presença de harmônicos                                                       | 61 |

| Tabela 6.1 – Resumo dos principais resultados das simulações                                   | 79 |

| Tabela 6.2 – Comparação de desempenho dos PLLs                                                 | 79 |

### Lista de abreviaturas e siglas

PLL Phase Locked Loop

FPB Filtro Passa Baixa

VCO Oscilador Controlado por Tensão (Voltage-Controlled-Oscillator)

PD Detector de Fase (Phase Detector)

LF Loop Filter

PI Proporcional Integral

PR Proporcional Ressonante

SOGI Integrador Generalizado de Segunda Ordem

DSP Processador Digital de Sinal (Digital Signal Processor)

QSG Geração de Sinal em Quadratura (Quadrature Signal Generator)

MAF Filtro de Média Móvel (Moving Average Filter)

SRF Quadro de Referência Síncrono (Synchronous Reference Frame)

FPGA Arranjos de Portas Programáveis em Campo (Field-Programmable Gate

Arrays)

ADB Banco Adaptativo de Atraso (Adaptive Delay Bank)

CDSC Cascata de Cancelamento de Sinal por Atraso (Cascaded Delayed Sig-

nal Cancellation)

IEEE Institute of Electrical and Electronics Engineers

SOGI Integrador Generalizado de Segunda Ordem

EPLL Enhanced Phase Locked Loop

ANF Filtro Notch Adaptativo (Filter Adaptive Notch)

FIR Resposta de Impulso Finito (Finite-Impulse-Response)

SHE Eliminação Seletiva de Harmônicos (Selective Harmonics Elimination)

ZCD Detecção de Cruzamento por Zero (Zero Crossing Detection)

## Sumário

| 1     | INTRODUÇÃO                                                     | 1  |

|-------|----------------------------------------------------------------|----|

| 1.1   | Apresentação do Tema                                           | 1  |

| 1.2   | Objetivos                                                      | 3  |

| 1.3   | Organização da Dissertação                                     | 3  |

| 2     | PHASE LOCKED LOOP MONOFÁSICOS                                  | 5  |

| 2.1   | Introdução                                                     | 5  |

| 2.2   | Estrutura Básica de um PLL                                     | 5  |

| 2.3   | Equações Básica de um PLL                                      | 6  |

| 2.4   | Modelo Linearizado de um PLL para Pequenos Sinais              | 7  |

| 2.5   | Metodologia de Projeto para um PLL                             | 9  |

| 2.6   | PLL Baseado na Transformação Inversa de Park                   | 11 |

| 2.7   | PLL Baseado no Integrador Generalizado de Segunda Ordem        | 13 |

| 2.8   | O Enhanced Phase Locked Loop                                   | 15 |

| 2.9   | PLL Baseado na Realimentação em Onda Quadrada                  | 16 |

| 2.9.1 | Filtro de Média Móvel                                          | 18 |

| 2.10  | Conclusões Parciais                                            | 19 |

| 3     | UTILIZAÇÃO DE BANCO DE FILTROS ADAPTATIVOS DE ATRASO           | )  |

|       | EM ALGORITMO PHASE LOCKED LOOP                                 |    |

| 3.1   | Introdução                                                     | 20 |

| 3.2   | Estrutura do PLL com Filtro ADB                                | 20 |

| 3.3   | Análise do Impacto do Filtro ADB sobre o Harmônico Fundamental |    |

|       | do Sinal da Rede                                               | 21 |

| 3.4   | Resultados de Simulações                                       | 24 |

| 3.4.1 | Análise de Estabilidade e Resposta Dinâmica                    | 25 |

| 3.4.2 | Projeto do Filtro ADB para Eliminação de Terceiro Harmônico    | 26 |

| 3.4.3 | Discretização                                                  | 26 |

| 3.4.4 | Testes em Estado Estacionário                                  | 27 |

| 3.4.5 | Testes de Transitórios                                         | 29 |

| 3.5   | Resultados Experimentais                                       | 30 |

| 3.5.1 | Tensão da Rede com Presença de Componentes Harmônicas          | 31 |

| 3.6   | Conclusões Parciais                                            | 31 |

|       |                                                                |    |

| 4     | UTILIZAÇÃO DO CONTROLADOR PROPORCIONAL RESSO-                  |    |

| 4.1     | Introdução                                                                       | . 36  |

|---------|----------------------------------------------------------------------------------|-------|

| 4.2     | Controlador Proporcional Ressonante                                              | . 36  |

| 4.3     | Projeto dos Ganhos para o Controlador Proporcional Ressonante .                  | . 37  |

| 4.4     | Resultados de Simulações                                                         | . 38  |

| 4.4.1   | Análise de Estabilidade e Resposta Dinâmica                                      | . 39  |

| 4.4.2   | Discretização                                                                    | . 41  |

| 4.4.3   | Testes em Estado Estacionário e Transitório                                      | . 42  |

| 4.4.3.1 | Salto de Fase                                                                    | . 42  |

| 4.4.3.2 | Afundamento de Tensão                                                            | . 44  |

| 4.4.3.3 | Presença de Harmônicos                                                           | . 44  |

| 4.4.3.4 | Degrau de Frequência                                                             | . 45  |

| 4.5     | Resultados Experimentais                                                         | . 46  |

| 4.6     | Conclusões Parciais                                                              | . 46  |

| 5       | ANÁLISE DE DESEMPENHO DE ALGORITMOS PHASE LOC-                                   |       |

|         | KED LOOP                                                                         | . 54  |

| 5.1     | Introdução                                                                       | . 54  |

| 5.2     | Testes de Desempenho                                                             | . 54  |

| 5.2.1   | Discretização                                                                    | . 56  |

| 5.2.2   | Resultados de Simulações                                                         | . 56  |

| 5.2.2.1 | Testes para uma Rede sem Distorções                                              | . 56  |

| 5.2.2.2 | Testes de Salto de Fase                                                          | . 56  |

| 5.2.2.3 | Testes de Afundamento de Tensão                                                  | . 59  |

| 5.2.2.4 | Testes de Distorção Harmônica                                                    | . 59  |

| 5.2.3   | Resultados Experimentais                                                         | . 60  |

| 5.2.4   | Síntese dos Resultados                                                           | . 60  |

| 5.3     | Conclusões Parciais                                                              | . 62  |

| 6       | CONCLUSÃO                                                                        | . 77  |

| 6.1     | Perspectivas de Trabalhos Futuros                                                | . 80  |

|         | REFERÊNCIAS                                                                      | . 81  |

|         | APÊNDICES                                                                        | 86    |

|         | APÊNDICE A – DESENVOLVIMENTO DO PROJETO PARA O CONTROLADOR PROPORCIONAL RESSONAN | TE 87 |

|         | APÊNDICE B – RESPOSTA DO PLL CLÁSSICO                                            | . 89  |

### 1 Introdução

#### 1.1 Apresentação do Tema

Os sistemas de geração de energia elétrica, baseados em fontes renováveis de energia, cada vez mais tem sido integrados aos sistemas de geração de energia elétrica de vários países. Isso ocorre devido aos benefícios técnicos e econômicos que esse tipo de sistema fornece. Tais benefícios podem ser:

- Redução de perdas do sistema;

- Economia nos custos de transmissão e distribuição;

- Redução do preço da eletricidade.

Visando a utilização de sistemas de geração de energia distribuída de baixa potência, utilizando fontes renováveis de energia, como turbinas eólicas e painéis fotovoltaicos, para o fornecimento de energia elétrica, faz-se necessária a interligação destes sistemas de geração às redes elétricas de distribuição. Para tal interligação, são utilizados conversores estáticos de energia, que irão adequar a energia gerada aos padrões operacionais das redes elétricas, notadamente, amplitude, frequência e fase.

De acordo com [2] uma parcela importante no controle de todos os conversores monofásicos é a unidade de sincronização, que é responsável pela conexão suave do conversor à rede elétrica, além de seu monitoramento. A informação fornecida pela unidade de sincronização (que é frequentemente fase, frequência e amplitude do harmônico fundamental da tensão da rede) é também de extrema importância para a estratégia de controle do conversor durante a condição de operação normal, particularmente para a geração da corrente de referência para o conversor.

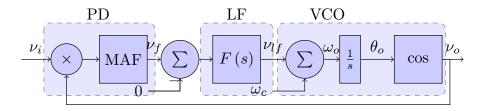

Várias técnicas de sincronização têm sido propostas na literatura. Uma estratégia bastante utilizada é baseada no algoritmo *Phase-Locked-Loop* (PLL). O PLL é um sistema em malha fechada que trava sua saída com o sinal de entrada mantendo um erro de fase constante (idealmente zero) [3]. Todos os PLLs possuem três partes em comum: i) detector de fase (PD), responsável por gerar um erro de fase entre o sinal de entrada e o estimado. ii) *loop filter* (LF), responsável por eliminar distúrbios dentro do *loop* de controle do PLL. iii) oscilador controlado por tensão (VCO) responsável por gerar o sinal sincronizado com a entrada do PLL. Os requisitos de desempenho de um PLL são o erro de fase em regime permanente, a velocidade de resposta a distúrbios de frequência, fase e amplitude das tensões de entrada, a imunidade a harmônicos e no caso trifásico a imunidade ao

desbalanceamento de fases. Portanto, o sistema de PLL deve ser capaz de determinar o ângulo de fase do sinal mesmo para diversas distorções presentes no sistema elétrico.

Nos últimos anos, um grande número de PLLs monofásicos com diferentes estruturas e propriedades foram desenvolvidos na literatura técnica [4–17]. Em [2] é proposta uma classificação dos PLLs monofásicos em duas categorias principais: 1) PLLs baseados em energia (pPLLs) e 2) PLLs baseados na geração de sinais em quadratura (QSG-PLLs). A principal diferença entre essas duas categorias consiste no bloco PD dos PLLs.

A categoria dos pPLLs são caracterizados por terem um bloco PD do tipo produto. Devido a isso, o sinal de saída gerado pelo bloco PD contêm termos oscilatórios com o dobro da frequência do sinal de entrada, gerando com isso um erro nas quantidades estimadas pelo pPLL padrão [2]. Devido a essa problemática, nos últimos anos vários pPLLs avançados foram projetados. A principal diferença entre eles, está relacionada a estratégia de filtragem para eliminar o termo de pertubação de frequência dupla [2]. Podese citar como exemplos dessas estratégias: filtro de média móvel (MAF), filtros notch, entre outros.

De acordo com [2], o grupo dos QSG-PLLs podem ser entendidos como a versão monofásica do PLL baseado no quadro de referência síncrono (SRF-PLL), que é uma versão padrão em aplicações de sistemas trifásicos. O que a maioria dos QSG-PLLs têm em comum é uma unidade para criar um sinal de quadratura fictício, que é necessário para transferir as informações para o quadro girante dq. Esta unidade pode ser implementada utilizando filtros, algoritmos, e etc.

É muito comum na literatura utilizar um controlador proporcional integral (PI) no bloco LF de um PLL, proporcionando um desempenho considerado satisfatório. No entanto, os controladores PI são propensos a desvantagens conhecidas, incluindo a incapacidade de rastrear uma referência senoidal sem erro de estado estacionário, além de problemas relacionados à filtragem harmônica de baixa ordem devido a limitações na largura de banda [18]. Algumas estratégias podem ser utilizadas para melhorar o desempenho do controlador PI, como aumento do ganho proporcional, resultando em uma largura de banda maior e pode reduzir os limites de estabilidade. O controlador proporcional ressonante (PR) pode ser usado no lugar do controlador PI para eliminar o erro de estado estacionário e fornecer seletividade de rejeição harmônica [18, 19].

Em [20] e [21] uma estrutura de PLL monofásica foi projetada para aplicações analógicas, onde o VCO foi implementado através de uma onda quadrada ao invés de usar uma onda senoidal. Este método não precisa de um multiplicador analógico no bloco PD e é adequado para implementações de hardware com entrada senoidal pura [22]. A estratégia de onda quadrada pode ser útil para PLLs implementados em microcontroladores, processadores de sinais digitais (DSPs) e arranjos de portas programáveis em campo (FPGA). Uma vantagem dessa estratégia em relação ao PLL clássico (VCO senoidal) é

reduzir o uso de memória associado às longas tabelas de busca que são necessárias para armazenar as formas de onda senoidais com precisão razoável [22]. De acordo com [21], o PLL de onda quadrada não é aplicável a sinais de entrada com harmônicos porque o erro de fase em estado estacionário não é zero.

A partir das colocações acima, neste trabalho é proposto: (1) a implementação do PLL de onda quadrada usando um banco de filtros adaptativos de atraso (filtro ADB) [23] baseado na estrutura em cascata de cancelamento de sinal por atraso (CDSC) [24–27] para resolver o problema do erro de fase, e (2) a implementação de estruturas de PLLs utilizando o controlador PR ideal para acrescentar robustez e melhorias na detecção da fase e frequência. Além disso, é proposto o projeto do controlador PR aplicado a PLLs.

#### 1.2 Objetivos

O objetivo desse trabalho é contribuir com o estudo de algoritmos de sincronização para conversores estáticos conectados à rede elétrica monofásica. Para isso, sendo necessário o desenvolvimento dos seguintes objetivos específicos:

- Propor o uso do filtro ADB na estrutura do PLL de onda quadrada para corrigir o problema do erro de fase quando o sinal da rede contêm harmônicos.

- Propor a implementação de estruturas de PLLs utilizando o controlador PR ideal para acrescentar robustez e melhorias na detecção da fase e frequência quando os PLLs estão submetidos a rede elétrica com presença de distorções.

- Propor uma metodologia de projeto para algoritmos de PLLs utilizando o controlador PR.

#### 1.3 Organização da Dissertação

Esta dissertação está organizada da seguinte forma:

- No Capítulo 2, são apresentadas discussões e esclarecimentos fundamentais sobre PLLs monofásicos. Inicialmente, é apresentada a estrutura básica de um PLL. Em seguida, o modelo linearizado de um PLL para pequenos sinais é visto. Depois uma metodologia de projeto é apresentada e por fim, algoritmos de PLLs monofásicos são analisados tendo seus fundamentos esclarecidos.

- No Capítulo 3, é apresentada a implementação do PLL de onda quadrada utilizando um filtro ADB. É analisado o impacto do filtro ADB sobre o harmônico fundamental, além da análise de estabilidade e resposta dinâmica do algoritmo. Depois, é realizado

- o projeto do filtro em estudo, e ao final, são realizadas simulações e experimentos para ilustrar conceitos e a operação do algoritmo apresentado.

- No Capítulo 4, é proposto a implementação do PLL clássico utilizando o controlador PR ideal, além disso é apresentado o projeto do algoritmo. Também é realizado um estudo da estabilidade e resposta dinâmica do PLL em questão. Ao final, são apresentadas simulações e experimentos com o objetivo de ilustrar conceitos e operações do algoritmo apresentado. Um estudo comparativo do PLL clássico com controlador PR frente ao PLL clássico com controlador PI é realizado.

- No Capítulo 5, é apresentado uma comparação de desempenho através de simulações e experimentos dos seguintes algoritmos monofásicos: PLL baseado na Transformação Inversa de Park (Park-PLL) utilizando os controladores PI e PR, o PLL baseado no Integrador Generalizado de Segunda Ordem (SOGI-PLL) e o Enhanced Phase Locked Loop (EPLL). Os algoritmos são testados para diferentes condições de rede. Neste mesmo Capítulo, os resultados simulados e experimentais são analisados e conclusões são obtidas a partir desta análise.

- No Capítulo 6, são apresentadas as conclusões e os trabalhos futuros.

### 2 Phase Locked Loop Monofásicos

#### 2.1 Introdução

Neste capítulo, são apresentados conceitos básicos sobre PLLs e estes conceitos são utilizados como base para a análise de diferentes algoritmos monofásicos. Além disso, é apresentado uma metodologia de projeto para PLLs e o modelo linearizado para pequenos sinais.

#### 2.2 Estrutura Básica de um PLL

Os algoritmos PLL são amplamente utilizados em aplicações como comunicações, computadores e eletrônicos modernos [28]. Eles podem gerar frequências estáveis sincronizadas com eventos periódicos externos, recuperar sinais relevantes de fontes distorcidas além de outras aplicações [28]. Um diagrama de blocos da estrutura PLL básica é ilustrado na Figura 2.1.

Figura 2.1 – Estrutura básica de um PLL.

O bloco PD tem como função a geração de um sinal de erro proporcional à diferença de fase entre o sinal de entrada  $\nu_i$ , e o sinal gerado internamente pelo PLL,  $\nu_o$ . O bloco LF apresenta uma característica de filtragem com função de remover distúrbios indesejáveis que possam afetar o comportamento do VCO. Tipicamente, este bloco é constituído por um controlador PI. Já o bloco VCO funciona como um oscilador interno do PLL, gerando um sinal senoidal na saída cuja frequência é deslocada de acordo com uma frequência central,  $\omega_c$ , em função da tensão fornecida pelo bloco LF.

A estrutura da Figura 2.1 é comum na maioria dos algoritmos de PLL, o que muda é apenas a estratégia de implementação de cada um dos blocos discutidos anteriormente. A seguir, é analisada a implementação de um PLL clássico considerando o cenário de uma rede monofásica.

#### 2.3 Equações Básica de um PLL

O diagrama de blocos do PLL clássico está ilustrado na Figura 2.2, sendo que os blocos referentes a cada estágio têm seus modelos de controle no domínio do tempo. Essa estrutura é de fundamental importância para a compreensão do funcionamento desse tipo de sistema, uma vez que estruturas mais elaboradas têm um funcionamento idêntico ao PLL clássico.

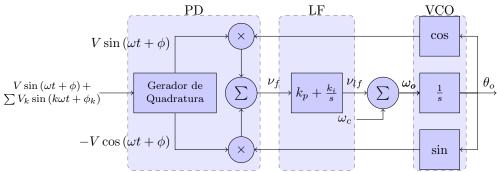

Figura 2.2 – Diagrama de blocos do PLL clássico.

Observa-se, da Figura 2.2, que o bloco PD é implementado por um simples multiplicador, o LF é baseado em um controlador PI e o VCO consiste em uma função senoidal cujo argumento é fornecido por um integrador. Considerando que o sinal aplicado na entrada do sistema seja dado por

$$\nu_i = A_1 \operatorname{sen}(\omega_1 t + \phi_1), \tag{2.1}$$

em que  $\omega_1$  representa a frequência fundamental e, o sinal gerado pelo VCO é dado por

$$\nu_o = \cos(\omega_o t + \phi_o), \tag{2.2}$$

o sinal de erro gerado pelo multiplicador no bloco PD pode ser escrito como

$$\nu_{f} = A_{1}k_{pd}\operatorname{sen}(\omega_{1}t + \phi_{1})\operatorname{cos}(\omega_{o}t + \phi_{o})$$

$$= \frac{A_{1}k_{pd}}{2} \left[ \underbrace{\operatorname{sen}((\omega_{1} - \omega_{o})t + (\phi_{1} - \phi_{o}))}_{\text{termos de baixa frequência}} + \underbrace{\operatorname{sen}((\omega_{1} + \omega_{o})t + (\phi_{1} + \phi_{o}))}_{\text{termos de alta frequência}} \right].$$

(2.3)

Considerando que os termos de alta frequência na saída do bloco PD são totalmente filtrados pelo bloco LF, restando apenas os termos de baixa frequência em (2.3), então o sinal de erro pode ser reescrito como

$$\nu_f = \frac{A_1 k_{pd}}{2} \operatorname{sen}((\omega_1 - \omega_o)t + (\phi_1 - \phi_o))$$

(2.4)

Considerando que o PLL entra em regime, isto é  $\omega_o \approx \omega_1$ , (2.4) pode ser simplificado obtendo

$$\nu_f = \frac{A_1 k_{pd}}{2} \operatorname{sen}(\phi_1 - \phi_o)$$

(2.5)

Observando (2.5), verifica-se que o sinal de erro produzido pelo bloco PD é não linear devido à presença da função senoidal. Contudo, quando o erro for muito pequeno,

isto é  $\phi_1 \approx \phi_o$ , a saída do bloco PD pode ser linearizada em torno de um ponto de operação, desde que a seguinte condição seja satisfeita:

$$\operatorname{sen}(\phi_1 - \phi_o) \approx \operatorname{sen}(\theta_1 - \theta_o) \approx \theta_1 - \theta_o$$

(2.6)

Portanto, em regime permanente, o termo relevante do erro é dado por:

$$\nu_f = \frac{A_1 k_{pd}}{2} (\theta_1 - \theta_o)$$

(2.7)

A equação (2.7) pode ser usada para representação do PLL através de um modelo linearizado para pequenos sinais. Por sua vez, a frequência média do VCO é determinada por:

$$\omega_o = (\omega_c + \Delta \overline{\omega}_o) = (\omega_c + k_{vco} \overline{\nu}_{lf}), \tag{2.8}$$

onde  $\omega_c$  representa a frequência central do VCO e depende da faixa de frequência a ser detectada pelo PLL. Considerando apenas as variações de pequenos sinais, a frequência no VCO pode ser dada por:

$$\tilde{\omega}_o = k_{vco} \tilde{\nu}_{lf}$$

(2.9)

Por fim, as variações de fase detectadas pelo PLL podem ser escritas como

$$\tilde{\theta}_o = \int \tilde{\omega}_o dt = \int k_{vco} \tilde{\nu}_{lf} dt$$

(2.10)

#### 2.4 Modelo Linearizado de um PLL para Pequenos Sinais

O modelo linearizado para pequenos sinais do PLL é de grande utilidade na análise quantitativa e na definição dos parâmetros do bloco LF do PLL. Aplicando a transformada de Laplace nas expressões desenvolvidas anteriormente e considerando  $k_{pd}=k_{vco}=1$  e  $\omega_c=0$ , o modelo para pequenos sinais do PLL pode ser dado de acordo com a ilustração da Figura 2.3.

Figura 2.3 – Modelo para pequenos sinais do PLL clássico.

Pela Figura 2.3, é observado que os sinais de saída dos blocos PD, LF e VCO são dados por

$$V_f(s) = \frac{A_1}{2} (\Theta_1(s) - \Theta_o(s)), \tag{2.11}$$

$$V_{lf}(s) = \frac{sK_p + K_i}{s} V_f(s),$$

(2.12)

$$\Theta_o(s) = \frac{1}{s} V_{lf}(s)$$

(2.13)

Considerando  $A_1=1$ , as funções de transferência de malha aberta e malha fechada podem ser escritas como

$$H_{ma}(s) = \left(\frac{K_p s + K_i}{s}\right) \left(\frac{1}{s}\right), \tag{2.14}$$

$$H_{mf}(s) = \frac{H_{ma}(s)}{1 + H_{ma}(s)},\tag{2.15}$$

$$H_{mf}(s) = \frac{K_p s + K_i}{s^2 + K_p s + K_i}. (2.16)$$

De acordo com (2.14) e (2.16) pode-se tirar algumas conclusões preliminares sobre o desempenho do PLL da Figura 2.2. A função de transferência de malha aberta do PLL possui um par de polos na origem do plano complexo, o que garante erro de regime permanente nulo para entradas em degrau na fase do sinal de entrada. Por sua vez, a função de transferência de malha fechada do PLL apresenta uma característica de filtragem passa-baixas de segunda ordem na detecção do ângulo de fase de entrada, que é uma característica muito útil para atenuar o erro de detecção de fase causado por possíveis ruídos e harmônicos de ordem elevada presentes no sinal de entrada [28].

Para o cálculo dos ganhos do controlador PI, pode-se comparar a função de transferência de malha fechada (2.16) por uma função de transferência de segunda ordem normalizada contendo um zero [29]:

$$H_{\theta}(s) = \frac{2\xi\omega_{n}s + \omega_{n}^{2}}{s^{2} + 2\xi\omega_{n}s + \omega_{n}^{2}},$$

(2.17)

em que,  $\omega_n$  representa a frequência natural de oscilação e  $\xi$  representa o fator de amortecimento, que varia usualmente entre 0 e 1.

Comparando (2.16) e (2.17) obtém-se

$$K_p = 2\xi\omega_n,\tag{2.18}$$

$$K_i = \omega_n^2 (2.19)$$

De acordo com [29], os parâmetros da função de transferência normalizada (2.17) podem-se correlacionar com a resposta no domínio do tempo, onde o tempo de estabelecimento para regime permanente é calculado como:

$$t_s = \frac{4,6}{\xi \omega_n},\tag{2.20}$$

$$\omega_n = \frac{4,6}{\xi t_s}. (2.21)$$

Fazendo a substituição de (2.21) em (2.18) e (2.19), obtém-se:

$$K_p = \frac{9, 2}{t_s},\tag{2.22}$$

$$K_i = \left(\frac{4,6}{\xi t_s}\right)^2. \tag{2.23}$$

De acordo (2.22) e (2.23), os ganhos do controlador PI podem ser calculados a partir do tempo de estabelecimento desejado para a malha fechada, de modo que o ganho proporcional ajusta a velocidade de resposta do PLL, pois quanto maior o ganho  $K_p$ , menor será o tempo de estabelecimento e mais rápida será a resposta do controlador. O ganho integral  $K_i$  ajusta o erro de regime permanente para que seja nulo.

É importante destacar que o valor do tempo de estabelecimento não deve ser muito pequeno, pois caso isso aconteça haverá uma banda passante grande, implicando em termos de alta frequência passando pelo bloco LF e com isso interferindo no desempenho do PLL. Logo o valor de  $t_s$  está diretamente relacionado a banda passante desejada para a malha fechada.

A banda passante de um sistema representa um intervalo de frequência no qual, o ganho em malha fechada está acima de -3 dB. De acordo com [28], a banda passante de (2.17) pode ser calculada da seguinte forma:

$$\omega_{cb} = \omega_n \left[ 1 + 2\xi^2 + \sqrt{(1 + 2\xi^2)^2 + 1} \right]^{1/2}, \qquad (2.24)$$

em que  $\omega_{cb}$  é a frequência de corte da banda passante.

Substituindo (2.21) em (2.24), resulta em:

$$\omega_{cb} = \frac{4.6}{\xi t_o} \left[ 1 + 2\xi^2 + \sqrt{(1 + 2\xi^2)^2 + 1} \right]^{1/2}.$$

(2.25)

De acordo com (2.25), verifica-se que quanto menor for o valor de  $t_s$ , maior será a banda passante de malha fechada do sistema, comprometendo assim a filtragem dos termos de alta frequência no bloco PD.

### 2.5 Metodologia de Projeto para um PLL

O PLL é um sistema complexo e difere na abordagem de projeto de outros circuitos. Por isso, é importante observar as diferentes etapas de projeto a fim de garantir que cada passo adiante seja baseado nos parâmetros corretos. É ilustrado na Figura 2.4 um fluxograma que descreve a metodologia de projeto do PLL.

Figura 2.4 – Fluxograma de projeto de um PLL [1].

A primeira etapa é a determinação dos requisitos iniciais do sistema. Apesar do fato de que a lista de requisitos pode ser extensa, recomenda-se iniciar o projeto dando ênfase a alguns parâmetros importantes, por exemplo:

- Frequência de saída;

- Tempo de bloqueio do PLL;

- Especificação de ruído de fase dentro e fora da largura de banda do loop;

- Erro de fase.

A segunda etapa é escolher a arquitetura, levando em consideração as vantagens e desvantagens de cada uma para a aplicação em questão. Depois disso, as especificações de cada bloco devem ser determinadas. Para esse processo, é útil usar simultaneamente fontes derivadas de publicações científicas, datasheets e experiência de projetos anteriores.

Após o levantamento de dados do sistema e dos blocos individuais, é recomendado o uso de softwares de simulações, por exemplo o Matlab, para criar modelos executáveis do sistema. A vantagem dessa abordagem é que o projetista tem controle total sobre o número de variáveis que são introduzidas no processo e nos modelos utilizados.

Depois de executar as simulações, caso as especificações do sistema não tenham sido alcançadas, deve-se voltar na etapa referente a determinação das especificações dos blocos, ficando nesse laço até que a simulação gere os resultados esperados. Quando a simulação atingir as especificações do sistema, é possível iniciar o projeto de cada bloco separadamente com alto nível de detalhe, utilizando sempre ferramentas de simulações, a fim de atingir os requisitos dos blocos levantados anteriormente.

Com os blocos projetados individualmente em alto nível de detalhes, a simulação do sistema é novamente realizada. Caso a simulação não ocorra como esperado, deve-se voltar a etapa da implementação dos blocos individuais. Se o resultado da simulação for compatível com as especificações do sistema, o fluxo de projeto é finalizado.

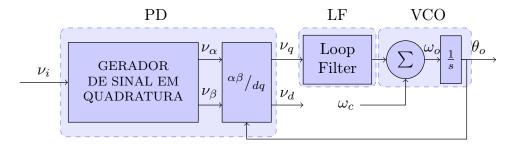

### 2.6 PLL Baseado na Transformação Inversa de Park

A detecção de fase baseado na geração de sinais em quadratura melhora o desempenho dinâmico de estruturas PLL [30]. A Figura 2.5 ilustra uma configuração de PLL semelhante à apresentada na Figura 2.2, com a diferença de que no bloco PD foi utilizado um gerador de sinal em quadratura, ao invés de um simples multiplicador como encontrado na estrutura do PLL clássico. De acordo com [28] essa mudança no bloco PD contorna de forma simples e eficiente as limitações do PLL clássico com relação a detecção de fase.

Figura 2.5 – PLL baseado na geração de sinais em quadratura.

Figura 2.6 – PLL com bloco PD em quadratura e transformação de Park.

O sinal do erro de fase produzido pelo bloco PD, neste caso, será expresso por

$$\nu_f = A_1 \operatorname{sen}(\omega_1 t + \phi_1) \cos(\omega_o + \phi_o) - A_1 \cos(\omega_1 t + \phi_1) \operatorname{sen}(\omega_o t + \phi_o)$$

$$= A_1 \operatorname{sen}((\omega_1 - \omega_o)t + (\phi_1 - \phi_o)) = A_1 \operatorname{sen}(\theta_1 - \theta_o).$$

(2.26)

Observa-se de (2.26) que a saída do bloco PD, diferente do PLL clássico, não contém termos de alta frequência, assim não prejudicando o desempenho do controlador PI no bloco LF, de modo que, em regime permanente ( $\omega_1 \approx \omega_o$ ), o sinal de saída estará totalmente sincronizado com o sinal de entrada quando o erro na saída do bloco PD for nulo.

A saída do bloco PD pode ser representada pela transformação de Park, obtendo também uma nova representação para o modelo apresentado na Figura 2.5. A transformação de Park consiste em converter um sistema do referencial estacionário  $\alpha\beta$  em um sistema de referencial girante síncrono dq, cujas componentes resultantes são quantidades contínuas. A transformação direta de Park é representada por:

$$\begin{bmatrix} \nu_d \\ \nu_q \end{bmatrix} = \begin{bmatrix} \cos(\theta_o) & \sin(\theta_o) \\ -\sin(\theta_o) & \cos(\theta_o) \end{bmatrix} \begin{bmatrix} \nu_\alpha \\ \nu_\beta \end{bmatrix}. \tag{2.27}$$

O novo diagrama para o PLL baseado em sinais em quadratura é mostrado na Figura 2.6. Considerando uma entrada da forma  $\nu = A_1 \operatorname{sen}(\theta_1) = A_1 \operatorname{sen}(\omega_1 t + \phi_1)$ , a saída do gerador de sinal em quadratura pode ser expressa por

$$\nu_{(\alpha\beta)} = \begin{bmatrix} \nu_{\alpha} \\ \nu_{\beta} \end{bmatrix} = V \begin{bmatrix} \operatorname{sen}(\theta_{1}) \\ -\cos(\theta_{1}) \end{bmatrix}$$

(2.28)

E para um PLL sincronizado ( $\omega_1 \approx \omega_o$ ), aplicando a transformação de Park resulta em

$$\nu_{(dq)} = \begin{bmatrix} \nu_d \\ \nu_q \end{bmatrix} = A_1 \begin{bmatrix} \sec(\theta_1 - \theta_o) \\ -\cos(\theta_1 - \theta_o) \end{bmatrix}. \tag{2.29}$$

Em sistemas trifásicos, nos quais existem três tensões de fase, o bloco gerador de sinais em quadratura, explicado anteriormente, pode ser implementado utilizando a transformação de Clarke [31–34]. No entanto, em sistemas monofásicos, onde há apenas

um sinal de fase, a transformação de Clarke não pode ser utilizada. Existem na literatura varias formas de contornar esse problema, uma delas é utilizando a transformação inversa de Park representada por (2.30). Na Figura 2.7 é ilustrado o PLL baseado na transformação inversa de Park.

Figura 2.7 – PLL baseado na transformação inversa de Park.

$$\nu_{(\alpha\beta)} = \begin{bmatrix} \nu_{\alpha} \\ \nu_{\beta} \end{bmatrix} = V \begin{bmatrix} \cos(\theta_{o}) & -\sin(\theta_{o}) \\ \sin(\theta_{o}) & \cos(\theta_{o}) \end{bmatrix} \begin{bmatrix} \nu_{d} \\ \nu_{q} \end{bmatrix}. \tag{2.30}$$

Pode-se observar da Figura 2.7 que dois filtros passa baixa (FPB) são usados para atenuar as oscilações quando os sinais de entrada da transformação de Park  $\nu_i$  e  $\nu_\beta'$  não estão em quadratura e, assim, garantir que os sinais de saída da transformação inversa de Park  $\nu_\alpha'$  e  $\nu_\beta'$  estejam em quadratura, embora  $\nu_i$  e  $\nu_\alpha'$  não estejam em fase se o PLL não estiver perfeitamente sincronizado. À medida que o PLL rastreia o ângulo de fase do sinal de entrada,  $\nu_i$  entrará em fase com  $\nu_\alpha'$  e em quadratura com  $\nu_\beta'$ . A função de transferência dos filtros pode ser representada por:

$$H_F(s) = \frac{\omega_f}{s + \omega_f},\tag{2.31}$$

onde  $\omega_f$  representa a frequência de corte do filtro e pode ser calculada como  $\omega_f = 2\xi\omega$ .

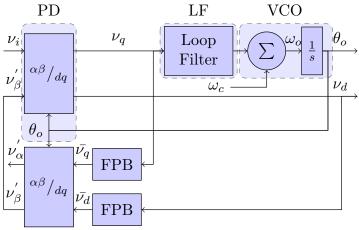

#### 2.7 PLL Baseado no Integrador Generalizado de Segunda Ordem

Na Figura 2.8 é ilustrado um sistema ortogonal que foi inicialmente apresentado em [30]. Como sinais de saída, são geradas duas ondas senoidais ( $\nu'$  e  $q\nu'$ ) com uma mudança de fase de 90°. A componente  $\nu'$  apresenta mesma fase e magnitude da componente fundamental do sinal de entrada  $\nu_i$ .

A estrutura apresentada é baseada no SOGI, que é definido como [30, 35–37]:

$$GI(s) = \frac{\omega_o s}{s^2 + \omega_o^2},\tag{2.32}$$

Figura 2.8 – Estrutura do sistema ortogonal.

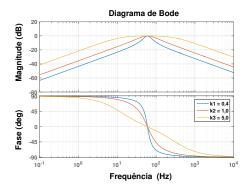

Figura 2.9 – Diagrama de Bode da função de transferência  $H_d(s)$  para diferentes valores de k.

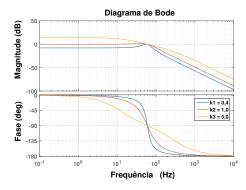

Figura 2.10 – Diagrama de Bode da função de transferência  $H_q(s)$  para diferentes valores de k.

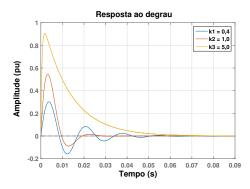

Figura 2.11 – Resposta ao degrau da função de transferência  $H_d(s)$  para diferentes valores de k.

onde  $\omega_o$  representa a frequência de ressonância do SOGI.

As funções de transferência de malha fechada  $H_d(s) = \frac{\nu'(s)}{\nu_i(s)}$  e  $H_q(s) = \frac{q\nu'(s)}{\nu_i(s)}$  da estrutura apresentada na Figura 2.8 são definidas como:

$$H_d(s) = \frac{\nu'(s)}{\nu_i(s)} = \frac{k\omega_o s}{s^2 + k\omega_o s + \omega_o^2}$$

(2.33)

$$H_q(s) = \frac{q\nu'(s)}{\nu_i(s)} = \frac{k\omega_o^2}{s^2 + k\omega_o s + \omega_o^2},$$

(2.34)

onde k afeta a largura de banda do sistema de malha fechada.

Os diagramas de Bode das funções de transferência  $H_d(s)$  e  $H_q(s)$  para uma frequência ressonante de 60Hz e diferentes valores de k são ilustrados nas Figuras 2.9

e 2.10. Observando o gráfico da magnitude nas Figuras 2.9 e 2.10, verifica-se que há um ganho unitário para sinais cuja frequência angular tem o mesmo valor de  $\omega_o$  ajustado nos ganhos do SOGI. Para frequências superiores à frequência angular de ajuste, observa-se que há um decaimento no ganho dos sinais, o que explica a atuação do SOGI como um filtro para possíveis harmônicos presentes no sinal de entrada. Observa-se também que o desempenho da filtragem aumenta com a diminuição dos valores de k, porém esta diminuição acarreta no aumento do tempo de estabelecimento do sistema como pode ser observado na Figura 2.11. Para a resposta da Figura 2.11 foi utilizado, uma entrada do tipo degrau na função de transferência  $H_d(s)$ . Verifica-se dos diagramas de fase que os sinais de saída estarão sempre em quadratura.

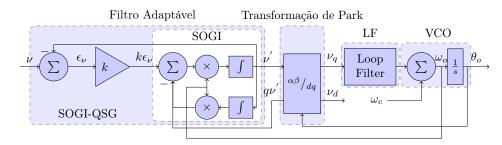

O sistema ortogonal (SOGI-QSG) da Figura 2.8 pode ser aplicado diretamente para implementar um PLL baseado na geração de sinais em quadratura, como é ilustrado na Figura 2.12, essa estrutura é conhecida como SOGI-PLL [28,30]. Este sistema tem uma dupla realimentação que é responsável por fornecer o ângulo de fase para a transformação de Park e a frequência central para o SOGI-QSG.

Figura 2.12 – Estrutura do SOGI-PLL.

O princípio de funcionamento do SOGI-PLL é similar ao que já foi apresentado para outras estruturas. Em regime permanente ( $\omega_1 \simeq \omega_o$ ), o bloco SOGI-QSG gera os sinais em quadratura que por sua vez irá passar pelo bloco da transformação de Park onde ocorrerá a mudança do referencial estacionário  $\alpha\beta$  para o referencial girante dq. Quando  $\nu_q = 0$  o vetor tensão de entrada irá sobrepor o eixo d e na saída do PLL é rastreado o ângulo  $\theta_o = \theta_1 - \frac{\pi}{2}$ .

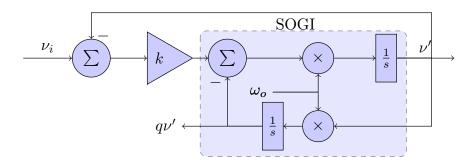

#### 2.8 O Enhanced Phase Locked Loop

O EPLL é um algoritmo de sincronização que apresenta características diferentes se comparado ao PLL convencional. A principal diferença nessa configuração de PLL está na presença de um novo esquema do detector de fase, que é baseado na teoria do Filtro Notch Adaptativo (ANF).

Na Figura 2.13 é ilustrado a estrutura do EPLL. Nela observa-se que o bloco PD proposto é basicamente uma configuração do ANF. O funcionamento do EPLL pode ser

compreendido como a unificação das propriedades do ANF com as propriedades do PLL.

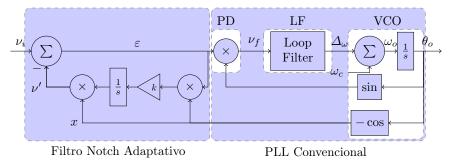

Figura 2.13 – Diagrama de blocos básico da estrutura EPLL.

A saída do bloco ANF da Figura 2.13 é nula quando a frequência e fase do sinal de referência gerado pelo VCO,  $x = cos(\theta_o)$ , correspondem aos do sinal de entrada  $\nu_i$ . Como resultado, as oscilações do sinal de saída do multiplicador do bloco PD são completamente canceladas e o ângulo de fase do sinal de entrada é detectado corretamente pelo PLL convencional. Vale ressaltar, no entanto, que há uma defasagem de 90° entre  $\theta$  e  $\theta_o$  quando o PLL entrar em regime permanente, isto é  $\theta_o = \theta - \frac{\pi}{2}$ , devido ao efeito do multiplicador do bloco PD [28].

A amplitude da componente fundamental do sinal de entrada é obtida através da realimentação negativa  $\nu'$  no bloco ANF. Quando o sistema entra em regime permanente, o erro da saída do sinal intermediário  $\varepsilon$  tende para zero, desta forma a amplitude da componente fundamental do sinal de entrada pode ser obtida através deste sinal de realimentação. O ganho k é responsável por controlar a velocidade de convergência de  $\nu'$ .

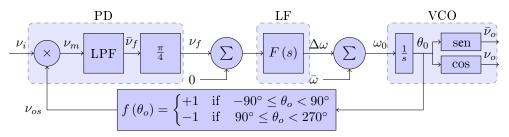

#### 2.9 PLL Baseado na Realimentação em Onda Quadrada

Na Figura 2.14 é ilustrado o PLL de onda quadrada (PLLOQ) monofásico. É observada uma semelhança com o PLL clássico apresentado na Figura 2.2, com a principal diferença de que o bloco PD é realimentado por uma onda quadrada (Figura 2.15), ao invés de usar uma tensão de  $\nu_o = \cos(\omega_o t + \phi_o) = \cos(\theta_o)$ . O sinal  $\nu_{os}$  é obtido na saída do gerador de onda quadrada e depende do ângulo de fase  $\theta_o$  de acordo com a função  $f(\theta_o)$  definido na Figura 2.14. Uma característica dessa estrutura é que a avaliação das funções sen e cos é computada fora do loop do PLL e não influência seu desempenho [22]. Uma vantagem de ter um VCO em onda quadrada é que o bloco PD se torna uma simples operação "multiplica por um" que pode ser implementado de forma simples. O bloco LPF na Figura 2.14 é implementado usando um filtro MAF [8,38].

Expressando  $\nu_{os}$  através das séries de Fourier

$$\nu_{os} = -\frac{4}{\pi} \sum_{j=1}^{\infty} (-1)^j \frac{\cos[(2j-1)\omega_o t + (2j-1)\phi_o]}{2j-1}$$

(2.35)

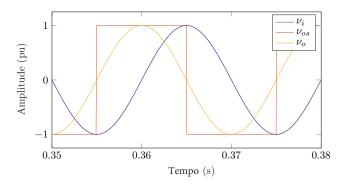

Figura 2.14 – Diagrama de blocos básico para o PLL de onda quadrada.

Figura 2.15 – Onda quadrada e tensão de saída  $\nu_o$  do PLL.

e considerando que a tensão de entrada do PLL de onda quadrada seja dada por uma tensão senoidal sem distorções,  $\nu_i = A_1 \operatorname{sen}(\omega_1 t + \phi_1)$ , a saída do multiplicador  $\nu_m = \nu_i \cdot \nu_{os}$  pode ser representada por (2.36), onde a mesma apresenta uma componente CC e termos oscilantes.

$$\nu_m = -\frac{2}{\pi} \left\{ \sum_{j=1}^{\infty} \frac{(-1)^j A_1}{2j-1} \left\{ \begin{array}{l} \operatorname{sen}[(2-2j)\omega_1 t + \phi_1 - (2j-1)\phi_o] + \\ + \operatorname{sen}[2j\omega_1 t + \phi_1 + (2j-1)\phi_o] \end{array} \right\} \right\}.$$

(2.36)

Supondo que os termos de alta frequência de  $\nu_m$  sejam atenuados pelo bloco LPF, o sinal de filtragem  $\overline{\nu_f}$  é representado por

$$\overline{\nu_f} = \frac{4}{\pi} \frac{A_1}{2} \operatorname{sen}(\phi_1 - \phi_o),$$

(2.37)

onde é observado, uma semelhança com o sinal de (2.5), exceto por causa do ganho  $4/\pi$ .

Quando  $\overline{\nu_f}$  for muito pequeno, isto é  $\phi_1 \approx \phi_o$ ,  $\operatorname{sen}(\phi_1 - \phi_o) \approx \phi_1 - \phi_o$  e consequentemente

$$\overline{\nu_f} = \frac{4}{\pi} \frac{A_1}{2} (\phi_1 - \phi_o). \tag{2.38}$$

Considerando que a tensão de entrada contêm componentes harmônicas

$$\nu_i = \sum_{k=1}^{\infty} A_k \operatorname{sen}(k\omega_1 t + \phi_k), \tag{2.39}$$

a saída do multiplicador pode ser representa por (2.40), onde é notado a presença de uma componente CC e termos oscilantes. Supondo que o bloco LPF atenua os termos de alta frequência de (2.40), a saída do bloco PD é representada por (2.41).

$$\nu_m = -\frac{2}{\pi} \left\{ \sum_{k=1}^{\infty} \sum_{j=1}^{\infty} \frac{(-1)^j A_k}{2j-1} \left\{ \begin{array}{l} \operatorname{sen}[(k-2j+1)\omega_1 t + \phi_k - (2j-1)\phi_o] + \\ + \operatorname{sen}[(k+2j-1)\omega_1 t + \phi_k + (2j-1)\phi_o] \end{array} \right\} \right\}, \quad (2.40)$$

$$\overline{\nu_f} = \frac{2}{\pi} \left[ A_1 \operatorname{sen}(\phi_1 - \phi_o) - \frac{A_3}{3} \operatorname{sen}(\phi_3 - 3\phi_o) + \dots - \frac{(-1)^j A_k}{2j - 1} \operatorname{sen}[\phi_{2j - 1} - (2j - 1)\phi_o] \right] \cdot (2.41)$$

Comparando as expressões (2.37) e (2.41), verifica-se que a inclusão de harmônicos em  $\nu_i$  resulta em novos termos de componentes CC. No entanto, supondo que o controlador force  $\nu_f$  e  $\overline{\nu_f}$  para zero, de acordo com (2.41), a inclusão de harmônicos em  $\nu_i$  pode levar a  $\phi_1 - \phi_o \neq 0$ . Isso explica o erro de fase para o PLL de onda quadrada operando com  $\nu_i$  distorcido. Em [22] é mostrado um exemplo e revisto aqui, onde é considerado uma entrada  $\nu_i$  contendo a presença da terceira harmônica com amplitude de  $A_3 = 0, 3A_1$ , e  $\operatorname{sen}(\phi_3 - 3\phi_o) = \pm 1$ . Isto resulta em  $\overline{\nu_f} = \frac{2}{\pi}[A_1 \operatorname{sen}(\phi_1 - \phi_o) \pm \frac{0,3}{3}A_11]$ . Quando o PLL está travado,  $\overline{\nu_f} = 0$ , o que resulta em um erro de fase igual a  $\phi_1 - \phi_o = \operatorname{sen}^{-1}(\pm 0, 3/3) = \pm 5,73^\circ$ . No capítulo 3, é apresentada uma solução para esse problema.

### 2.9.1 Filtro de Média Móvel

Os MAFs são filtros de resposta de impulso finito de fase linear (FIR), que podem atuar como filtros passa baixa ideal, se determinadas condições persistirem [8,38,39]. Eles são econômicos em termos de carga computacional e fáceis de implementar na prática.

O MAF com um sinal de entrada y(t) e um sinal de saída  $\bar{y}(t)$  pode ser descrito no domínio de tempo contínuo por

$$\bar{y}(t) = \frac{1}{T_j} \int_{t-T_j}^t y(\tau) d\tau,$$

(2.42)

onde  $T_j$  representa o tamanho da janela. A partir de (2.42), a função de transferência do MAF pode ser obtida como:

$$H_{MAF}(s) = \frac{\bar{y}(s)}{y(s)} = \frac{1 - e^{-T_j s}}{T_j s}.$$

(2.43)

Observa-se da função de transferência (2.43) que quanto maior o comprimento de janela, mais lenta será a resposta transitória do MAF.

Substituindo  $s=j\omega$  em (2.43), as expressões de magnitude e fase do MAF podem ser dadas por:

$$H_{MAF}(j\omega) = \left| \frac{\operatorname{sen}(\omega T_j/2)}{\omega T_j/2} \right| \angle - \omega T_j/2$$

(2.44)

De (2.44), verifica-se que, o MAF fornece ganho nulo nas frequências  $f = n/T_j$  (n = 1,2,3,...) em hertz e ganho de unidade na frequência zero. Isso significa que o MAF passa a componente CC e bloqueia completamente as componentes de frequência de múltiplos inteiros de  $1/T_j$  em hertz [8].

Para implementar o filtro MAF na prática, é necessária uma definição de tempo discreto. Assumindo que o tamanho da janela do MAF contém N amostras (N sendo

um número inteiro) do seu sinal de entrada, ou seja,  $T_j = NT_s$  onde  $T_s$  é o tempo de amostragem, a descrição de tempo discreto do filtro MAF pode ser obtida, com base em (2.42),

$$\bar{y}(k) = \frac{1}{N} \sum_{i=0}^{N-1} y(k-1)$$

(2.45)

onde y(k) é a amostra atual.

Escrevendo (2.45) no domínio Z temos:

$$\bar{Y}(z) = H_{MAF}(z)Y(z)

= \frac{1}{N}(Y(z) + z^{-1}Y(z) + \cdots z^{-(N-1)}Y(z))

= \left(\frac{1}{N}\sum_{i=0}^{N-1} z^{-i}\right)Y(z)

= \frac{1}{N}\frac{1 - z^{-N}}{1 - z^{-1}}Y(z).$$

(2.46)

A equação (2.46) representa a função discreta do MAF, onde N determina a ordem do filtro.

## 2.10 Conclusões Parciais

Neste capítulo, foram apresentados os conceitos básicos e principais parâmetros dos algoritmos de PLLs monofásicos. Além disso, foram apresentadas as modelagens de cinco algoritmos de PLL, sendo estes: PLL clássico, Park-PLL, SOGI-PLL, EPLL e PLL de onda quadrada. Foi visto, uma metodologia para projetar algoritmos de PLLs e o modelo linearizado do PLL para pequenos sinais, sendo este último, útil para projetar ganhos para o controlador utilizado no loop filter.

## 3 Utilização de Banco de Filtros Adaptativos de Atraso em Algoritmo Phase Locked Loop

## 3.1 Introdução

Neste capítulo, é apresentada a estrutura do PLL de onda quadrada utilizando o filtro ADB. É explicado o funcionamento do filtro ADB e como realizar seu projeto para a eliminação seletiva de harmônicos. Além disso, é apresentada uma análise da estabilidade e resposta dinâmica do PLL de onda quadrada e do PLL de onda quadrada com filtro ADB. Resultados de simulações e experimentais são realizados para validar as abordagens teóricas.

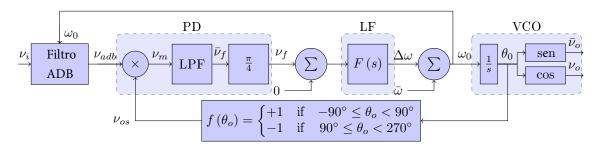

### 3.2 Estrutura do PLL com Filtro ADB

Conforme discutido na seção 2.9, se  $\nu_i$  e  $\nu_{os}$  tiverem harmônicos de mesma ordem, eles contribuem para a componente CC de  $\nu_m$  resultando em um erro de fase. Uma solução para isto, consiste em eliminar todos os harmônicos relevantes que existem na tensão de entrada  $\nu_i$ . Para isto é inserido um filtro ADB na estrutura do PLL de onda quadrada como ilustrado na Figura 3.1 [40].

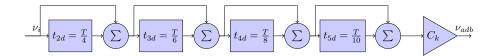

Figura 3.1 – Diagrama de blocos básico para o PLL de onda quadrada com filtro ADB.

O filtro ADB consiste em vários blocos de filtros, cada um com a função de eliminar um harmônico específico conforme ilustra a Figura 3.2. A harmônica de k - ésima ordem (k=2,3,...) que deve ser eliminada é adicionada à sua própria imagem atrasada para T/2k, onde T é o período da componente fundamental do sinal da rede. Então, se o terceiro harmônico deve ser eliminado (k=3), ele deve ser adicionado à sua própria imagem atrasada de  $t_{3d}=T/6$ , para a eliminação da quarta harmônica é necessário um atraso de  $t_{4d}=T/8$ , e assim por diante.

Figura 3.2 – Diagrama de blocos básico do filtro ADB para eliminação seletiva de harmônicos.