## Universidade Federal de Campina Grande

Centro de Engenharia Elétrica e Computação

Departamento de Engenharia Elétrica

Laboratoire TIMA

Équipe AMfoRS

## Self-Adaptative Approximate System-On-a-Chip

## SysAx Project

Development of the Hardware Platform

#### **Autor:**

Gabriel Villanova N. Magalhães

Campina Grande, Paraíba Data: 2018

## Self-Adaptative Approximate System-On-a-Chip

## Development of the Hardware Platform

#### Autor:

Gabriel Villanova Novaes Magalhães

#### Orientador:

Prof. D.Sc. Gutemberg Gonçalves dos Santos Júnior

Prof. D.Sc. Gutemberg Gonçalves dos Santos Júnior

Prof. D.Sc. Marcos Ricardo Alcântara Morais

Componentes da banca

Relatório de estágio obrigatório apresentado no curso de Engenheria Elétrica, como requisito parcial para obtenção do título de Bacharel em Engenheria Elétrica na Universidade Federal de Campina Grande (UFCG).

Campina Grande, Paraíba Data: 2018

Resumo: Approximate Computing é um tema bastante recente e que tem tomado a atenção dos pesquisadores, principalmente pelo aumento de softwares do tipo RMS e aplicações IoT, que processam dados com erro intrínseco, permitindo portanto processamento computacional de forma aproximada. Entretanto, a pesquisa nessa área ainda precisa de muito avanço, um deles, é construir uma plataforma computacional que permita testar ideias de AxC com bastante produtividade, em todo o espectro da Engenharia da Computação, do transistor aos Sistemas Operacionais Multiprocessados. O objetivo principal desse trabalho é estabelecer uma plataforma para que os pesquisadores da área possam testar suas ideias, treinar pessoas e avançar na pesquisa. Para isso, várias plataformas computacionais gratuitas foram avaliadas, sendo a mais promissora, o projeto da University of Berkeley, o Rocket Chip SoC Generator. Esse projeto, apesar de bastante completo para o que a pesquisa demanda, não possui uma documentação que permita entender e usar a plataforma e toda a sua capacidade de forma produtiva. Esse trabalho cria uma documentação abordando de forma gradativa quase tudo que essa plataforma oferece. No final, todo o conhecimento adquirido é usado para implementar e testar um Coprocessador na plataforma com técnica de Computação Aproximada.

Palavras-chave: Computação Aproximada, Engenharia da Computação, RISC-V, Rocket Chip, Chisel, FIR.

Abstract: Approximate Computing is a very recent issue that has been attracting the attention of the researchers, mainly due to the increase of RMS software and IoT applications, which process data with intrinsic error, thus allowing computational processing of approximate form. However, the research in this area still needs a lot of progress, one of them, is to build a computational platform that allows to test ideas of AxC with enough productivity, in the entire spectrum of Computer Engineering, from the transistor to Multiprocessed Operating Systems. The main objective of this work is to establish a platform for researchers in the field to test their ideas, train people and advance research. To this end, several free computing platforms have been evaluated, the most promising being the University of Berkeley's the Rocket Chip SoC Generator. This project, although quite complete for what the research demands, does not have documentation that allows to understand and use the platform and all its capacity in a productive way. This work creates documentation by gradually addressing almost everything that this platform offers. In the end, all knowledge acquired is used to implement and test a Coprocessor on the platform with Approximate Computing technique.

**Keywords**: Approximate Computing, Computer Engineering, RISC-V, Rocket Chip, Chisel, FIR.

"Eu dedico esse trabalho primeiramente a Deus, pois sem Ele nada disso seria possível. Aos meus pais, George e Angela, que sempre acreditaram no meu potencial, possibilitando a realização do sonho de me tornar Engenheiro. A minha namorada Mirtys, por todos os incentivos e cuidados. E a todos os meus professores, em especial, o Prof. Gutemberg Júnior e Prof. Marcos Morais, por me mostrar, de todas as formas, o caminho da excelência."

# Lista de Figuras

| 1  | Logo TIMA                                                                 | 2  |

|----|---------------------------------------------------------------------------|----|

| 2  | AMfoRS                                                                    | 3  |

| 3  | Qualidade de imagem com aritmética exata, aproximação dos 8 bits LSB e    |    |

|    | implementação de largura de bit reduzida (fonte: [1])                     | 6  |

| 4  | AxC                                                                       | 9  |

| 5  | Compilador gerando códigos para executar parte em Processador parte em    |    |

|    | Unidade de Processamento Neural (Fonte: [3])                              | 10 |

| 6  | Exemplo de processador com circuitos precisos e não precisos (Fonte: [3]) | 11 |

| 7  | Somador de precisão configurável (Fonte: [3])                             | 12 |

| 8  | Logo PULP-platform                                                        | 13 |

| 9  | Arquitetura do PULP                                                       | 14 |

| 10 | Arquitetura simplificada do PULPino.                                      | 15 |

| 11 | Arquitetura simplificada do PULPissimo                                    | 16 |

| 12 | Logo Nios II                                                              | 17 |

| 13 | IP MicroBlaze                                                             | 18 |

| 14 | Visão geral dos componentes do Rocket Chip                                | 19 |

| 15 | Logo lowRISC                                                              | 21 |

| 16 | Arquitetura simplificada lowRISC                                          | 21 |

| 17 | Logo OpTiMSoC                                                             | 22 |

| 18 | Ecossistema do Rocket Chip                                                | 25 |

| 19 | Componentes do SoC Rocket Chip [14]                                       | 26 |

| 20 | Visão geral da arquitetura do Rocket Chip                                 | 27 |

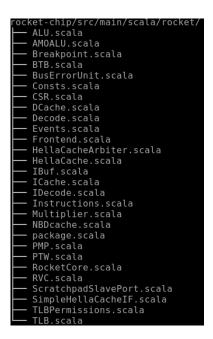

| 21 | Diretórios das implementações dos componentes de hardware do Rocket Chip. | 28 |

| 22 | Implementação Chisel do Rocket Tile                                       | 30 |

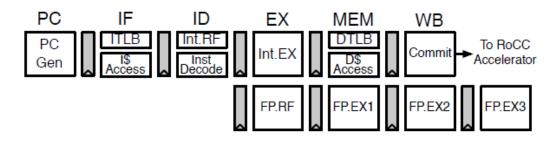

| 23 | The Rocket Core pipeline                                                  | 31 |

| 24 | Códigos dos componentes do Rocket Core                                    | 32 |

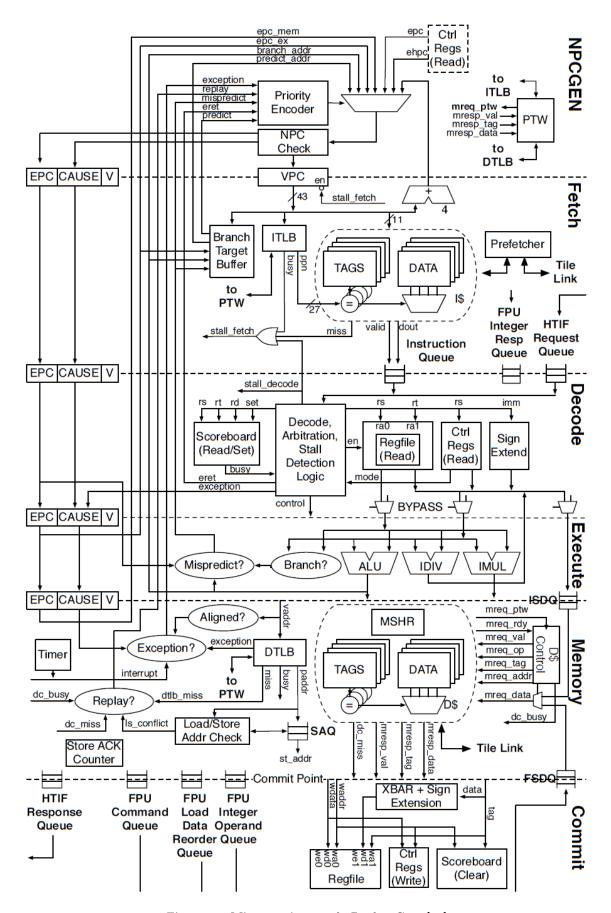

| 25 | Microarquitetura do Rocket Core [21]                                      | 35 |

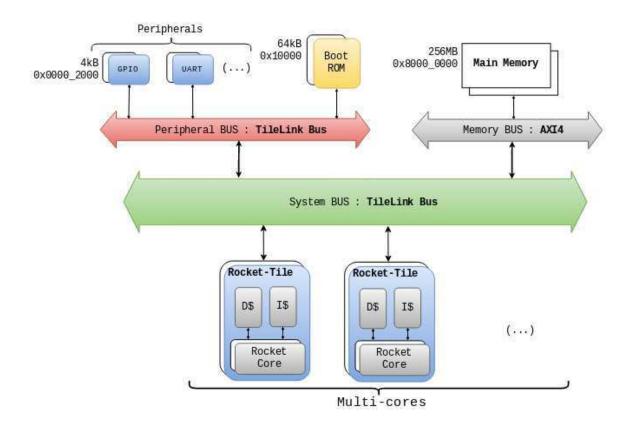

| 26 | Arquitetura de hierarquia de memória do Rocket Chip simplificada          | 37 |

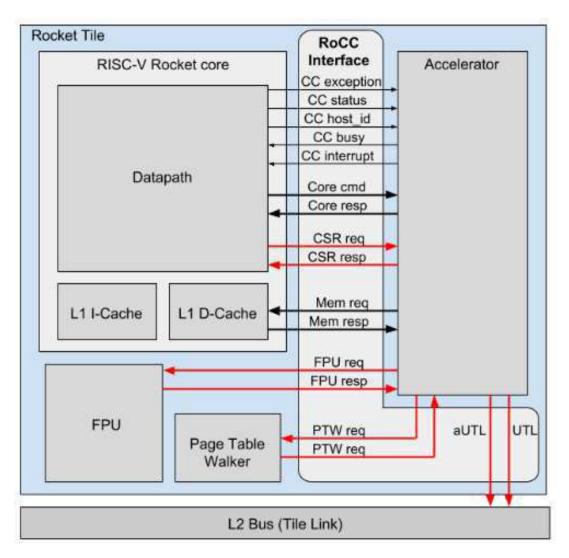

| 27 | Rocket Custom Coprocessor Interface (fonte: [24])                         | 39 |

| 28 | RoCC instruction format                                                   | 41 |

| 29 | Módulos CLINT e PLIC conectados ao Rocket Core [23]                       | 51 |

| 30 | Mapa de Memória do Módulo CLINT, fonte [23]                               | 53 |

| 31 | Mapa de Memória do Módulo PLIC em sistema 64 bits, fonte [23]             | 54 |

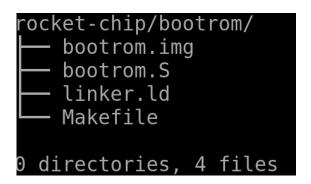

| 32 | Códigos do bootloader do Rocket Chip                                      | 56 |

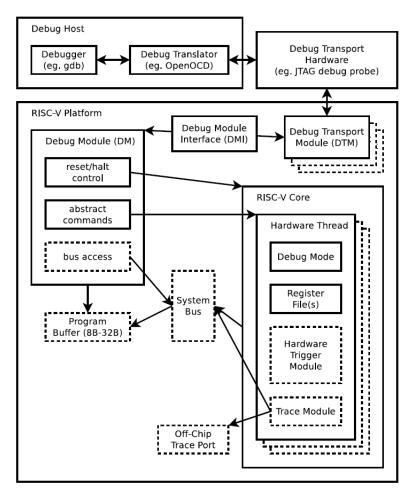

| 33 | Arquitetura do sistema de depuração do RISC-V                             | 59 |

| 34 | Arquivos de implementação do DTM                                          | 60 |

| 35 | Arquivos de implementação do JTAG                                         | 60 |

| 36 | Logo Chisel                                                       |

|----|-------------------------------------------------------------------|

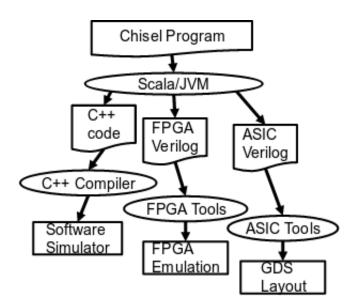

| 37 | Fluxo de compilação de um programa Chisel                         |

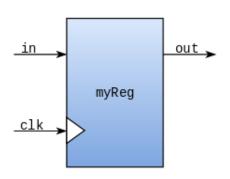

| 38 | Registrador p/ Exemplo 1                                          |

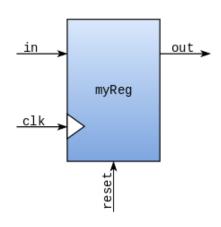

| 39 | Registrador p/ Exemplo 2                                          |

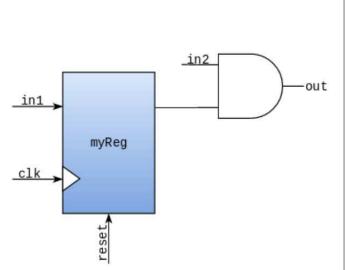

| 40 | Registrador p/ Exemplo 3                                          |

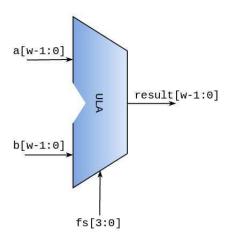

| 41 | ULA para exemplo com condicional                                  |

| 42 | Circuito meio somador                                             |

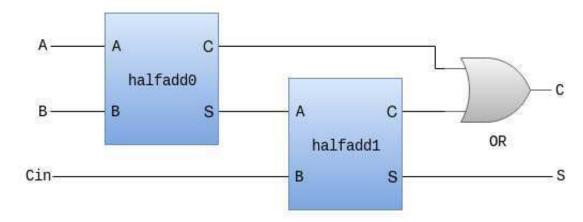

| 43 | Circuito somador completo usando dois meio somadores 81           |

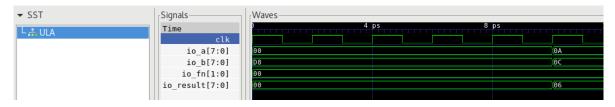

| 44 | Waveform do teste da ULA                                          |

| 45 | Infraestrutura de diretórios p/ projetos Chisel                   |

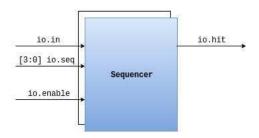

| 46 | RTL Identificador de Sequência                                    |

| 47 | FSM para Identificador de Sequência                               |

| 48 | Diretório desenvolvimento projeto identificador de sequências     |

| 49 | Waveform 1 testbench FSM                                          |

| 50 | Waveform 2 testbench FSM                                          |

| 51 | Fluxo de compilação cruzada RISC-V                                |

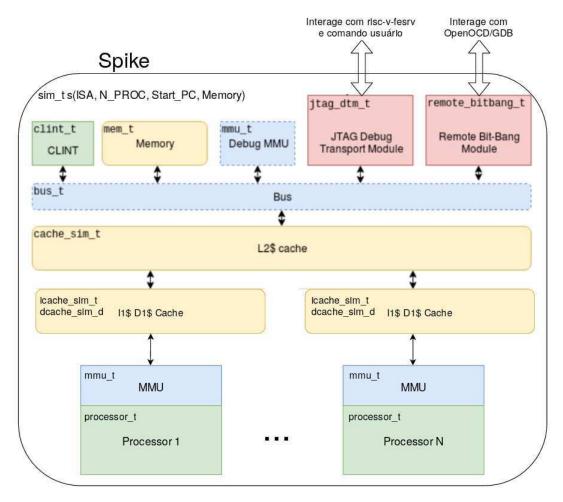

| 52 | Arquitetura do model de simulação Spike                           |

| 53 | Árvore de arquivos para compilação cruzada                        |

| 54 | Saída de compilação cruzada do exemplo Spike                      |

| 55 | Mapa de endereços gerados com implementação do RoccExConfig 103   |

| 56 | DTS do exemplo RoccExConfig - A                                   |

| 57 | DTS do exemplo RoccExConfig - B                                   |

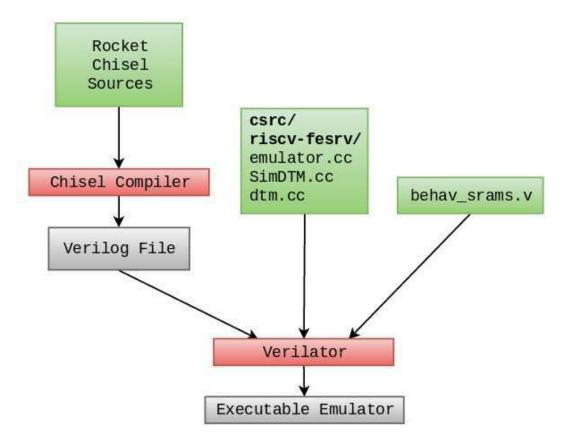

| 58 | Fluxo de geração do emulator                                      |

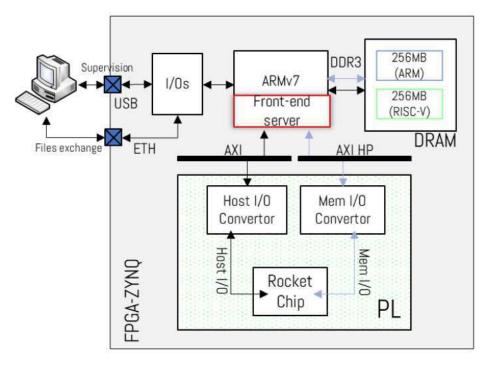

| 59 | Interface de acesso ao SoC Rocket Chip                            |

| 60 | Arquitetura do Rocket Chip Tethered                               |

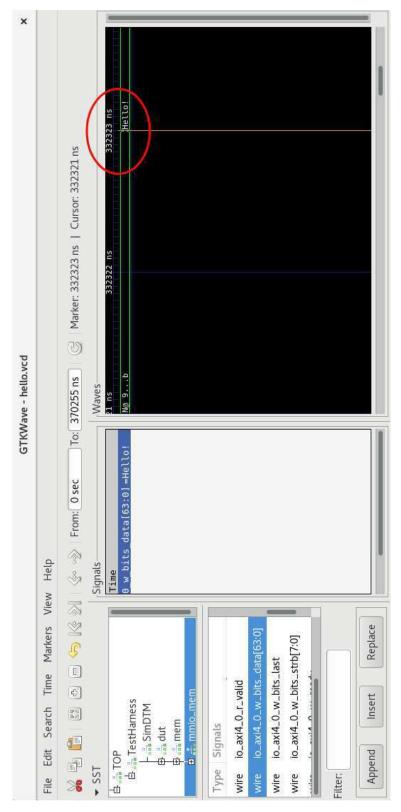

| 61 | Verificando mensagem escrita na região de memória MMIO            |

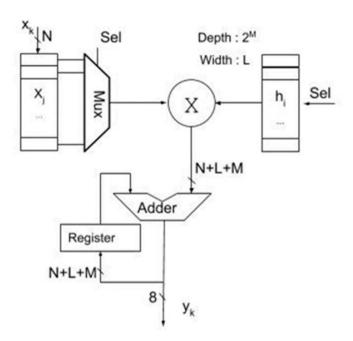

| 62 | Arquitetura de Filtro FIR Serial. Fonte: [40]                     |

| 63 | Arquitetura de Filtro Serial FIR AxC                              |

| 64 | Interface do componente FIR Serial AxC                            |

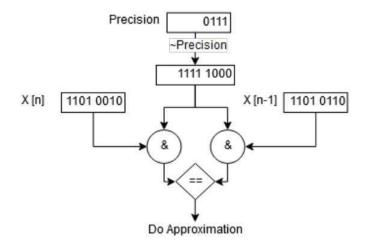

| 65 | Arquitetura do circuito comparador do FIR Serial AxC              |

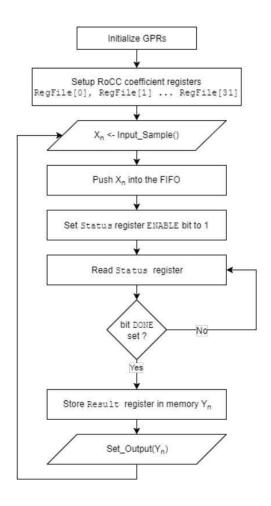

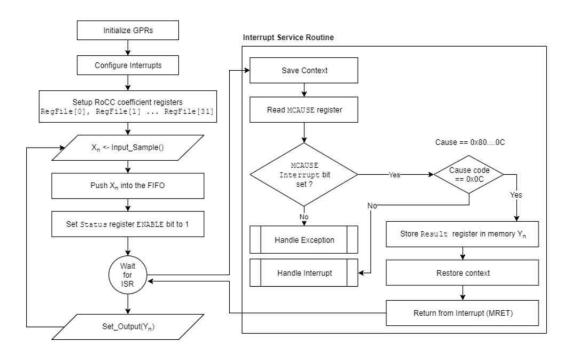

| 66 | Modelo de programação para o RoCC FIR AxC, sem interrupção 120    |

| 67 | Modelo de programação para o RoCC FIR AxC, com interrupção        |

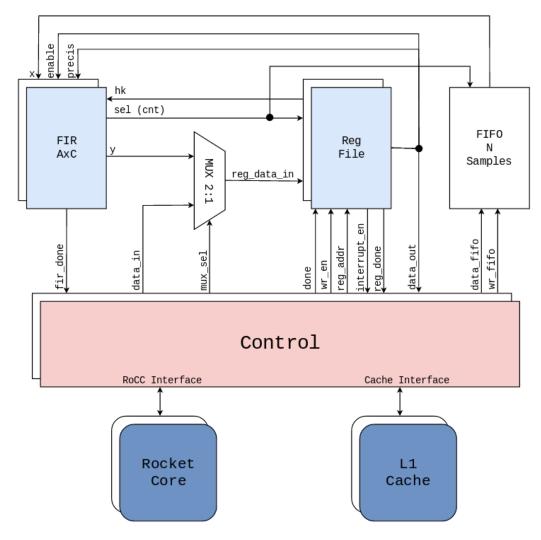

| 68 | Coprocessor FIR AxC Architecture                                  |

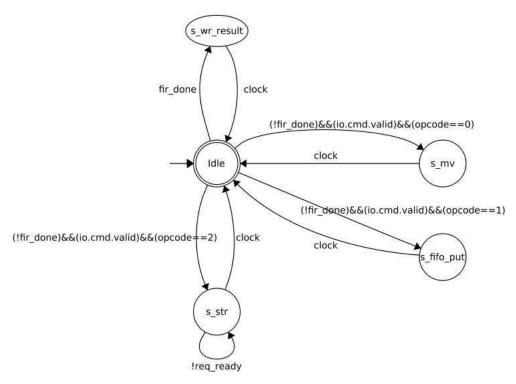

| 69 | Máquina de estado implemtando interface RoCC                      |

| 70 | Extensão de ISA RISC-V com Instruções do FIR AxC Desenvolvido 123 |

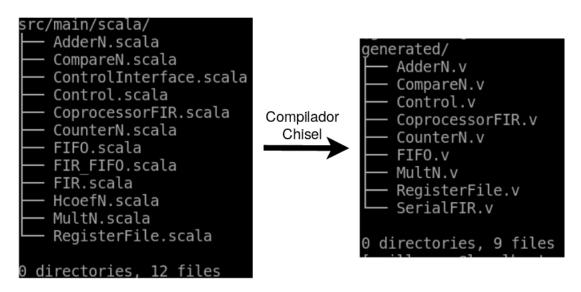

| 71 | Fontes Chisel e Verilog gerarados                                 |

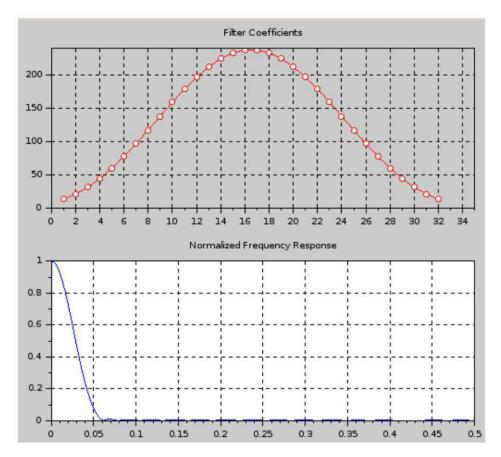

| 72 | Coeficientes e Responta ao Impulso de Filtro Passa Baixas         |

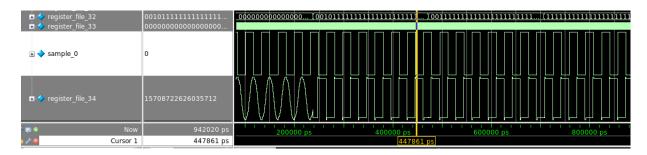

| 73 | RoCC FIR AxC executando filtragem de Onda Quadrada                |

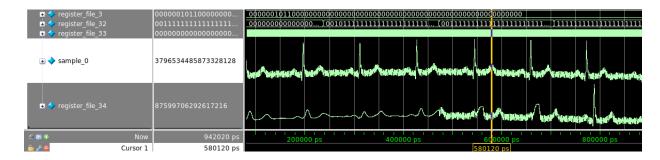

| 74 | RoCC FIR AvC executando filtragem de ECG 126                      |

### LISTA DE FIGURAS

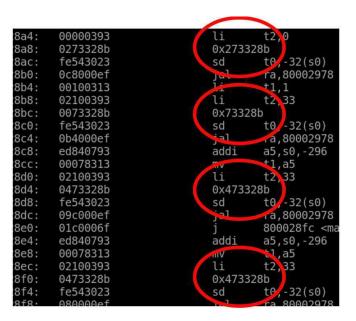

| 75 | Instruções RoCC adicionadas ao binário gerado  | 129 |

|----|------------------------------------------------|-----|

| 76 | RoCC FIR AxC embutido no Rocket Chip           | 130 |

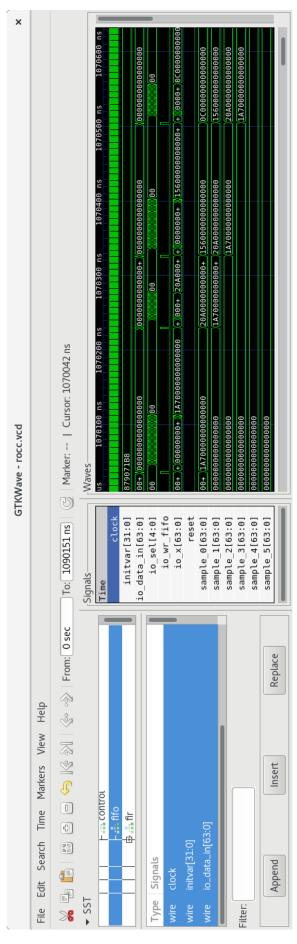

| 77 | FIFO recebendo as amostras                     | 131 |

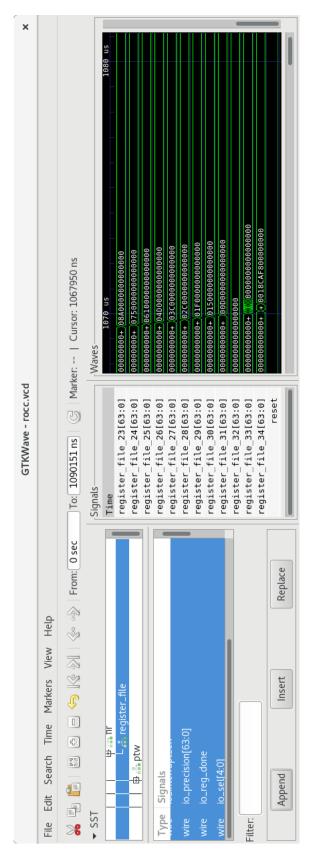

| 78 | Banco de Registradores recebendo valores do SW | 132 |

## Lista de Tabelas

| 1  | Tecnicas de Computação Aproximada em diferentes camadas [5] |

|----|-------------------------------------------------------------|

| 2  | Descrição de recursos OpTiMSoC                              |

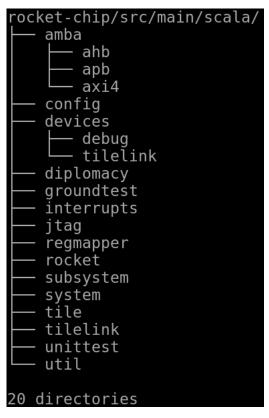

| 3  | Pacotes de Código do Rocket-Chip Generator [15]             |

| 4  | Parâmetros do processador Rocket Core                       |

| 5  | L1 Cache parameters and caractheristics                     |

| 6  | Sinais do Core Control                                      |

| 7  | Register Mode - Sinais de controle                          |

| 8  | Register Mode - Sinais de resposta                          |

| 9  | RoCC sinais de requisição de memória                        |

| 10 | RoCC sinais de resposta da memória                          |

| 11 | AUTL acquire signals                                        |

| 12 | AUTL grant signals                                          |

| 13 | RoCC FPU Request signals                                    |

| 14 | RoCC FPU Response signals                                   |

| 15 | RoCC CSR signals                                            |

| 16 | RoCC Opcodes                                                |

| 17 | Mapa de Memória Default do Rocket Chip                      |

| 18 | Construtores do tipo Bool                                   |

| 19 | Operadores que retornam tipo Bool                           |

| 20 | Construtores do tipo Bits                                   |

| 21 | Extensão de operadores lógico da Tabela 19                  |

| 22 | Construtores dos tipos UInt e SInt                          |

| 23 | Operadores aritméticos                                      |

| 24 | Conversão de tipos                                          |

| 25 | sintaxe tipo Vec                                            |

| 26 | Construtores de Registradores                               |

| 27 | Argumentos construção do Verilog                            |

| 28 | API Chisel Tester                                           |

| 29 | Argumentos construção do teste                              |

| 30 | Comandos SBT p/ compilação Chisel                           |

| 31 | Revisao dos diretórios do Rocket Chip                       |

| 32 | Revisao dos diretórios do Rocket Chip                       |

| 33 | Opções de comandos do C-Emulator                            |

| 34 | Extensão de ISA com instruções de Filtro FIR AxC            |

| 35 | Banco de Registrador do FIR AxC                             |

| 36 | Registrador de Status                                       |

| 37 | Coeficientes de 8 bits do Filtro Passa Baixas               |

## Lista de Códigos

| 1  | Downgrade in Rocket Chip git repository                                                 | 25 |

|----|-----------------------------------------------------------------------------------------|----|

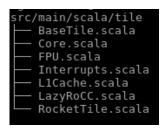

| 2  | Part of RocketTile.scala                                                                | 30 |

| 3  | $Implem.\ do\ processador\ With NB ig Cores\ no\ C\'odigo\ subsystem/Configs.scala.\ .$ | 33 |

| 4  | Implem. do processador WithNSmallCores no Código subsystem/Configs.scala.               | 33 |

| 5  | Parte do Código subsystem/Configs.scala p/ instanciar e config. RoCCs                   | 46 |

| 6  | Parte do Código subsystem/Configs.scala para remover mecanismo de coerên-               |    |

|    | cia de cache                                                                            | 49 |

| 7  | Parte do Código subsystem/Configs.scala para adic. binário do bootloader                | 55 |

| 8  | Parte do Código system/Configs.scala para modificar endereço da SRAM                    | 57 |

| 9  | Parte do Código system/Configs.scala para modificar endereço da DRAM                    | 57 |

| 10 | Mux 4:1 em Verilog                                                                      | 63 |

| 11 | Uma possível abstração para Mux                                                         | 63 |

| 12 | Uma possível abstração para Mux 4:1                                                     | 63 |

| 13 | Exemplo de uso para tipo Bool                                                           | 66 |

| 14 | Exemplo de operadores retornando Bool                                                   | 67 |

| 15 | Exemplo de uso para tipo Bits                                                           | 67 |

| 16 | Exemplo de operadores com tipo Bool                                                     | 68 |

| 17 | Exemplo de uso do tipo UInt e SInt                                                      | 69 |

| 18 | Exemplo de operadores aritméticos                                                       | 70 |

| 19 | Exemplo de criação de porta, fio e tipo inferido                                        | 70 |

| 20 | Exemplo de uso de constantes                                                            | 71 |

| 21 | sintaxe construção de Enum                                                              | 71 |

| 22 | Exemplo de conversão de tipo                                                            | 72 |

| 23 | Exemplo uso de Vec                                                                      | 72 |

| 24 | Exemplo uso de Bundles                                                                  | 73 |

| 25 | Exemplos de implementação de circuitos elementares                                      | 73 |

| 26 | Verilog gerado por Chisel ex. 1                                                         | 75 |

| 27 | Exemplo 1 de Reg. em Chisel                                                             | 75 |

| 28 | Exemplo 2 de Reg. em Chisel                                                             | 75 |

| 29 | Verilog gerado por Chisel ex. 2                                                         | 75 |

| 30 | Verilog gerado por Chisel ex. 3                                                         | 76 |

| 31 | Exemplo 3 de Reg. em Chisel                                                             | 76 |

| 32 | Outra forma de de escrever reg. do exemplo 3                                            | 76 |

| 33 | Tipos de atribuições                                                                    |    |

| 34 | Estrutura When [36]                                                                     |    |

| 35 | Estruturas Swithc [36]                                                                  |    |

| 36 | Evemplo de circuito usando condicional When                                             | 78 |

| 37 | Exemplo de circuito usando condicional Switch                                           |

|----|-----------------------------------------------------------------------------------------|

| 38 | Classe Module                                                                           |

| 39 | Instanciação de módulos e parametrização                                                |

| 40 | Implem. meio somador                                                                    |

| 41 | Implementação do somador completo com 2 meio somadores 82                               |

| 42 | Exemplo com classe BlackBox                                                             |

| 43 | Verilog gerado do Exemplo com classe BlackBox                                           |

| 44 | Função Main p/ geração de Verilog                                                       |

| 45 | Função Main p/ geração de Verilog                                                       |

| 46 | Função Main p/ geração de Simulador                                                     |

| 47 | Teste básico para circuito da ULA                                                       |

| 48 | Comandos para instalação do JDK no linux                                                |

| 49 | Comandos para instalação do SBT no linux                                                |

| 50 | Script build.sbt                                                                        |

| 51 | Implementação da FSM do circuito identificador de sequências 91                         |

| 52 | Comandos para compilação da FSM identificador de sequências                             |

| 53 | Implementação do teste do circuito identificador de sequências                          |

| 54 | Comandos para compilação do testbench do circuito identificador de sequências. 94       |

| 55 | Comandos para exemplo Spike                                                             |

| 56 | Exemplos de implementações do Rocket Chip                                               |

| 57 | Exemplos de implementações do Rocket Chip                                               |

| 58 | Construção de um emulador para configuração DefaultConfig                               |

| 59 | main.c para exemplo com Emulador                                                        |

| 60 | Emulando o sistema DefaultConfig                                                        |

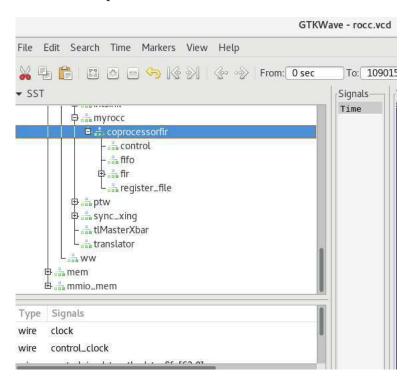

| 61 | Abrindo arquivo VCD gerado pelo emulador                                                |

| 62 | Parte do código tile/LazyRoCC.<br>scala para instanciar FIR RoCC AxC. $$ 127            |

| 63 | Parte do código subsystem/Configs.<br>scala para instanciar FIR RoCC AxC. $$ .<br>. 128 |

| 64 | Módulo topo instanciando RoCC FIR AxC no Rocket Chip                                    |

| 65 | Comando para gerar o emulador do SoC com RoCC implementado 129                          |

| 66 | entry.S                                                                                 |

| 67 | syscalls.c                                                                              |

| 68 | main.c                                                                                  |

| 69 | link.ld                                                                                 |

| 70 | util.h                                                                                  |

| 71 | enconding.h                                                                             |

| 72 | Variáveis de ambiente para configuração do Rocket Chip                                  |

| 73 | Makefile                                                                                |

| 74 | Testbench para RoCC FIR AxC em SystemVerilog                                            |

| 75 | main.c para testar RoCC FIR AxC                                                         |

#### Lista de Abreviações

RMS Recognition, Mining and Synthesis

AxC Approximate Computing

PNSR Peak Signal to noise ratio

BER Bit Error Rate

SoC System-On-a-Chip

HW HardwareSW Software

SDK Software Development Kit

**ASIC** Application Specific Integrated Circuits

HDL Hardware Description Language

CPU Central Processing Unit

ISA Instruction Set Architeture

BOOM Berkeley Out-of-Order

ISS Instruction Set Simulator

## Sumário

| Re            | esum                                   | 10                                                                                          | iv                               |

|---------------|----------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------|

| $\mathbf{A}$  | bstra                                  | act                                                                                         | $\mathbf{v}$                     |

| D             | edica                                  | tória                                                                                       | vi                               |

| Li            | sta d                                  | le Figuras                                                                                  | ix                               |

| $\mathbf{Li}$ | sta d                                  | le Tabelas                                                                                  | x                                |

| $\mathbf{Li}$ | sta d                                  | le Códigos                                                                                  | xii                              |

| Li            | sta d                                  | le Abreviações                                                                              | xiii                             |

| Ι             | Es                                     | trutura de Acolhimento e Projeto SysAx                                                      | 1                                |

| 1             | Est: 1.1 1.2                           | rutura de Acolhimento  Laboratório TIMA                                                     | 2<br>2<br>3                      |

| 2             | Pro<br>2.1<br>2.2<br>2.3               | jeto SysAx Contexto                                                                         | 5<br>5<br>6<br>7                 |

| II            | $\mathbf{E}$                           | studos Iniciais                                                                             | 8                                |

| 3             | Intr<br>3.1<br>3.2                     | rodução ao Approximate Computing  Técnicas HW/SW de Approximate Computing                   | 9<br>10<br>12                    |

| 4             | Ava                                    | liação de Plataformas de Prototipagem de SoCs                                               | 13                               |

|               | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | PULP-platfom .  Nios II .  MicroBlaze .  Rocket Chip SoC Generator .  LowRISC .  OpTiMSoC . | 13<br>17<br>18<br>19<br>21<br>22 |

|               | 4.7                                    | Critério de escolha de plataforma                                                           |                                  |

| II | $\mathbf{I}$ | A Pla                                   | taforma Rocket Chip Generator e suas Ferramentas                                 | 24         |  |  |

|----|--------------|-----------------------------------------|----------------------------------------------------------------------------------|------------|--|--|

| 5  | Roc          | cket Cl                                 | nip SoC Generator                                                                | <b>2</b> 5 |  |  |

| 6  | Vis          | Visão Geral dos Componentes de Hardware |                                                                                  |            |  |  |

|    | 6.1          | Rocke                                   | t Tile                                                                           | 30         |  |  |

|    |              | 6.1.1                                   | Processador - Rocket Core                                                        | 31         |  |  |

|    |              | 6.1.2                                   | FPU                                                                              | 36         |  |  |

|    |              | 6.1.3                                   | L1 Cache e MMU                                                                   | 36         |  |  |

|    | 6.2          | RoCC                                    | - Rocket Custom Coprocessor Interface [24]                                       | 39         |  |  |

|    |              | 6.2.1                                   | Visão Geral                                                                      | 39         |  |  |

|    |              | 6.2.2                                   | Interface Padrão                                                                 | 40         |  |  |

|    |              | 6.2.3                                   | Interface Estendida                                                              | 43         |  |  |

|    |              | 6.2.4                                   | Implementação do RoCC no Rocket Chip                                             | 46         |  |  |

|    | 6.3          | Barrai                                  | mentos                                                                           | 48         |  |  |

|    |              | 6.3.1                                   | TileLink Bus [25]                                                                | 48         |  |  |

|    |              | 6.3.2                                   | AMBA AXI4, AHB-Lite e APB Protocols                                              | 50         |  |  |

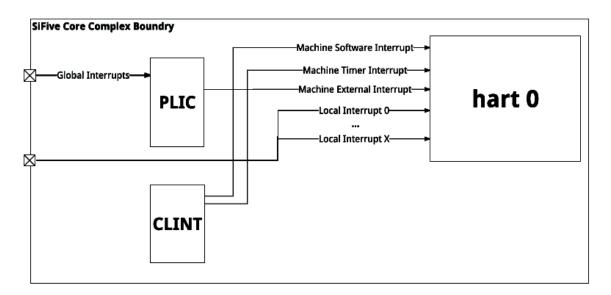

|    | 6.4          | Contro                                  | oladores de Interrupção                                                          | 51         |  |  |

|    |              | 6.4.1                                   | CLINT - Core Local Interrupt                                                     | 52         |  |  |

|    |              | 6.4.2                                   | PLIC - Platform-Level Interruptor Controller                                     | 54         |  |  |

|    | 6.5          | Memó                                    | rias                                                                             | 55         |  |  |

|    |              | 6.5.1                                   | ROM                                                                              | 55         |  |  |

|    |              | 6.5.2                                   | SRAM - Memória Principal                                                         | 56         |  |  |

|    |              | 6.5.3                                   | MMIO - Memory Mapped I/O                                                         | 57         |  |  |

|    | 6.6          |                                         | sitivos de $E/S$                                                                 |            |  |  |

|    | 6.7          | Debug                                   | g - DTM (Device Transport Module) e JTAG                                         | 59         |  |  |

|    | 6.8          |                                         | de Memória                                                                       |            |  |  |

| 7  | Chi          | sel - U                                 | ma nova Linguagem de Descrição de Hardware                                       | 62         |  |  |

|    | 7.1          | Introd                                  | lução (Overview)                                                                 | 62         |  |  |

|    | 7.2          | Tipos                                   | de Dados (Datatypes) e Operadores $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 66         |  |  |

|    |              | 7.2.1                                   | Bool                                                                             | 66         |  |  |

|    |              | 7.2.2                                   | Bits                                                                             | 67         |  |  |

|    |              | 7.2.3                                   | UInt e SInt                                                                      | 68         |  |  |

|    |              | 7.2.4                                   | Constantes                                                                       | 70         |  |  |

|    |              | 7.2.5                                   | Enum                                                                             | 71         |  |  |

|    |              | 7.2.6                                   | Conversão de Tipos                                                               | 72         |  |  |

|    |              | 7.2.7                                   | Tipos compostos: Vec e $Bundle \dots \dots \dots \dots \dots$                    | 72         |  |  |

|    |              | 7.2.8                                   | Conclusão: Lógica Combinacional e Fios (Wires)                                   | 73         |  |  |

|    | 7.3          | Lógica                                  | Sequencial: Registradores, Clock e Reset                                         | 74         |  |  |

|    | 7.4  | Semâr   | ntica                                               | 77  |

|----|------|---------|-----------------------------------------------------|-----|

|    |      | 7.4.1   | Atribuições                                         | 77  |

|    |      | 7.4.2   | When e Switch                                       | 77  |

|    | 7.5  | Const   | ruindo Módulos                                      | 80  |

|    |      | 7.5.1   | Hierarquia de Módulos e Parametrização              | 80  |

|    |      | 7.5.2   | Classe BlackBox, conectando IPs Verilog             | 82  |

|    |      | 7.5.3   | Classe geradora de Verilog                          | 84  |

|    | 7.6  | Chisel  | Testbenches                                         | 86  |

|    | 7.7  | Prepa   | rando o ambiente de programação Chisel              | 88  |

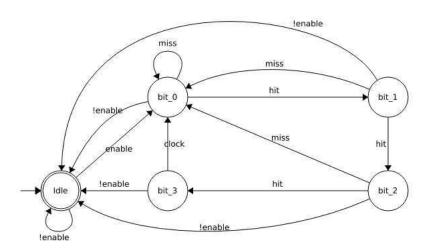

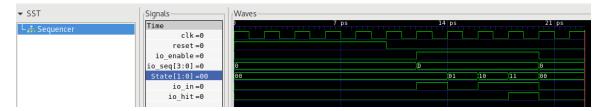

|    | 7.8  | FSM,    | um identificador de sequência binária               | 90  |

| 8  | Den  | nais Fe | erramentas do Rocket Chip                           | 95  |

|    | 8.1  | Ferrar  | nentas de Desenvolvimento de SW - riscv-tools/      | 96  |

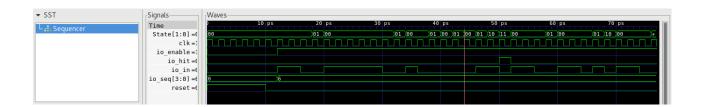

|    |      | 8.1.1   | RISC-V GNU Compiler Toolchain                       | 97  |

|    |      | 8.1.2   | Simulador de ISA RISC-V Spike                       | 98  |

|    |      | 8.1.3   | Construindo um "Hello World!" e executando no Spike | 100 |

|    | 8.2  | Geran   | do Verilog de SoC Rocket Chip - vsim/ $\dots \dots$ | 102 |

|    | 8.3  | Emula   | ador - emulator/                                    | 106 |

|    |      | 8.3.1   | Bootloader e Rocket Chip Tethered                   | 108 |

|    |      | 8.3.2   | Exemplo de uso do Emulador                          | 110 |

| 9  | Con  | clusão  |                                                     | 113 |

| I  | / I  | Desen   | volvimento de Hardware AxC no Rocket Chip           | 114 |

| 10 | Filt | ro FIF  | R AxC                                               | 115 |

|    | 10.1 | Filtro  | FIR Serial                                          | 115 |

|    | 10.2 | Filtro  | FIR em paradigma AxC                                | 116 |

| 11 | Cop  | rocess  | sador FIR AxC                                       | 118 |

|    | 11.1 | Interfa | ace de Filtro Serial FIR AxC                        | 118 |

|    | 11.2 | ISA p   | ara Coprocessador FIR AxC                           | 119 |

|    | 11.3 | Banco   | de Registradores                                    | 119 |

|    |      | 11.3.1  | Registrador de <i>Status</i>                        | 120 |

|    | 11.4 | Arquit  | tetura                                              | 122 |

|    |      | 11.4.1  | Módulo de Controle                                  | 123 |

|    |      | 11.4.2  | Testbench em SystemVerilog e Resultados             | 124 |

|    | 11.5 | Integr  | ação do RoCC no Rocket Chip                         | 127 |

|    |      | 11.5.1  | Construção de SW e Emulação do Sistema              | 129 |

|    |      | 11.5.2  | Problemas Enfrentados e Conclusão                   | 130 |

|     |        | _   |   |                                         |

|-----|--------|-----|---|-----------------------------------------|

| C   | TTA    | TA  | D | $T \cap$                                |

| . 7 | 1 / /\ | /IA | ĸ | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

|     |        |     |   |                                         |

| 12 Conclusão                                                    | 133 |

|-----------------------------------------------------------------|-----|

| Referências                                                     | 134 |

| Anexo A: Códigos p/ compilação cruzada com RISC-V GNU Toolchain | 137 |

| Anexo B: Testbench RoCC FIR AxC                                 | 166 |

| Anexo C: main.c para teste de RoCC FIR AxC                      | 170 |

# Parte I

# Estrutura de Acolhimento e Projeto SysAx

#### 1 Estrutura de Acolhimento

#### 1.1 Laboratório TIMA

Figura 1: Logo TIMA.

TIMA - Techniques of Informatics and Microelectronics for integrated systems Architecture, é um laboratório de pesquisa pública do CNRS (*Centre National de la Recherche Scientifique*), Instituto Grenoble-INP e UGA (*Université Grenoble Alpes*).

Os tópicos de pesquisa do TIMA abrangem a especificação, projeto, verificação, testes, ferramentas CAD e métodos de *design* para sistemas integrados, desde componentes analógicos a digitais, em uma extremidade do espectro, até SoCs multiprocessados junto a sistemas operacionais básicos.

O TIMA está na origem de oito empresas *spin-off*. Entre os mais recentes, o TIEMPO, criada em 2007 para industrializar a tecnologia de *design* de circuitos assíncronos inventada pelo grupo CIS; UROMEMS financiado por Hamid Lamraoui (grupo MNS) para desenvolver seus resultados de PhD em sensores de pressão MEMS, em cooperação com o TIMC e o hospital Parisiense Pitié Salpétrière: a empresa visa resolver problemas de incontinência urinária com um esfíncter artifical mais sofisticado e melhor tolerado.

O TIMA é uma equipe multinacional, com membros e estagiários de todo o mundo. O Laboratório está estruturado em cinco equipes de pesquisa:

- AMfoRS: Architectures and Methods for Resilient Systems.

- CDSI: Circuits, Devices and System Integration.

- **RIS**: Robust Integrated Systems.

- RMS: Reliable Mixed-signal Circuits and Systems.

- SLS: System Level Synthesis.

Site oficial http://tima.univ-grenoble-alpes.fr.

#### 1.2 Equipe AMfoRS

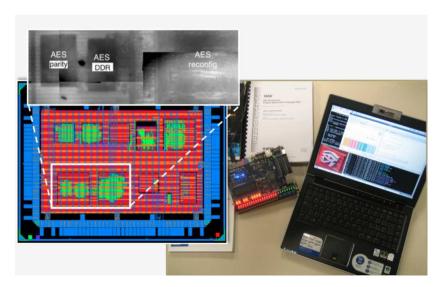

Figura 2: AMfoRS.

A equipe da AMfoRS foi criada em janeiro de 2015. Sua principal experiência é em verificação e resiliência de sistemas. Esta perícia vem das habilidades conjuntas de parte dos membros dos grupos ARIS e VDS anteriores. O AMfoRS visa aumentar a sinergia entre atividades de projeto, verificação e validação de sistemas integrados confiáveis e seguros, com foco em componentes digitais.

A equipe aborda os desafios cruciais relacionados ao que é resumido como "sistemas resilientes", ou seja, a garantia de que os sistemas não se comportarão de maneira inesperada e que proporcionarão um nível substancial de robustez e segurança.

Atingir um nível significativo de segurança requer o design de componentes criptográficos otimizados e robustos que fornecem proteção contra ataques de hardware. Além do desenvolvimento de tais blocos, vários métodos e ferramentas para resiliência são necessário, para garantir melhor confiabilidade e segurança.

As soluções "alvo" visam realizar previsão de envelhecimento, protegendo circuitos digitais contra falhas e dando-lhes a possibilidade de adaptar dinamicamente seu comportamento em caso de erros. Soluções analíticas também são tratadas para análise de confiabilidade, ferramentas para a instrumentação automática de sistemas de hardware com monitores e para testar esses sistemas instrumentados, além de ferramentas especializadas para melhorar o projeto de circuitos 3D.

Como os sistemas estão se tornando cada vez mais complexos, há também uma necessidade crucial de métodos eficientes para a análise em nível de sistema. O trabalho em andamento e futuro da equipe inclui debug e testes online para System-On-Chips embutidos em seu ambiente funcional.

#### Principais temas de pesquisa da equipe:

- Multi-level specification and verification of hardware/software on-chip architectures: formal and semi-formal approaches

- System-level modeling, analysis and testing.

- Dependability of integrated systems: fault detection/tolerance, on-line monitoring, self-adapting and self-healing circuits.

- Dependability evaluations: fault injections and alternatives (analytical or formal approaches), prediction of ageing effects on lifetime.

- Security of integrated systems: cryptographic accelerators, counter-measures against hardware attacks.

O estágio em questão foi desenvolvido junto a essa equipe. Mais informações sobre ela pode ser encontrada no site http://tima.imag.fr/amfors/. Informações sobre as demais equipes estão disponíveis em http://tima.imag.fr/.

#### 2 Projeto SysAx

#### 2.1 Contexto

Durante as últimas décadas, a indústria de semicondutores mostrou muitas melhorias em termos de eficiência energética dos dispositivos produzidos: projetos multiprocessadores, componentes de baixa potência (ultra-low power), entre outros. No entanto, como descrito em [2], o consumo de energia de sistemas de computacionais ainda está crescendo rapidamente e em um ritmo alarmante. Além disso, um grande número de aplicativos, geralmente chamados de RMS (do inglês, Recognition, Mining and Synthesis), surgiram e estão ganhando cada vez mais popularidade. Dos sistemas portáteis e Internet of Things (IoT) aos grandes centros de dados, eles representam agora uma parcela significativa e crescente dos recursos computacionais globais e do consumo de energia [3]. Indicando que é preciso melhorar a eficiência energética dos futuros dispositivos de silício. Isso é realmente crítico, já que a tecnologia de semicondutores continua diminuindo para transistores nanométricos: melhores desempenhos, mas ao preço de uma crescente ineficiência energética [9]–[10].

Felizmente, aplicativos como o RMS geralmente apresentam propriedades de resiliência de erro intrínsecas [11]. De fato, esses aplicativos não precisam fornecer um resultado único ou exato. Por exemplo, em aplicativos de vídeo, alguns tipos de erros, como a quantização adaptativa local, podem ser facilmente tolerados, contanto que o erro permaneça abaixo do limiar visual da percepção visual humana. Com base nessas observações, nos últimos anos, uma solução muito promissora conhecida como "Computação Aproximada" (ou AxC - Approximate Computing) [2], [12], está ganhando cada vez mais interesse na comunidade científica, tanto na indústria quanto na academia. O AxC baseiase na observação intuitiva de que, ao executar a computação exata, é necessária uma quantidade elevada de recursos, permitindo a aproximação seletiva ou a violação ocasional da especificação, o que proporciona ganhos de consumo de energia superiores a uma ordem de magnitude. Ou, para a mesma quantidade de consumo, os desempenhos podem ser melhorados. Várias aplicações de AxC foram pesquisadas, tais como análise de dados, computação científica, multimídia, processamento de sinais, aprendizado de máquina e assim por diante.

Olhando para o estado da arte, as técnicas de AxC propostas podem ser classificadas como: software AxC (por exemplo, iterações de algoritmos reduzidas, gerenciamento de tarefas do SO, entre outros), arquitetura AxC (por exemplo, processadores com blocos aritméticos aproximados, entre outros) ou circuitos AxC (por exemplo, tensão de alimentação reduzida, lógica imprecisa, entre outros).

Muitas técnicas são propostas, mas para serem mais amplamente aceitas, a AxC precisa de mais pesquisas sobre gerenciamento de qualidade. Na verdade, a maioria das abordagens é orientada por componente ou camada para cada uma das métricas dedicadas: PNSR (Peak Signal to noise ratio) para aplicações de processamento de imagem e vídeo, BER (Bit Error Rate) para componentes de hardware aproximados, etc. No entanto, um sistema aproximado requer uma avaliação do impacto de cada componente de cada camada (local) na precisão global da aplicação. É preciso, portanto, definir quais são os Metadados adequados (atributos de qualidade/precisão) e quão coerentes, correlacionados e simplificados são as métricas associadas a serem aplicadas em todas as camadas significativas do sistema.

#### 2.2 Objetivos

O projeto SysAx proposto aqui tem como objetivo final o desenvolvimento de um SoC auto-adaptativo composto por técnicas de hardware e software de Computação Aproximada. A ideia é construir um sistema que modifique seu contexto de um modo preciso para um modo impreciso e vice-versa, executando diferentes aplicativos RMS, tais como reconhecimento de imagens e/ou algoritmos de aprendizado de máquina.

Grosso modo, pretende-se avaliar a relação entre computação com aproximações, qualidade do resultado e desempenho do sistema. Por exemplo, em processamento de imagem, o quanto de erro pode ser aceito sem que aja degradação da imagem em relação ao que o olho humano percebe. Aproximar cálculos desse grupo de aplicações implica na alteração de alguns parâmetros computacionais, como velocidade de processamento, diminuição de *overhead* de software e hardware, menor consumo de energia, entre outros. É esse tipo de avaliação e conclusão que a pesquisa pretende formalizar.

Exakt PSNR = 31.16

Approximiert PSNR = 28.9

Bitreduziert PSNR = 19.04

Figura 3: Qualidade de imagem com aritmética exata, aproximação dos 8 bits LSB e implementação de largura de bit reduzida (fonte: [1]).

Um outro objetivo do estágio é educacional. Isto é, pretende-se usar a plataforma de pesquisa também como uma plataforma de ensino, com intuito de auxiliar a compreensão dos estudantes a relação entre hardware e software no desenvolvimento de sistemas integrados.

Portanto, esse projeto de longo prazo possuí dois aspectos principais:

- **Pesquisa**: Desenvolver um SoC para ser usada na exploração de novas ideias de Computação Aproximada, bem como outros campos de pesquisa das equipes do laboratório TIMA, por exemplo para avaliar técnicas de tolerância a falhas (equipe RIS) ou SoCs multiprocessados de sistemas embarcados e prototipagem (equipe SLS).

- Educação: Desenvolver um SoC para ser usada como uma ferramenta de prototipagem para criar SoCs personalizados destinados como suporte de educação para o departamento SEI (Systèmes Electroniques Integrés) na escola de engenheria PHELMA.

Devido a existencia de duas linhas de pesquisa (hardware AxC e software AxC) o laboratório contou com dois estágiarios para iniciar a pesquisa, sendo o presente relatório relacionado ao estágio de desenvolvimento de hardware.

#### 2.3 Trabalhos propostos

Motivado por esses desafios, este trabalho surge como uma fase preliminar, para estabelecer, documentar e demonstrar o uso de uma plataforma de prototipação de SoC para dar base a pesquisa e ser usada como ferramenta educacional. Sendo os macro objetivos os seguintes items:

- 1. Ler e entender o estado-da-arte de técnicas de hardware para projetar circuitos integrados (CI) de Computação Aproximada.

- 2. Explorar projetos de SoCs de código aberto e escolher o que melhor se adeque aos objetivos do projeto.

- 3. Documentar a plataforma selecionada explanando: arquitetura, componentes de hardware e ferramentas de desenvolvimento.

- 4. Experimentar o fluxo de co-projeto de software e hardware usando na plataforma selecionada.

- 5. Sugerir e desenvolver uma demonstração de uma técnica de Computação Aproximada usando a plataforma.

- 6. Sintetizar demonstração em FPGA.

- 7. Estimar consumo de potência para diferentes cenários de aproximação.

# Parte II

# Estudos Iniciais

#### 3 Introdução ao Approximate Computing

Os computadores continuam se tornando cada vez mais rápidos e poderosos, abrindo as portas para processamento de algoritmos e aplicações como aprendizado de máquina (Machine Learning), Deep Learning, visão computacional, processamento de linguagem natural e outros. Todos esses aplicativos são chamados de aplicativos de reconhecimento, mineração e síntese (RMS). Hoje, essas aplicações são responsáveis por uma parcela significativa de recursos computacionais em todo o espectro da computação, de dispositivos móveis e Internet das Coisas (IoT) até Data Centers de grande escala [2].

As aplicações de RMS geralmente apresentam as seguintes características:

- Resiliência ao erro: processam enormes quantidades de dados ruidosos, por exemplo, provenientes de vários sensores que apresentam variações aleatórias.

- Saídas não precisas podem ser aceitáveis: significa que a saída ou alguns dos cálculos intermediários não são necessários para alcançar valores aceitáveis

- Alto consumo de energia devido a cálculos intensos.

À partir da observação dessas características, os pesquisadores e projetistas de sistemas começaram a investigar que ao reduzir a precisão do processamento, pode-se ter ganhos significativos na eficiência energética dos sistemas, dado que essas aplicações toleram erro. Técnicas que visão provar esse conceito são chamadas de *Approximate Computing* ou Computação Aproximada.

O Approximate Computing pode ser definida como: "Uma técnica de computação (de forma geral um paradigma) que um resultado possivelmente impreciso em vez de um resultado preciso e pode ser usado para aplicações em que um resultado aproximado é suficiente para o propósito" [3].

Figura 4: AxC.

A computação aproximada é introduzida apenas em dados não críticos, uma vez que a aproximação de dados críticos (por exemplo, operações de controle) pode levar a conseqüências desastrosas. Exemplos de aplicações são: processamento de vídeo devido às limitações perceptuais dos seres humanos, mecanismos de buscas (Google), entre outros.

Será apresentado, de forma superficial, algumas ideias de software e hardware para computação em paradigma AxC, como uma forma de apresentar o estado-da-arte desse domínio de estudo.

#### 3.1 Técnicas HW/SW de Approximate Computing

Na Tabela 1 são apresentadas técnicas de Computação Aproximada nas diferentes camadas dos sistemas, software, arquitetura e circuitos.

| Camadas     | Técnicas de Computação Aproximada                         |

|-------------|-----------------------------------------------------------|

| Software    | Loop perforation, Code perforation, Theread fusion, Tun-  |

|             | able kernels, Patter reduction.                           |

| Arquitetura | Approximate storage, ISA extensions, Approximate acceler- |

|             | ators.                                                    |

| Circuito    | Imprecise logic, Voltage overscaling, Analog computation, |

|             | Precision scaling.                                        |

Tabela 1: Técnicas de Computação Aproximada em diferentes camadas [3].

No que diz respeito a camada de software, a pesquisa atual busca desenvolver ferramentas de software que possam expressar idéias relacionadas ao AxC. O objetivo dessas ferramentas é estimar como os erros se propagam e quão confiável um sistema pode ser, nas diferentes partes que compõe o desenvolvimento de software: código, compiladores, mecanismos de análise, entre outros.

Algumas linguagens de programação já foram desenvolvidas em pesquisas, como EnerJ [4] e Rely [5], elas fornecem uma abstração para cálculos aproximados, como tipos de dados especiais relacionados a Computação Aproximada, permitindo avaliar diferentes algoritmos que permitam inexatidão em seus resultados. Nos compiladores, os pesquisadores buscam modificar os compiladores adicionando técnicas como *Loop Perforation*, que pode gerar menos iterações de loop em tempo de compilação e, assim, gerar um programa binário que seja executado mais rapidamente. Esses compiladores também podem produzir código de máquina que tenha como alvo hardware específico aproximado, de forma autônoma ou ajudado pelas diretivas do programador. Com a existencia de compiladores abertos, a exemplo do GCC (GNU C Compiler), torna-se viável a pesquisa.

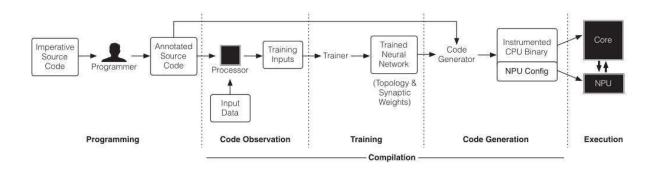

Figura 5: Compilador gerando códigos para executar parte em Processador parte em Unidade de Processamento Neural (Fonte: [3]).

Na camada seguinte, das arquiteturas de processadores, a AxC é investigada em dois grupos distintos. O primeiro grupo tem como objetivo dar suporte à Computação Aproximada executando código tradicional em processadores de uso geral com recurso para executar algumas instruções escolhidas ou segmentos de código no modo aproximado, implicando em uma eficiência de energia (veja Figura 6). O segundo grupo transforma segmentos aproximados do código tradicional em um algoritmo neuralmente inspirado em aceleradores, veja Figura 5. Ambos os grupos deve-se ter um compilador ou programador para identificar ou anotar segmentos de códigos que possam ser cálculados de forma aproximada [3].

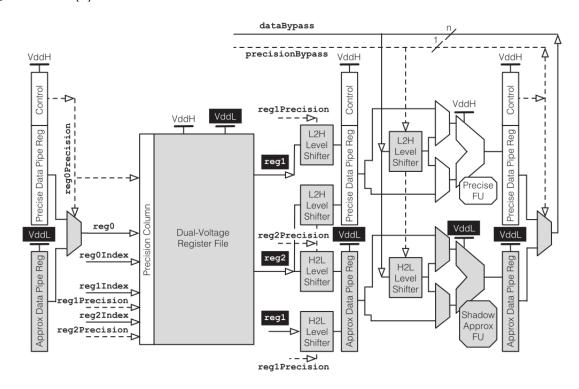

Figura 6: Exemplo de processador com circuitos precisos e não precisos (Fonte: [3]).

Na camada de mais baixo nível, existem várias linhas de pesquisa que estudam arquiteturas de armazenamento e memória aproximadas, assim como circuitos aritméticos aproximados, como: somadores, multiplicadores, divisores, ponto flutuante, etc. O objetivo principal é reduzir a sobrecarga de hardware, e consequentemente acelerar processamento e diminuir consumo de energia elétrica.

Em armazenamento e memória aproximados, em vez de armazenar valores de dados exatos, eles podem ser armazenados de forma aproximada, por exemplo, truncando os bits inferiores em dados de ponto flutuante. Outro método é aceitar uma memória menos confiável. Para isso, DRAMs e eDRAMs, a taxa de atualização pode ser reduzida e, em SRAMs, a tensão de alimentação pode ser também reduzida [6], [7]. Maior largura de banda do canal de memória [8]. Em geral, qualquer mecanismo de detecção e correção de erros deve ser desativado, diminuindo o overhead de hardware.

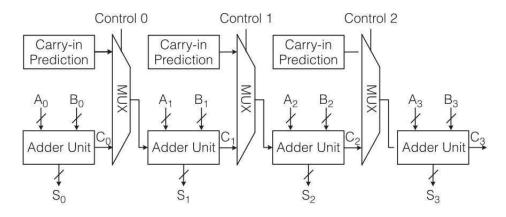

Em circuitos aritméticos as técnicas variam de redução de tensão (o que parece não dar ganhos significativos de consumo de energia [3]) e especulação de valores. Um exemplo é apresentado na Figura 7 em que a precisão do circuito somador é configurável, isto é, vários sub-somadores podem aceitar o transporte previsto ou a propagadação normal do carry sendo os resultados parciais são combinados para formar a saída final aproximada [3]. Dado que muitas aplicações do tipo RMS usam operações aritméticas, essa abordagem para promissora.

Figura 7: Somador de precisão configurável (Fonte: [3]).

#### 3.2 Conclusão

A pesquisa em Computação Aproximada ainda precisa ser bastante aprofundada. Tendo em vista que as abordagens estão presentes em todo espectro da criação de Sistemas Computacionais (de circuitos aritméticos ao software), é preciso estabelecer uma ferramenta que permita avaliar e desenvolvar novas técnicas de AxC em todas as direções. É nesse ponto que esse trabalho tem seu objetivo principal, preparar uma plataforma computacional que permita explorar e desenvolver ideias AxC.

Na próxima seção, é apresentado alguns dos sistemas avaliados durante o estágio e qual plataforma se mostrou mais promissora para os objetivos futuros de pesquisa no Laboratório TIMA.

#### 4 Avaliação de Plataformas de Prototipagem de SoCs

Nessão seção, serão apresentadas as plataformas de prototipagem de *System-On-Chip* que foram avaliadas no estágio. O objetivo dessa atividade foi escolher a plataforma computacional mais adequeada para torna-se instrumento de base na pesquisa, ou seja, que ofereça maiores vantagens para os objetivos que a pesquisa apresenta: desenvolvimento de ideias de Computação Aproximada e plataforma de ensino de Sistemas Embarcados.

#### 4.1 PULP-platfom

Figura 8: Logo PULP-platform.

O PULP-platform é um projeto que iniciou-se nos grupos: Integrated Systems Laboratory (IIS) da ETH Zürich e Energy-efficient Embedded Systems (EEES) da University of Bologna, com intuito de explorar novas ideias de arquiteturas de computadores para processamento com Ultra-Baixa Potência, termo mais comumente referenciado no mundo acadêmico por *Ultra Low-Power Processing*. O projeto busca desenvolver plataformas computacionais para desenvolvimento escalável <sup>1</sup> de hardware e software visando sempre a eficiência energética.

O framework desenvolvido do projeto encontra-se disponível em https://github.com/pulp-platform e já conta com algumas plataformas, destacando-se:

- PULP Parallel Ultra-Low-Power

- PULPino

- PULPissimo

- bigPULP

- ARIANE

<sup>&</sup>lt;sup>1</sup>Um Sistema Escalável é um sistema que ao ser acrescido de novos compomentes aumenta seu desempenho. Sistema escalável implica desempenho.

As unidades de processamento do projeto, desenvolvidas pelo grupo, são implementações de algumas variações da ISA aberta RISC-V, sendo elas: o processador RI5CY (32 bits) com 4 níveis de *pipeline* e implementação de ISA RV32IMFC, o zero-riscy, um processador com 2 níveis de *pipeline* de 32 bits e ISA RV32IMC e o processador ARIANE com 6 níveis de pipeline e implementação de ISA RV64G (G referindo ao conjunto completo da ISA), capaz de executar sistemas Linux. Cada uma dessas implementações são usadas como unidades de processamentos nos SoCs, isto é, o PULP, PULPino, etc.

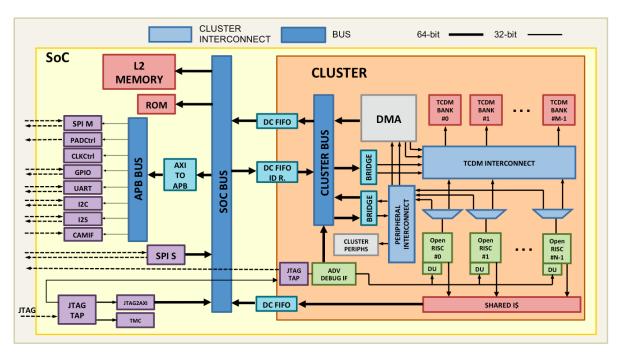

O PULP <sup>2</sup> é um cluster <sup>3</sup> que pode ser síntetizado com os processadores zero-riscy e RI5CY. É uma arquitetura avançada de Microcontroladores, com suporte a multiprocessamento e periféricos como I2S, I2C, SPI e UART, veja Figura abaixo.

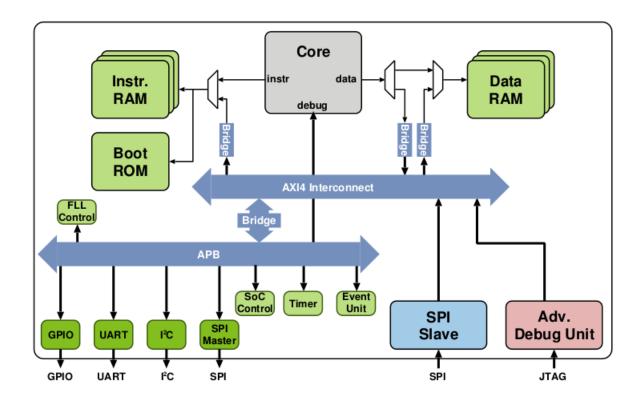

Figura 9: Arquitetura do PULP.

Em resumo o PULP tem as seguintes caraterísticas:

- RI5CY ou zero-riscy como processador principal

- micro-DMA

- Hardware Processing Engines, ou máquina de processamento em HW, em tradução livre

- Computação paralela por cluster

- Periféricos

- Unidade de detectação de evento (Event Unit)

- SDK (Software Development Kit)

<sup>&</sup>lt;sup>2</sup>Repositório oficial: https://github.com/pulp-platform/pulp

<sup>&</sup>lt;sup>3</sup>Um cluster consiste em computadores fracamente ou fortemente ligados que trabalham em conjunto, de modo que, em muitos aspectos, podem ser considerados como um único sistema (Fonte: Wikipédia https://pt.wikipedia.org/wiki/Cluster).

Já o PULPino <sup>4</sup> é um Microcontrolador de baixo consumo de energia com apenas uma unidade de processamento. Quando seu processador está inativo, ele pode ser colocado em um modo de baixa energia, onde apenas uma unidade de evento simples está ativa, fazendo com que o sistema consuma o mínimo de energia. Uma unidade de evento especializada ativa o processador no caso de um evento/interrupção de forma configurável. O PULPino foi sintetizado como ASIC (Application Specific Integrated Circuits) em tecnologia UMC 65nm em janeiro de 2016 e ele possui suporte completo a debug. A arquitetura é apresentada na Figura 10.

Figura 10: Arquitetura simplificada do PULPino.

Como características principais, destacam-se:

- RI5CY ou zero-riscy como processador principal (único processador)

- Sistema de baixo consumo de energia (Low-Power)

- Unidade de detectação de evento (Event Unit) em modo low-power

- Periféricos (inclusive JTAG para depuração)

- Suporte a interrupções

- SDK

<sup>&</sup>lt;sup>4</sup>Repositório oficial: https://github.com/pulp-platform/pulpino

O PULPino e PULPissimo <sup>5</sup> são bastantes similares, ambos são projetos de Microcontroladores e possuem um único processador, que pode ser o RI5CY ou zero-riscy. A principal diferença é que o PULPissimo incrementa ao SoC: micro-DMA, HWPE (*Hardware Processing Engines*, ou máquina de processamento, em hardware em tradução livre) e um novo subsistema de memória. Sua arquitetura é apresentada na Figura 11.

Figura 11: Arquitetura simplificada do PULPissimo.

O SoC com processador ARIANE não fora avaliado, porém pode ser facilmente explorado em seu repositório oficial https://github.com/pulp-platform/ariane. Todos esses projetos foram escritos com HDL (Hardware Description Language) SystemVerilog e usufrui de algumas ferramentas para geração de código de máquina, permitindo: desenvolvimento, simulação, síntese e avaliação das plataformas.

Interfaces de Entrada e Saída (E/S), permitem adicionar periféricos próprios sem muito esforço (sem alterar drasticamente a plataforma), porém, componentes internos como unidade de ponto flutuante, multiplicadores, micro-DMA, cache, etc, não foram projetados para serem modificados facilmente, tornando a tarefa de adicionar implementações próprias para teste e avaliação (no caso em questão, de Computação Aproximada) de ideias um trabalho não trivial.

$<sup>^5\</sup>mathrm{Reposit\'{o}rio}$  oficial: https://github.com/pulp-platform/pulpissimo

#### 4.2 Nios II

Figura 12: Logo Nios II.

Plataformas computacionais para desenvolvimento paralelo de HW e SW podem ser desenvolvidas com framework oferecido pelas ferramentas FPGAs, tendo em vista que elas possuem IPs como: processadores modificáveis, periféricos, interfaces, etc. Isso permite prototipação rápida de SoCs, possibilitando testes e avaliação de novas ideias de HW e SW (para a pesquisa em questão, permite avaliar ideias de AxC). Portanto, foi avaliado o Nios II da empresa Intel FPGAs.

O Nios II <sup>6</sup> é uma arquitetura de processador RISC de 32 bits projetada especificamente para a família de FPGAs Intel/Altera. Ele incorpora muitos recursos, tornando-o adequado para uma ampla gama de aplicações de computação. O Nios II permite:

- Definição de instruções personalizadas: como forma de atingir metas de desempenho

- Periféricos padrões (disponibilizados como IPs)

- Periféricos personalizados (definidos pelo usuário)

- Unidade de Gerenciamento de Memória (MMU)

- Execução de Sistemas Operacionais (SO), como o kernel Linux

- SDK

Existem várias versões do Nios II, sendo destacando-se:

- Nios II/e: baixo custo para FPGAs pequeno porte, sem necessidade de licença

- Nios II/s: manter um equilíbrio entre desempenho e custo, necessita de licença

- Nios II/f: projetado para desempenho máximo às custas do aumento de área do processador, necessita de licença

As grandes desvantagens de escolher essa plataforma é a incapacidade de alterar componentes internos ao processador, como, unidades aritméticas (ponto flutuante, multiplicadores, somadores), cache, DMAs, etc, que podem ser alvo de interesse para pesquisa. Além disso, algumas versões que possuem maior desempenho são pagas.

<sup>&</sup>lt;sup>6</sup>Site oficial: https://www.intel.com/content/www/us/en/products/programmable/processor/nios-ii.html

#### 4.3 MicroBlaze

Figura 13: IP MicroBlaze.

A CPU MicroBlaze é uma família de configurações de processador RISC de 32 bits, predefinidas e modificáveis, disponível para se usar na maioria das FPGAs Xilinx. O projetista do sistema pode aproveitar o Xilinx SDK sem custo, baseado no Eclipse, e sem experiência prévia em FPGA, para desenvolver diferentes soluções com MicroBlaze, que é capaz de fornecer CPUs para projetos de Microcontroladores, para processamento em tempo real ou capaz de executar sistemas Linux.

Partindo de uma configuração, é possível uma personalização adicional de uma variedade de opções do processador, além disso um catálogo de periféricos são disponível, como PWMs, UARTs, DMAs, controladores de interrupção, interfaces seriais, entre outros, que podem ser adicionados na construção de SoCs. Também é possível adicionar periféricos próprios para construção do sistema, com intuito de satisfazer as necessidades específicas do projeto.

Em resumo, o MicroBlaze possui:

- Tamanho de cache configurável

- Opção de pipeline de 3, 5 ou 8 estágios

- Periféricos (IPs Xilinx ou IP próprio)

- Unidade de gerenciamento de memória configurável

- Interfaces de barramento configurável

- Instruções para operações de multiplicação, divisão e ponto flutuante podem ser adicionadas/removidas

- Suporta SOs que requerem paginação e proteção com base, como o kernel do Linux

- Suporta SOs com uma proteção simplificada e modelo de memória virtual, por exemplo, FreeRTOS ou Linux sem suporte a MMU

Várias personalizações permitem que um desenvolvedor faça as trocas de design apropriadas para um conjunto específico de hardware host e requisitos de software de aplicativos, mas, de forma semelhante ao Nios II, componentes internos não podem ser modificados.

# 4.4 Rocket Chip SoC Generator

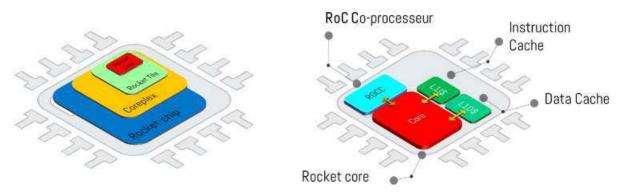

Figura 14: Visão geral dos componentes do Rocket Chip.

O Rocket Chip é um gerador de SoC de código aberto que emite RTL sintetizável. Ele aproveita a Linguagem de Descrição de Hardware Chisel para compor uma biblioteca de geradores sofisticados para processadores, caches e interconexões em um SoC integrado. O Rocket Chip tem as seguintes características:

- Possui implementações de processadores de uso geral: o Rocket Core com 5 estágios de pipeline e Z-Scale com 3 estágios, ambos configuráveis

- Processador Fora de Ordem (BOOM Berkeley Out-Of-Order) também configurável

- Implementa variações de ISA aberta RISC-V permitindo adicionar/remover extensões de ISA RISC-V no sistema

- Possui interface de depuração JTAG (pode ser facilamente removida)

- Permite configurar tamanho de barramento: 32, 64 ou 128 bits

- Permite adicionar, remover ou configurar memória cache

- Permite integrar arquiteturas com multi-processadores heterogêneas para ganhos adicionais de eficiência

- Suporta a integração de aceleradores personalizados na forma de extensões de conjunto de instruções: coprocessadores (RoCC Rocket Custom Coprocessor) ou novos processadores totalmente independentes

- Controladores de Interrupção locais e globais

- Temporizadores e interrupção de software para cada processador

- Pode construir pequenos SoCs (como Microcontroladores) até sistemas computacionais complexos como servidores e clusters

- Fornece várias ferramentas de teste/simulação/validação: simulação de ISA, simulação funcional QEMU, emulação acelerada com precisão de ciclo e ferramentas para exportar RTL para implementação real de hardware FPGA.

A principal desvantagem do Rocket Chip é o fato de não possuir uma versão Untethered (não ligada), i.e., os SoCs gerados do projeto são conectados a processador que faz o papel da memória principal e bootloader do sistema. Isso faz com que as aplicações que se executam em FPGA tornem-se bastante lentas, por serem gerenciadas por outro processador, impossibilitando o teste e avaliação de desempenho de soluções em FPGAs. Um outro ponto importante, é a necessidade de aprender uma nova HDL, a linguagem Chisel. E que o projeto não possuem periféricos de E/S como I2C, I2S, UART, PWM, etc, necessitando de implementação caso necessário.

No entanto, mesmo com os inconvenientes, o gerador de SoC ainda parece interessante para pesquisa e fins de educação, já que possue uma boa infraestrutura que permite a construção de diferentes configurações de SoCs (de simples Microcontroladores a sistemas multi-processados), além de permitir novas implementações ou modificações da sua gama de componentes e avaliar usando as ferramentas de simulação e emulação. Sobre o problema da versão *Untethered*, ela pode ser solucionada com alguns esforços de programação.

O Rocket Chip <sup>7</sup> foi fabricado onze vezes e produziu protótipos funcionais de silício para executar programas bare-metal, bem como inicializar o Linux. É uma fonte aberta, bem mantida e livre de encargos para implementação e fabricação.

<sup>&</sup>lt;sup>7</sup>Repositório oficial: https://github.com/freechipsproject/rocket-chip

#### 4.5 LowRISC

Figura 15: Logo lowRISC.

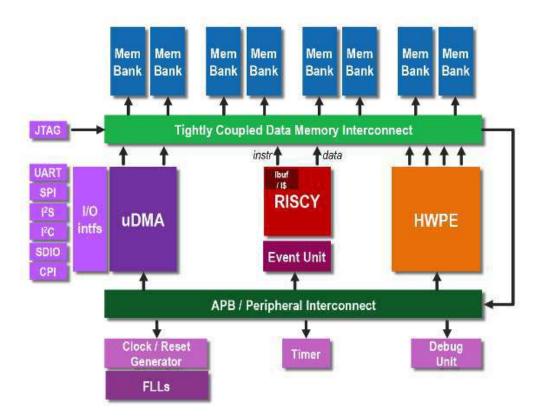

O lowRISC <sup>8</sup> é uma organização sem fins lucrativos que trabalha em estreita colaboração com a University of Cambridge e a comunidade *open-source*. O projeto se baseia principalmente no fluxo de desenvolvimento do Rocket Chip e todas as ferramentas são muito semelhantes, inclusive os processadores usados no lowRISC é o Rocket Core, implementando a extensão RISC-V RV64GC com 5 estágios de pipeline.

O lowRISC suporta personalização, possui um conjunto de periféricos implementados, multi-processamento, entre outros. Apesar de ser derivado do Rocket Chip, os SoCs gerados não são ligados (*Tethered*) a outro processador como no Rocket Chip, permitindo síntese em FPGAs ou ASICs diretamente. O repositório já possui versões de SoC capaz de executar Sistema Operacional Debian e Linux em geral.

O objetivo principal do projeto é construir diferentes plataformas capazes de executar sistemas baseados em Linux com baixo custo de fabricação. Soluções *Ultra-Low Power*, geração de Microcontroladores, entre outros, não são possíveis, o que torna a plataforma pouco flexivel em relação a outras para o ensino de Sistemas Embarcados e como plataforma de pesquisa. Uma visão geral da plataforma é apresentada a seguir.

Figura 16: Arquitetura simplificada lowRISC.

21

<sup>&</sup>lt;sup>8</sup>Site oficial: https://www.lowrisc.org/

# 4.6 OpTiMSoC

Figura 17: Logo OpTiMSoC.

OpTiMSoC  $^9$  - Open Tiled Manycore System-on-Chip. É um framework de código aberto escrita principalmente em Verilog que permite construir System-on-Chips. Fornece blocos como processadores, memórias, aceleradores de hardware, componentes de E/S, entre outros, todos conectados em arquitetura Network-on-Chip  $^{10}$  (NoC). O sistema resultante pode então ser simulado ou sintetizado em FPGA.

O OpTiMSoC oferece os recursos apresentados na Tabela seguinte:

| Recursos          | Descrição                                                          |

|-------------------|--------------------------------------------------------------------|

| Toolchain         | Consiste em um conjunto de ferramentas usado para compilar         |

|                   | programas de software para arquitetura OpenRISC.                   |

| Bibliotecas       | Fornecem todas as funcionalidades das plataformas OpTiMSoC         |

|                   | para os aplicativos. Este inclui drivers de hardware, suporte a    |

|                   | tempo de execução, APIs de comunicação e APIs de gerencia-         |

|                   | mento de tarefas.                                                  |

| Simulação RTL     | É o ponto de partida do desenvolvimento. Além disso, a simulação   |

|                   | RTL é usada para executar pequenos pedaços de software para        |

|                   | teste ou desenvolvimento de drivers e o sistema em tempo de        |

|                   | execução.                                                          |

| Verilator         | Ferramenta de código aberto que transforma código Verilog em       |

|                   | modelos C++ ou SystemC para desenvolvimento de simulações          |

|                   | do sistema.                                                        |

| Síntese           | Atualmente, a equipe do OpTiMSoC se concentra na síntese de        |

|                   | FPGAs. O Xilinx WebPack grátis é suportado, assim como o           |

|                   | Synopsys Synplify, mas a licença ainda é necessária em alguns      |

|                   | casos.                                                             |

| Interface gráfica | Fornece fácil controle e observabilidade dos sistemas em execução. |

Tabela 2: Descrição de recursos OpTiMSoC.

Apesar de ser uma plataforma bastante completa, o objetivo dessa plataforma de pesquisa é o estudo de arquiteturas NoCs.

<sup>&</sup>lt;sup>9</sup>Site oficial: https://www.optimsoc.org/

<sup>&</sup>lt;sup>10</sup>NoCs, de forma simplificada, são topologias de redes de comunicação entre componentes de SoC, que visão melhorar a eficiência de energia em SoCs.

# 4.7 Critério de escolha de plataforma

A decisão sobre qual plataforma escolher para ser utilizada, analisou vários critérios, levando em consideração também os objetivos apresentados na seção 2.2. Os critérios estabelecidos foram:

- 1. Escolher uma plataforma de código aberto *upstream* (disponível para download na Internet) com todos os recursos de hardware e software incluidos, para garantir uma boa acessibilidade e manutenção da plataforma por todos usuários.

- 2. Geração de arquiteturas de SoCs amplamente personalizáveis, i.e., quantidade de processadores, personalização de memória cache, unidades de aceleração (e.g. coprocessadores) periféricos, etc. O intuito é poder explorar o máximo de componentes de um SoC, de forma produtiva.

- 3. Possibilitar geração de Microcontroladores de pequeno porte e sistemas capazes de executar sistemas Linux, o objetivo é fornecer uma plataforma mais genérica possível.

- 4. Possibilitar simulação e síntese das soluções geradas.

- 5. Possuir uma ISA aberta.

O PULP-platform (PULP, PULPino ou PULPissimo) são microcontroladores projetados para alçancar o baixo consumo de energia. Eles são bem mantidos e documentados, mas sua arquitetura não é personalizável e não são projetados para executar sistemas como Linux.

As plataformas Nios II e MicroBlaze, tem os componentes internos do processador fechados, suas ISAs não são de código aberto e algumas ferramentas de análise não abertas.

O OpTiMSoC atende a maior parte desses critérios, mas é relativamente desatualizado (última versão é 2016) e é baseado na arquitetura OpenRISC, que tem muitas limitações em comparação com o ISA RISC-V (Rocket Chip e lowRISC). Estas limitações são apresentadas em detalhes no manual de especificação RISC-V [13], página 15.

Levando em consideração os argumentos mencionados, ficamos apenas com duas opções lowRISC e Rocket Chip. Pesquisas adicionais e experimentos técnicos mostraram que o lowRISC é baseado em uma versão antiga do Rocket Chip, que não é mais mantida/atualizada. Além disso, ambos não são bem documentados, mas a vantagem do Rocket Chip é que o trabalho é mantido, sendo uma referência nas implementações relacionadas ao RISC-V.

Com base nesses critérios e nessa análise, escolheu-se o Rocket Chip SoC generator, sendo a solução que mais se ajusta enquadra com as necessidades do projeto.

# Parte III

# A Plataforma Rocket Chip Generator e suas Ferramentas

# 5 Rocket Chip SoC Generator

Figura 18: Ecossistema do Rocket Chip.

O Rocket Chip é um gerador de System-on-Chip de Código aberto que emite RTL sintetizável. Ele aproveita a linguagem de construção de hardware Chisel para compor uma biblioteca de geradores sofisticados para cores, caches e interconexões em um SoC integrado. O Rocket Chip gera processadores de uso geral que usam a ISA (do inglês, Instruction Set Archictecture) RISC-V e fornece tanto um gerador de processador em ordem (Rocket-Core [14]) quanto um fora de ordem (BOOM). Para projetistas de SoC interessados em usar especialização heterogênea para ganhos adicionais de eficiência, o Rocket Chip suporta a integração de aceleradores personalizados na forma de instrução de extensões, coprocessadores ou cores totalmente independentes.

Em vez de ser uma única instancia de um projeto de SoC, o Rocket Chip é um gerador de SoC, capaz de produzir várias instancias de projeto a partir de uma única fonte de alto nível. A parametrização extensiva torna-o flexível, permitindo a fácil personalização para uma aplicação específica. Ao alterar uma única conFiguração, um usuário pode gerar SoCs que variam em tamanho, desde microcontroladores embutidos até chips de servidores com vários processadores [14].

Em outras palavras, podemos imaginar o Rocket Chip como um grande menu de componentes de um SoC, em que o cliente faz a escolha dos componentes e pode também escolher as características de cada um deles, e no final da respectiva escolha, o SoC é entregue de acordo com as especificações.

O projeto está disponível para download em https://github.com/freechipsproject/rocket-chip. No decorrer do relatório, os repositórios contidos neste projeto serão referenciados, fornecendo uma compreensão prática e teórica da plataforma passo a passo. Devido a atualização constante deste repositório foi fixada uma versão, que pode ser conseguida usando o comando:

```

$ cd rocket-chip

$ git checkout 4ba8acb4aa26901899963136704d065a22e36460 -b branch_name

```

Código 1: Downgrade in Rocket Chip git repository.

# 6 Visão Geral dos Componentes de Hardware

Nesta Seção será apresentada a arquitetura do SoC Rocket Chip, expondo os seus principais componentes, seus barramentos e como tudo se conecta de forma global. Nas próximas subseções, descreveremos esses componentes de uma forma mais detalhada, apresentando também onde encontrar os Códigos de implementação destes componentes e quais são as opções de personalização que cada um oferece.

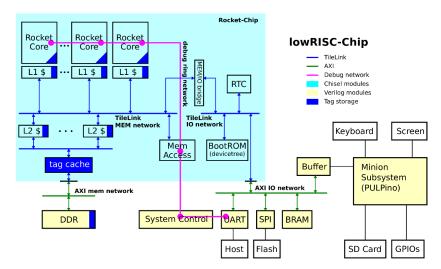

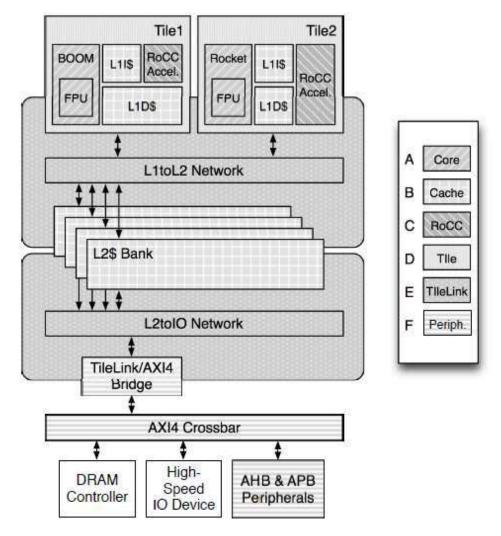

Figura 19: Componentes do SoC Rocket Chip [14].

A arquitetura apresentada na Figura 19 mostra os principais componentes existentes do Rocket Chip e como eles são agrupados e conectados.

O módulo Tile (ou Rocket Tile, letra D na Figura) é um componente que instancia importantes circuitos, como: processador, cache L1, coprocessador (RoCC - Rocket Custom Coprocessor) e FPU. Na Figura acima, o sistema possui dois Tiles, o primeiro (Tile1) possui: processador BOOM, FPU, L1 Cache e RoCC. O segundo Tile (Tile2) é muito semelhante, deferenciado na instancia do processador e nos paramêtros da cache

L1.

Os Tiles são conectados ao barramento TileLink (principal barramento do Rocket Chip), que além de fornecer conectividade entre componentes, implementa o mecanismo de coerência de cache. Esse barramento também possui interface AMBA AXI4 (ou *bridge* TileLink-to-AMBA) e usa isso para conectar outros dispositivos de E/S e memórias, como pode ser observado na Figura.

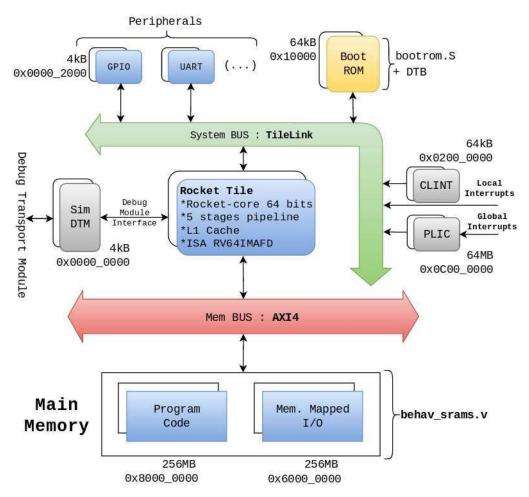

A Figura 20 é outro exemplo de instanciação do Rocket Chip. Nessa arquitetura mais simplificada o sistema possui apenas um Tile, porém evidencia outros componentes de hardware como o Core Local Interruptor (CLINT), que é o controlador de interrupções locais dos processadores, o Platform Level Interrupt Controller (PLIC), responsável pelo controle das interrupções globais, a memória ROM que contém parte do Código do bootloader e o dispositivo I/O SimDTM (Debug Transport Module) responsável pela interface E/S de depuração do sistema.

Figura 20: Visão geral da arquitetura do Rocket Chip.

No geral, o Rocket Chip é uma biblioteca de geradores de hardware (processadores, FPU, barramentos, memórias, etc) que podem ser parametrizados e compostos de diversas formas, possibilitando uma larga variedade de projetos de SoC.